If you want to find a company’s press releases, product details and short biographies of its key personnel, then its website is often very informative. But what you fail to find there are the details of the activities that led to the forming of the company – in fact, sometimes this information is nowhere to be found on the Internet.

That’s the case with IQE, which has just notched up 30 years in the epiwafer supply business. So when I went to interview one of its co-founders, CEO Drew Nelson, I was keen to hear how the venture got off the ground (see p. 20 for the full story).

When I spoke with Nelson, I found out that he met his cofounder, Mike Scott, at events associated with a government sponsored programme called the Joint Opto Electronics Research Scheme (JOERS). There Nelson would present work by BT, Scott would detail the latest successes at Plessey, and while this duo were together they would try to gauge the appetite for a supplier of InP epiwafers for the fibre-optic business. Talking to others in the industry, they knew they were on to a winner – they just had to convince an investor. Eventually they did so, with Shell Ventures, part of the Shell Group, providing funding.

Thirty years on, following a management buyout, a merger, a float on the stock exchange and the acquisition of a handful of other companies, IQE is the biggest epiwafer supplier in the world. It could hardly have gone better.

Judged in terms of compound semiconductor manufacturing in the UK, the company created by Nelson and Scott must be the biggest success right now. After all, in the intervening years, while IQE’s presence in this industry has grown, that of the likes of Plessey and BT has dwindled, despite their strong IP.

This clearly irks Nelson, and is behind his motivation to drive the formation of the world’s first compound semiconductor cluster. Pieces of this jigsaw are falling into place, and one of the most encouraging elements must be interest from overseas. Asian companies, described by Nelson as “fairly significant”, are starting to outsource their manufacture to the cluster.

Growth in this business will be great news for those at IQE. While they celebrate the thirtieth anniversary, they can get as much pleasure thinking about the promise of the future as the triumphs of the past.

After a quiet period due to the saturation of the mobile handset industry, the GaAs wafer market is waking up, according to a new resport by Yole Développement (GaAs Wafer and Epiwafer Market: RF, Photonics, LED and PV Applications report, July 2018). It forecasts a 15 percent CAGR between 2017 and 2023 (in volume), with an impressive 37 percent, especially for photonics applications.

As one of the most mature compound semiconductors, GaAs has been ubiquitous as the building block of power amplifiers in every mobile handset. In 2018, GaAs RF business represents more than 50 percent of the GaAs wafer market. However, market growth has slowed down in the past couple years due to the handset market’s gradual saturation and shrinking die size.

“At Yole, we expect GaAs to remain the mainstream technology for sub-6 GHz instead of CMOS, owing to GaAs’ high power and linearity performance as required by carrier aggregation and MIMO technology,” explains Hong Ling, Technology and Market Analyst at Yole. Since 2017, GaAs wafer has been particularly notable in photonics applications. When Apple introduced its new iPhone X with a 3D sensing function using GaAs-based lasers, it paved the way for a significant boost in the GaAs photonics market. The GaAs wafers market segment for photonics applications should reach $150 million by 2023. “GaAs-based ROY and infrared LED applications have also caught our attention”, asserts Ezgi Dogmus, technology and market analyst at Yole. “We estimate, 2017-2023 CAGR achieves 21 percent (in units) for the total GaAs LED market, surpassing more than half of the GaAs wafer volume by 2023.”

In terms of the wafer and epiwafer businesses, each application requires a different size and quality when determining wafer and epiwafer prices. As a new entrant, photonics applications will impose new specification requirements compared to the well-established RF and LED wafer and epiwafers, creating significant ASP diversity.

From a value chain point of view, the GaAs photonics market’s remarkable growth potential will offer plenty of opportunities for wafer, epiwafer, and MOCVD equipment suppliers, as well as for investors.

Sumitomo Electric, Freiberger Compound Materials, and AXT, involved in GaAs wafer supply, lead the market with about 95 percent of market share collectively. And since new laser applications have very high specification requirements for GaAs wafer that are constantly evolving, Yole analysts’ expect the top players to maintain their technical advantage for at least another 3 - 5 years.

Regarding GaAs epiwafer production, Yole’s analysts identified different business models. The GaAs LED market is principally vertically integrated, with very well-established IDMs like Osram, San’an, Epistar, and Changelight. In parallel, GaAs RF businesses outsource significantly from well-established epihouses.

Within the GaAs photonics market, the epi business is still applicationsdependent. GaAs datacom market segment is mostly epi-integrated, with dominant IDMs like Finisar, Avago, and II-VI. For 3D sensing in smartphones, epi outsourcing is significant. In 2017, Apple’s supplier Lumentum used IQE as its VCSEL epi supplier. This resulted in an almost 10-fold increase in IQE’s stock price. Other leading GaAs epihouses are in qualification or ramping up. Yole expects the photonic epiwafer market to behave similar to the GaAs RF epiwafer market.

Kaiam, a manufacturer of data centre optical transceivers, has initiated a strategic transceiver reserve programme. The strategic reserve is intended to protect US and European data centres from the effects of the incipient US-China trade war.

The Trump administration has recently enacted broad-based tariffs that could impede the importation of Chinesemade optical transceivers into the US. Because US Cloud data centre companies are largely dependent on a supply of Chinese-made transceivers, they are highly vulnerable to collateral damage from the increasingly turbulent US-Chinese relationship. As one of the few remaining US optical transceiver companies, Kaiam is immune to illeffects of US-China trade tensions. Kaiam is building a strategic reserve of transceivers that its customers can draw down in response to a dwindling Chinese transceiver supply. The company will populate this reserve with units fabricated in its UK facility and welcomes partners to add to this reserve.

“In today’s global economy, it’s easy to assume goods will flow seamlessly across borders indefinitely. We sometimes forget that the optical components that power Cloud companies like Google, Facebook, Amazon, and others are virtually all made in China and are thus susceptible to trade tensions. As patriots, we believe a transceiver reserve is necessary for our domestic security,” said Jeremy Dietz, VP of global sales and marketing at Kaiam. “Our advanced technology and manufacturing process allows us to easily build a buffer to protect our nation in case of an embargo or even a natural disaster. We are currently exploring secure underground locations in states such as Utah and Nevada.”

“Our constitution implicitly guarantees the fundamental right to engage in online activities ranging from the sublime to the abject on a 24/7 basis,” said CTO Rob Kalman of Kaiam. “We view it as our patriotic duty to protect these rights, for it is more true than ever that the price of freedom is eternal vigilance!”

The Compound Semiconductor Applications Catapult, Wales’ first and the UK’s newest Catapult has announced that it will open its Innovation Centre, based in South East Wales, in early 2019. The announcement made by Secretary of State for Wales Alun Cairns, also confirmed that the Catapult will receive £51 million of grant funding from the £780 million investment in the UK’s internationally renowned Catapult network announced by the Chancellor Philip Hammond as part of the Government’s industrial strategy. This builds on the £180 million announced by the Prime Minister last month for centres in the North East last month, taking the total of additional funding to almost £1 billion.

The Catapult has already employed 23 people and is set to create around 100 new jobs internally. By 2023 it aims to have helped create 1,000 new hightech jobs within the businesses it has supported around the whole of the UK. With analysts predicting that the world market for compound semiconductors will increase from $66 billion today to over $300 billion by 2030, it is essential that the UK plays a substantial part in that growth and the Catapult is here to help make that happen. Secretary of State for Wales Alun Cairns said: “This investment in the Compound Semiconductor Applications Catapult cements Wales’ reputation as a leader in advanced electronics. Bringing together academics and businesses to develop new technologies will support areas of our daily lives from the next generation 5G mobile network to improving scanning at airport security.

“Our investment in this technology will help Welsh businesses exploit a hugely lucrative global market and ensure that Wales continues to lead the world in science and innovation, creating vital new jobs along the way.”

Compound Semiconductor Applications Catapult CEO, Stephen Doran said: “Our Catapult is a UK-wide centre, based in Wales. With immediate effect, this grant funding will allow the Catapult to create a critical mass of industry-leading expertise at the heart of the world’s first compound semiconductor cluster in South Wales. The transformative potential for compound semiconductors to meet the challenges of the future has never been higher, and our new Innovation Centre will make sure that Wales is at the forefront of this revolution.”

The Catapult Innovation Centre will house a design studio, laboratories and test facilities, supported by simulation and modelling tools and advanced capabilities. It will help companies to accelerate the development of new products using compound semiconductors.

The Compound Semiconductor Applications Catapult has also set out its strategy with the publication of its Launching the Compound Semiconductor Applications Catapult brochure which was developed in collaboration and with input from over 150 companies in the sector. The strategy focuses around three areas: the Catapult’s new Innovation Centre; designing and manufacturing a series of evaluation modules to help companies prototype systems; and running a series of challenge programmes to identify how best compound semiconductors can address global challenges.

The Catapult is actively looking to fill positions across all levels of the organisation and in particular its three technology areas: Power Electronics, Photonics and Microwave and RF. Working with the Catapult can provide the opportunity to contribute and shape a business in its early stages with the stability of secured funding within which to operate. The Catapult has a collaborative, supportive and inclusive culture which will be reflected in its Innovation Centre where agile workspaces and settings for different types of working behaviour are part of its DNA. The Catapult has the benefit of a fast-moving entrepreneurial culture and a strong financial footing.

Network firm Infinera has announced its intent to acquire Coriant, a privately owned network company, to create one of the world’s largest optical network equipment providers.

The combination positions Infinera to capitalise on the next wave of global network spending as network operators transform their networks to transition from 4G to 5G, from Optical Transport Network (OTN) to packet and from closed to open network architectures. Infinera’s vertically integrated business model provides the ability to unleash value for customers and investors as the company’s combined network solutions power the world’s largest network operators. Ovum forecasts optical network spending to reach $17.8 billion in 2022. Under the terms of the definitive purchase agreement governing the acquisition, subject to customary adjustments, Infinera will pay approximately $150 million in cash at closing, and estimated additional amounts of $25 million in the two quarters post-closing and $55 million over a period of years. Infinera will issue approximately 21 million shares, which when combined with the cash consideration, results in total transaction consideration of approximately $430 million.

“Acquiring Coriant is a fantastic opportunity, strengthening our ability to serve the world’s largest network operators, accelerating our ability to leverage vertical integration and reinforcing our commitment to our long-term business model,” said Tom Fallon, Infinera CEO. “This powerful combination immediately benefits our combined customers by delivering the innovative technology required for the next wave of network spending.”

The acquisition is expected to be substantially accretive in 2019. This accretion will come from $100 million of identified cost savings in both cost of goods sold and operating expenses. Total cost synergies of $250 million are expected through 2021, with the continuation of operating synergies and the introduction of vertical integration into the Coriant product line, resulting in a step-function increase in Coriant’s margins. Infinera will be acquiring a debt-free balance sheet and expects cash flows to pay back transaction consideration within three years.

Coriant invested nearly $1 billion in research and development over the last five years to significantly advance its portfolio to address the growing demand for software automation and open, disaggregated platforms. Infinera recently upgraded its portfolio based on the innovative Infinite Capacity Engine (ICE4). Combining the strengths of both companies creates a powerful new portfolio to support our customers’ transition from 4G to 5G, from OTN to packet and from closed to open network architectures.

Confident in the combined company’s opportunities, Coriant’s majority owner, Oaktree Capital Management, expressed an interest in being compensated for this transaction largely in stock. Post-transaction, Oaktree will own approximately 12 percent of the combined company on a fully diluted basis. Pursuant to the terms of the definitive purchase agreement, Oaktree has agreed to lock up 50 percent of its shares for six months post-close and the remaining 50 percent of its shares for 12 months post-close. To fund the cash requirements of this transaction, and to support future working capital requirements, Infinera plans to pursue debt financing. Morgan Stanley Senior Funding has committed to provide debt financing for the transaction, subject to customary conditions.

The acquisition is expected to close in the third quarter of 2018, subject to customary closing conditions. The board of directors of Infinera has unanimously approved the transaction. Morgan Stanley & Co. LLC served as financial advisor and Wilson Sonsini Goodrich & Rosati, PC served as legal counsel to Infinera on this transaction. Moelis & Company served as financial advisor and Kirkland & Ellis served as legal counsel to Coriant.

Industry analyst firm N-tech Research has just published a new report titled Micro-LED Market Opportunities: 2018-2027 that forecasts the global micro-LED market will grow from $2.7 billion in revenues in 2019 to $10.7 billion in 2022.

N-tech believes micro-LED technology is making substantial advances, which will produce substantial opportunities in the coming years from applications such as near-eye AR/VR projectors and automotive head-up displays which require a combination of small form factor, low weight, super-high resolution and super-high brightness. The smart watch market is another opportunity for micro-LEDs. Here, the combination of extremely low power consumption and very strong brightness make micro-LEDs an obvious choice for wearable displays. N-tech sees this segment as generating $1.6 billion in 2022. Growth is also expected in extralarge displays. Such displays are used in video walls, digital cinemas, digital signage and home theatres, where N-tech believes they will greatly benefit from the scalability of micro-LED technology to large areas (already demonstrated by Sony and Samsung). Micro-LEDs also offer the ‘giant screen’ sector the possibility of hybridisation with other functionalities, and compatibility with flexible and transparent display designs.

Micro-LEDs are not for everyone. N-tech believes that there are still applications where micro-LEDs will struggle to make inroads. These include smartphones, tablets and regular TV market, where LCD and OLED technologies will continue to do well. Benefits from micro-LEDs are not as apparent in these markets although low power consumption could be something of a selling feature for tablets and smart phones.

The Poweramerica Institute at North Carolina (NC) State University, a member of Manufacturing USA, has awarded funding to six new member projects that will enhance wide bandgap technologies in the US. In addition, PowerAmerica has awarded funding for 20 projects to be led by existing members for a total of $20 million in project funding for this cycle. The new member projects receiving funding are:

Wide bandgap power modules for next generation systems

GE Aviation Systems and National Renewable Energy Laboratory (NREL) will work together to design and produce advanced wide bandgap power modules made with SiC and GaN. The goal of this project is to enable true engine coolant temperature-grade equipment which is required to support next generation defence systems as well as commercial transportation, wind and solar, while reducing overall system costs.

Dual-inductor hybrid converter for direct 48V to sub-1V DC-DC module

A team at UC Boulder will design and implement a GaN-based, novel converter with an increased density of ten times that of converters currently on the market, with up to three times lower power loss. The converter will have fewer components, simpler implementation and lower cost. It can be used for power delivery to data centres, cellular base stations, portable applications, and defence systems.

Devices for solid-state circuit breaking at the medium voltage level

A team at the University of North Carolina, Charlotte (UNCC) will test a functioning prototype of a medium voltage (3.3 kv) SiC solid-state circuit breaker. The use of SiC in the product will enable fast turn-off capability in the microsecond range or better, and superior efficiency compared to silicon. Market segments to be targeted include utility operators of the electricity distribution network.

600V GaN bi-directional switch

Infineon will develop a low-cost, 600V bidirectional 70 mΩ switch based on the company’s CoolGaN HEMT technology, capitalising on the unique bidirectional nature of the GaN HEMT. The project will validate both the dual gate concept and a solution for substrate voltage stabilization, and will make the GaN switch more economically attractive compared to the standard silicon devices commonly used today.

Graduate wide bandgap semiconductor power device lab

A team at NCSU will establish a graduate laboratory course focused entirely on the design, fabrication, and characterisation of wide bandgap power devices, and disseminate the curriculum to PowerAmerica members to accelerate the education of new engineers.

Power electronics teaching lab incorporating wide bandgap switches and circuits

Researchers at UNCC will develop a modular, multi-function, educational highfrequency power electronics board with plug and play capability. The new board will give students the flexibility to perform different power electronics lab sessions and train undergraduate students as wide bandgap power electronics engineers through hands-on experience and practical knowledge of WBG semiconductors in power electronics applications.

PowerAmerica aims to save energy and create US manufacturing jobs by accelerating the development and large-scale adoption of wide bandgap semiconductor technology made with SiC and GaN in power electronics systems. The institute, located at North Carolina State University in Raleigh, NC, is funded by the Department of Energy, industry partners and the state of North Carolina, and has a member portfolio representing more than 45 companies in the wide bandgap semiconductor field.

France-based GaN-on-silicon device pioneer Exagan has delivered transistors and switching ICs for pocket-sized fast chargers

As the dust settles on this year’s PCIM Europe, myriad power electronics companies are taking home a vast array of GaN-based devices.

For example, GaN Systems showcased 100 V and 650 V GaN E-HEMTs, Transphorm unveiled 650 V GaN FETs while EPC demonstrated its low-voltage enhanced-mode GaN FETs, targeting automotive, power supply and data centre applications, and more.

At the same time, France-based Exagan, also a key power electronics player, launched its 650 V G-FET power transistor alongside an integrated driver and transistor switching system, G-DRIVE, aimed at fast charger markets.

Described as being easy to design into electronic systems, the products are compliant with the USB power delivery 3.0 type C standard. And as Exagan president and chief executive, Frédéric Dupont, puts it: “The market potential here is enormous, including portable electronic devices as well as homes, restaurants, hotels, airports, automobiles and more.”

“In the near future, users will be able to quickly charge their devices by plugging a standard USB cable into a small, generic mobile charger,” he adds.

Since spinning out of CEA-Leti and Soitec in 2014, Exagan has firmly focused on developing 650 V GaN-on-silicon products for photovoltaic, automotive and PC markets and more. So why focus on the charging market right now?

According to Dupont, silicon power devices simply cannot fulfil fast charging applications, opening the door to GaN-based systems. But moreover, the chief executive reckons his company can deliver more intelligent and cost-effective GaN device solutions for this application.

“This is a place where GaN can really have a play, but the challenge is the cost and providing a complete solution – this is why you won’t see many GaN players addressing this segment,” he says. “However, Exagan can bring a lot of value here in the short-term.”

Indeed, thanks to a rich heritage of heteroepitaxy development from France-based CNRS-CRHEA, CEALeti, and Soitec, Exagan has been ahead of the pack on production, and consequent costs, from word go.

During processing, a stack of buffer, insulating and strain management layers is deposited between the silicon substrate and GaN epilayers to relieve crystal stresses and prevent cracking.

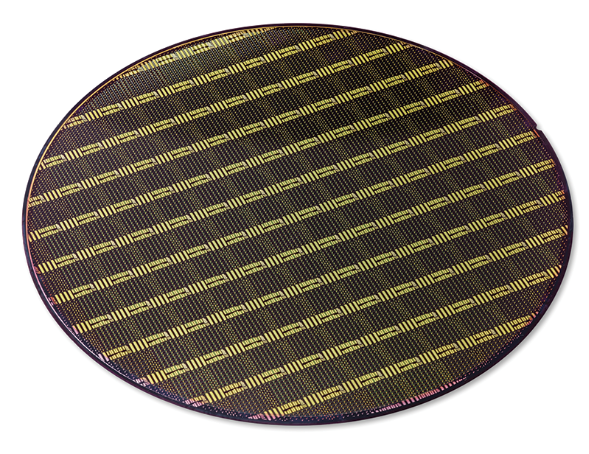

As a result, Exagan has been able to take GaN-onsilicon FET fabrication to larger wafer sizes, focusing on 200 mm production at X-Fab’s CMOS foundry in Germany, as many other GaN players grapple with smaller, 150 mm wafer sizes.

“Most companies are at six inches today but we have been working at eight inch, which is a good size for GaN,” points out Dupont. “This is important for costs, as most of the silicon power electronics market is currently being manufactured at eight inch... and we are using the same 200 mm CMOS infrastructure and equipment.”

“In the future we will see some silicon power devices moving to twelve inches but we think GaN will stick with eight inches,” he adds. “I don’t want to say forever but certainly for a long time as the cost structure is already very competitive.”

Costs aside, Dupont is also certain that GaN-based systems are ideal for fast-charging applications. As he points out, heteroepitaxial devices, such as GaN-onsilicon FETs, are fabricated as lateral devices.

“Compared to vertical SiC devices, these transistors are suited to integration and co-packaging,” he says. “So while SiC devices are very suitable for high current and high power applications, GaN is a good choice for fast charging applications and, indeed, any application that can benefit from system in package integration.”

“We have always believed that GaN should be approached as a system solution, rather than a transistor solution, this is why we are offering our intelligent GaN Power solutions to the market” he adds.

And for the future, Dupont says Exagan will be focusing on co-packaging silicon driver ICs with GaN transistors to achieve the best combination of cost, performance and functionality, rather than integrating the driver electronics onto the GaN transistor chip to produce a monolithic IC.

“Customers want to have a whole solution, not just a transistor,” says Dupont. “And they also want to know how to drive it, how to control it, how to design a transformer and so on.”

“We have to make sure our products have what a designer needs for a particular application... and many customers want to use an external silicon driver, this is why we developed the G-FET,” he adds. “Meanwhile, some customers and applications need a more integrated solution, and this is offered with G-DRIVE.”

Right now, Exagan is sampling and finalizing application development of G-FET and G-DRIVE products with its customers and will ramp production with foundry partner X-Fab according to demand. The company is also working with TÜV NORD’s aerospace and electronics arm, HIREX Engineering, on device testing and qualification in a range of applications.

“The power electronics industry has been very conservative about new technologies, but wide bandgap materials – both SiC and GaN – are revolutionizing this space,” says Dupont. “I do hope in a few years you will have a small GaN-based charger in your wallet, that can charge your phone, laptop, and anything you want to charge.”

Exagan chief executive, Frédéric Dupont, believes the fastcharger market holds massive potential for GaN FETs and systems.

GT Advanced Technologies opens a crystal growth facility to meet imminent silicon carbide market boom, reports Rebecca Pool

In June this year, US-based GT Advanced Technologies, opened a state-of-the-art SiC manufacturing plant in Hudson, New Hampshire.

Equipment, including crystal furnaces, has been shipped over from the company’s former Merrimack facility, sold in December 2016. And as GTAT chief executive, Greg Knight, puts it: “Merrimack was designed for a very different business so we’re now at Hudson, which has been designed from the ground up for this business.”

“The facility is designed to be north of 100,000 square feet of crystal growth production,” he adds. “The first batch of furnaces are already installed and are producing crystal. In the past we have installed thousands and thousands of furnaces so this is very much a known entity for us and we intend to ramp production very quickly.”

GTAT has been producing crystal-growth equipment for the photovoltaics industry, as well as honing SiC boule production, for several years. Emerging from bankruptcy following a disastrous sapphire furnace supply contract with Apple in 2014, the company set out to establish a stable, high-yield robust 6-inch process for SiC boules for photovoltaic, electric vehicle, data centre markets and more.

The current process includes the company’s ‘SiClone’ SiC sublimation furnace and full SiC seeds, and Knight is confident the resulting six-inch boules compete with 4-inch versions on quality. What’s more, the chief executive is certain his company and process is ready for a SiC device market that is poised to explode.

“We believe that the demand for silicon carbide will truly start to accelerate around 2021 to 2022, so in my mind, now is the time to enter the market,” he says. “The market is still far from this inflexion point, when you see volumes ramping, but we are entering at scale and will add incrementally as utilisation rises.”

“We can respond very quickly to utilisation, which is important as you don’t want to outpace yourself and end up with a factory that’s say, 30 percent utilised,” he adds. “But we will be able to be a major player as the market gets through the inflexion point and reaches true volumes.”

Crucially, Knight hopes to soon establish a robust supply chain for SiC markets, providing low-cost, highly repeatable crystal growth equipment that can be easily scaled with a ‘fairly low’ capital outlay. He is confident that GTAT’s experience in crystal growth processes and furnace production, combined with managing supply chains, gives it a competitive edge in meeting the growing demand for wide bandgap semiconductors.

At the same time, however, Knight also wants to ensure GTAT doesn’t compete with its customers.

As he puts it: “One of the largest problems in the silicon carbide industry today is that the substrate providers are also the main competitors to their customers.... and we don’t think this is a long-term strategy that is particularly healthy for the industry.”

Given this, GTAT will grow the SiC crystal and then sell it to vertically integrated customers that can fabricate wafers and devices. “We’re also aligning with strategic partners, which include the pure play wafer manufacturers that will also take our crystal and fabricate epi-ready wafers that can be distributed into the market,” he adds.

6-inch production

Right now, GTAT manufactures 6-inch silicon carbide materials, but as Knight points out, the company is ready to transition to 8-inch production when volumes demand the larger wafer size. Importantly, the chief executive reckons the new facility is ready and can make this leap without any additional capital outlay.

“Fabs in Asia, including China, are focused on four-inch wafer sizes while European and US fabs are working with six-inch wafers, and are looking towards eight-inch sizes,” says Knight. “Such high-end fabs are running on eight-inch silicon and larger, and are currently using their equipment on a downsized six-process, so moving to eight-inch wafer sizes will not require new capital for most of the Western fabs.”

Importantly, as part of its roadmap, GTAT will also focus on reducing costs. Right now, the selling price of a 6-inch SiC wafer comes in at between $1200 and $1500, but Knight reckons these figures will drop to $1000 in the near future.

“Our costs can bring [today’s] selling price down significantly and we believe that in a few years we will have the crystal component cost of a wafer – not including additional process steps – to below $300,” he says. “We really have to get the epi-ready wafer costs down to a point where you can get mass adoption into the end markets.”

The roll-out of 5G will draw on advances in RF and optical semiconductor technologies, basestation system architectures and network topologies by Tony Fischetti from Macom

Much has been written about the impending global roll-out of 5G wireless infrastructure. This is expected to have a transformative impact on everything from mobile device connectivity and fixed-wireless services to transportation, industrial and entertainment applications and beyond. By combining data rates that could be ten to a hundred times faster than those of today with the capacity to handle untold data traffic volumes, the global 5G network is anticipated to provide connectivity that is almost instantaneous, alongside a seemingly limitless bandwidth elasticity that will encompass people, autonomous vehicles, IoT devices, industrial systems and civil infrastructure.

Before large scale deployment of 5G can begin, daunting technology and regulatory issues will have to be resolved. These challenges have an upside, however – they present a tremendous opportunity for operators to evolve network infrastructure in a sustainable manner that enables continuous improvements in bandwidth, power, management and cost efficiencies, amid an ever-intensifying data deluge. Consequently, the advent of 5G invites a fresh, top-to-bottom look at global communications infrastructure, from RF and optical chips to base station system architectures and network topologies.

It is certainly no coincidence that the efforts at developing 5G are paralleling an evolution in civil radar, which is used for air traffic control and weather surveillance. Efforts at streamlining and improving radar infrastructure are informing commercial 5G technology and deployment strategies. That’s not surprising, given that the end goals of these civil and commercial initiatives are similar: the creation of a scalable, cost-effective and highly integrated antenna technology that enables faster, more accurate and more sensitive transmit and receive capabilities. For civil radar, this ensures an expanded field of ‘view’ to aircraft and weather systems, while for 5G, it increases subscriber coverage.

In the US, both efforts are supported by government sponsored, cross-agency planning and coordination.

The aim is to consolidate national radar infrastructure into a single multifunction platform, while freeing up valuable radio spectrum for reallocation to commercial 5G wireless services. This programme, known as Spectrum Efficient National Surveillance Radar (SENSR), brings together the Federal Aviation Administration (FAA), the National Oceanic and Atmospheric Administration (NOAA), the Department of Defense (DoD), and the Department of Homeland Security (DHS).

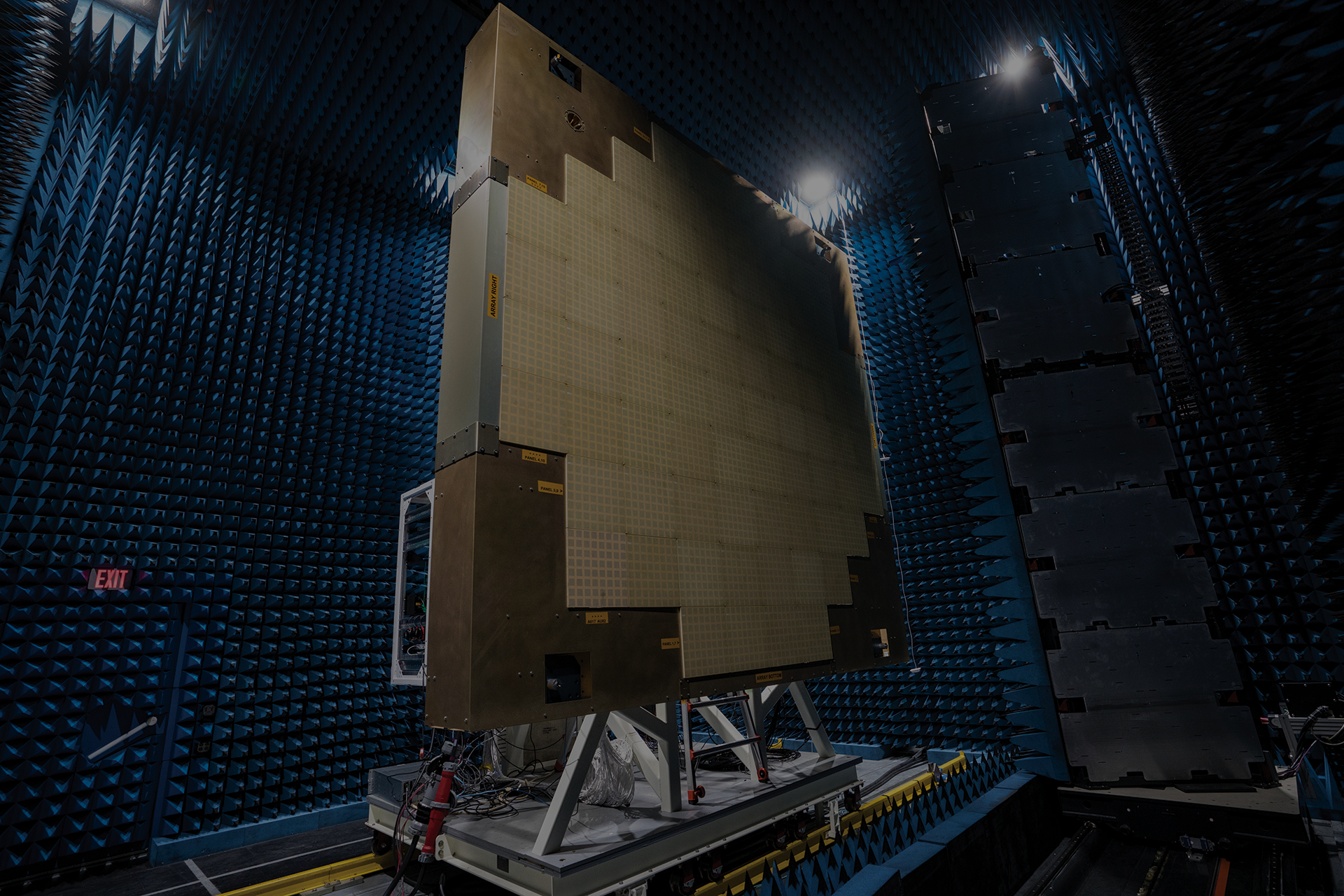

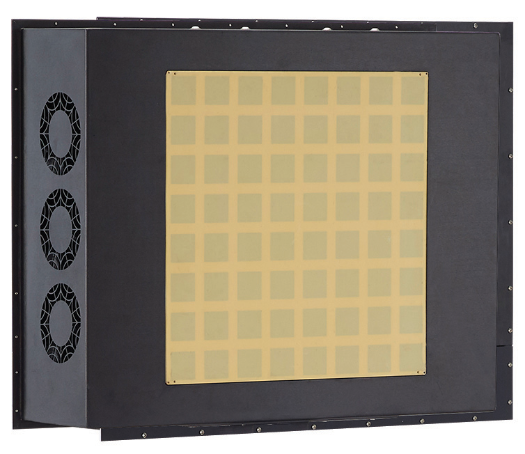

MACOM Scalable Planar Array (SPAR) Tiles

Drawing on civil radar

One of the recent developments in radar antenna has been the introduction of tile-based, planar phased-array radar for air traffic control and weather tracking applications. This breakthrough provides a compelling template for the architecture and assembly of massive MIMO (multiple-input, multiple-output) 5G systems. Drawing on the highly-integrated antenna sub-systems, and volume-scale commercial packaging and manufacturing techniques, will allow those associated with the roll-out of 5G to take little time in building planar arrays that can be flexibly tailored and scaled for deployment across a wide range of environments. And this will be at one-fifth of the cost of that for conventional array architectures, as demonstrated by the first-generation of Scalable Planar Array (SPAR) Tiles targeted for civil applications.

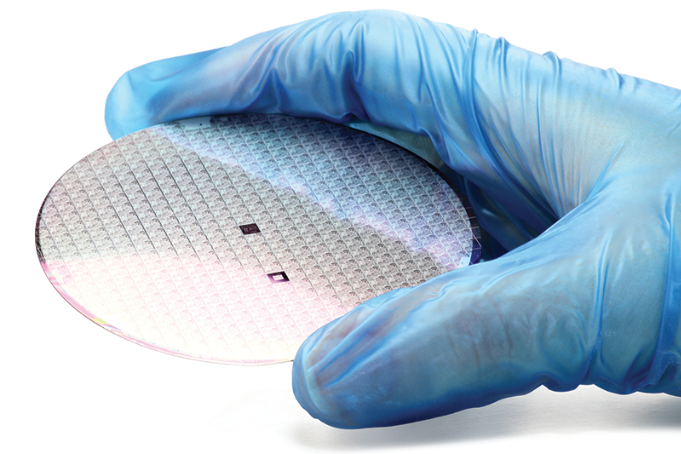

A MACOM 8-inch silicon wafer provides cost efficiencies at scaled volume production

A downside of the current generation of conventional, mechanically-steered air traffic control radars is the slow revisit rates, due to gimbal axis rotation. Planar phased array radars address this weakness with electronic scanning via stationary arrays comprised of hundreds to thousands of transmit and receive elements. What’s more, planar arrays are readily equipped to track weather patterns and unmanned aircraft systems, in addition to conventional aircraft. Thanks to this universality, numerous radar functions are integrated into a single, cost-effective multifunction platform.

It is expected that 5G massive-MIMO antennas will adopt a similar architecture to their radar-based cousins. That means that the number of transmit and receive elements will expand well beyond the two to eight antennas found in current MIMO configurations, and extend to anywhere from 64 to hundreds of antennas.

Similarities between planar air-traffic control radar arrays and 5G basestations don’t stop at the antenna architecture layer. Both feature a coherent beam forming capability, whereby each transmit and receive element in a massive-MIMO array operates in concert with others. This is highly beneficial, dynamically increasing transmitted power and receiver sensitivity in the direction of subscribers, while mitigating noise, interference and reflections from other sources. In densely populated areas, this approach overcomes bandwidth and capacity limitations, while mitigating multipath problems.

Another virtue of coherent beam forming massive-MIMO is that, by leveraging digital phased arrays, it can outperform traditional fixed-beam massive-MIMO architectures in terms of latency, wide band performance and the use of multiband antennas. The upshot is a superior spectral efficiency, which holds the key to wider coverage areas and a higher quality of service for a greater number of subscribers, at a lower cost of implementation.

Advances in GaN and MMICs

It is not just the evolution in basestation architectures and beam forming techniques that is aiding the deployment of 5G infrastructure. There are also improvements in semiconductor and packaging technologies that are offering compelling advantages over legacy approaches.

For massive MIMO, antenna configurations have to be tightly clustered, creating a need to preserve available PCB space, particularly at higher frequencies. One way to address these constraints is to switch from 5G basestation designs that use discrete ICs and single function MMICs to those that employ multifunction MMICs.

In addition to the space saving advantages provided by multifunction integration, costs can be trimmed by reducing individual die packaging, design complexity, testing and assembly labour. Meanwhile, reductions to the number of interfaces can increase overall mechanical reliability.

With all these factors at play, mainstream adoption of GaN-on-silicon is coming at just the right time. Thanks to scalability to 8-inch and 12-inch wafers, this technology is poised to provide cost efficiencies that are well out of reach for GaN-on-SiC at scaled volume production levels, while delivering performance metrics that can’t be achieved with LDMOS.

The superiority over LDMOS is significant – power efficiency is more than 70 percent higher, power per unit area is higher by a factor of four to six, and there is scalability to higher frequencies. In parallel, comprehensive testing data has affirmed the capability of GaN-on-silicon devices to conform to stringent reliability requirements, and to replicate and even exceed the RF performance and reliability of rivals made from GaN-on-SiC.

Where GaN-on-silicon clearly has the upper hand over GaN-on-SiC is in its potential to integrate increased functionality at the silicon level. This yields additional space optimization, leading to ultra-compact MMICs; and it enables the homogeneous integration of GaN devices and CMOS-based devices on a single chip. The latter opens the door to multifunction, digitally assisted RF MMICs that incorporate on-chip digital control and calibration, on-chip power distribution networks, and more.

Superior switches

RF switches – either in the form of discrete components or front-end modules, where they are integrated with LNAs and controllers – will play a pivotal role in 5G wireless basestation performance. There are a wide variety of underlying semiconductor technologies to select from, and designers need to select the best semiconductor junction for the required system function, while keeping an eye on conserving valuable real estate and minimising power loss and associated costs. Insertion loss is a critical performance metric: every tenth of a dB gained in insertion loss performance translates to extended range and expanded subscriber coverage.

For front-end transmit/receive topologies in highpower 5G antennas, extremely low insertion loss can be realised with AlGaAs and heterolithic microwave IC (HMIC)-based switch technologies. Supporting high-frequency operation to enable wider bandwidths, these technologies may help to maximize received sensitivity and antenna coverage while maintaining transmit/receive signal integrity. In addition, by lowering power loss, these technologies may lead to less compensation further down the RF signal chain.

To give an example of these benefits, a discrete heterojunction AlGaAs p-i-n diode switch can halve the high-frequency insertion loss compared to other switches in its class. This advantage translates to a more reliable system performance at higher frequency bands.

Optical opportunities

To handle the massive increases in network data traffic that lie ahead, emerging 5G network architectures are expected to rely more heavily on high-speed optical interconnects from the network backbone through to baseband processing, and on to the antenna. This architecture, which we refer to as fibre-to-the-antenna, reduces copper cabling as new fibre deployments push deeper into the network.

Wireless fronthaul is a prime example of how innovations in optical semiconductor and packaging technologies – at optimal cost structures – have the potential to transform today’s wireless network topologies, which could extend from remote radio units to baseband units.

We anticipate new 100 Gbit/s, single-wavelength PAM-4 DSPs and advanced silicon photonics technologies to provide high-performance, cost effective 100G optical interconnects for centralized/cloud radio access network architectures. This will greatly simplify the design and maintenance of remote radio units, with processing intelligence moving to a centrally managed, maintained, and cooled baseband unit, which services a multitude of remote radio units over long distances.

Previously, the common public radio interface protocol enabled a streamlining of centralized/cloud radio access network architectures, but data delivery speeds fell short of the mark. Bridging this gap is 100G connectivity in cloud data centres, a move that has resulted in a reduction in 100G cost structures. Wireless operators are now well positioned to exploit the speed and cost efficiencies of 100G interconnects for wireless fronthaul in preparation for the 5G data deluge, while enabling a flexible centralized/cloud radio access network architecture designed for seamless scalability into the future.

The parallel advances in RF and optical semiconductor technologies, basestation system architectures and network topologies are converging to propel the wireless networking industry toward the realization of more elegant, integrated and cost effective wireless infrastructure on the path to 5G connectivity. Drawing on innovative technologies honed in the civil and commercial technology domains, system designers and network architects are well equipped to realise higher levels of functionality, performance and device integration for 5G network infrastructure while streamlining data flows throughout the network, from core to antenna.

Back in 1988, Drew Nelson fulfilled a long-held dream by launching his own company. Thirty years on, it could have hardly turned out better: IQE is the world’s biggest epiwafer supplier, with facilities on all three major continents; and it’s the driving force behind the creation of the world’s first compound semiconductor cluster Richard Stevenson reports

At the beginning of 1980s, companies making InP chips for the fibre-optic industry had a broad range of expertise. Their skillsets included the design of the device, its testing, and its production – including the most challenging aspect of all, the epitaxial growth of the heterostructure.

But in 1988, this situation changed irrevocably. From then on, those chipmakers could choose between adopting a vertically integrated approach, or outsourcing epitaxial growth to a new start-up. Now known as IQE, this epitaxial specialist launched under the name Epitaxial Products International (EPI), reflecting its desire to serve a global industry.

Over the last thirty years the company has increased in size, to have manufacturing facilities on all three major continents; and it has expanded its portfolio, by diversifying its range of epiwafers, and adding substrates and material technologies to the mix. What’s more, it has become the driving force behind the development in the world’s first compound semiconductor cluster, which is making much headway in South Wales.

At the helm of the company since its formation is its co-founder Drew Nelson. After gaining a doctorate at Sheffield University – where he developed microwave devices, grown by LPE and MOCVD – in 1981 he joined British Telecom, where he led a group developing epitaxial technologies for detectors, lasers and modulators. But that was never going to be his long-term career – he had always wanted to run his own company.

The spark for fulfilling this dream came through his involvement in the Joint Opto Electronic Research Scheme, an initiative sponsored by the UK government. This programme, which focused on developing the technology for optoelectronic applications such as fibre-optic networks, brought many of the nation’s biggest technology companies, such as BT, Plessey, GEC and STC, together with several smaller organisations and universities.

Through JOERS, Nelson met Mike Scott, who shared his vision for launching a supplier of epiwafers. “We gauged the level of appetite, and we were encouraged to set up the business,” says Nelson.

Nelson had no intention of going to his bosses, to see if BT would fund this venture: “It definitely wasn’t the right culture.” Instead, he crafted a business plan with Scott and tried to secure backing from venture capitalists. “It wasn’t easy at times, but eventually we were put in touch with Shell Ventures.”

This introduction led to funding from Shell Ventures, a part of the Shell Group that had been created following encouragement by the then Prime Minister, Margaret Thatcher.“

She basically said to them, you’ve gained a huge amount of revenue from North Sea oil, and you should plough some of that back into British technology. We ended up being their keyhole on the semiconductor industry.”

Coming to Cardiff

Backed by “a couple of million pounds”, Nelson and Scott decided to build their facility on a brown-field site on the outskirts of the Welsh capital, Cardiff.

“The Welsh Development Agency were the premier agency in the UK industry for attracting inward investment, and we were able to get some capital grants to help the company,” says Nelson.

That wasn’t the only benefit of this particular location, however: the Electronic Engineering Department at Cardiff University had tremendous expertise in building and testing lasers. “We thought that would be a good source of skilled labour and engineers.”

Once the fab had been built, it was kitted out with equipment to grow and characterise epiwafers. While MOCVD tools were by no means as advanced as they are today, at least they didn’t have to be home built.

“We could have systems built for us, to our very specific designs, which we did,” recollects Nelson. “So we started with one MOCVD system from Thomas Swan, and one MOCVD system from CVT.”

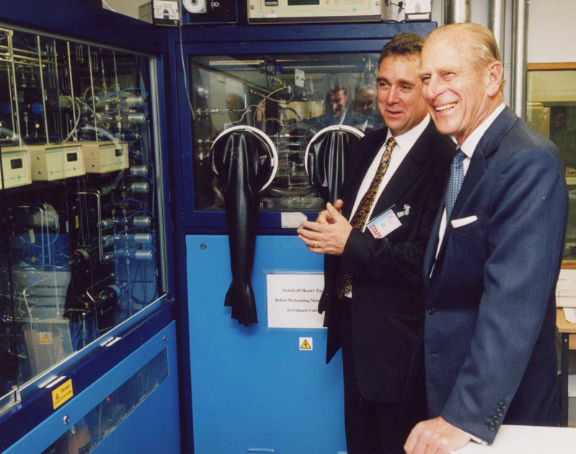

His Royal Highness, the Duke of Edinburgh (right), unveils a plaque to mark the opening of the extension to IQE’s St Mellon’s facility.

Substrates were sourced from AXT, and some suppliers in Japan. “Two-inch substrates were the norm, and even at BT we had been using even smaller substrates than that,” says Nelson. One of the benefits of the JOERCs initiative is that it helped to create a UK manufacturer of metal-organic source materials, Epichem. EPI used this supplier, which had commercialised some of the technology developed at Queen Mary University of London.

IQE CEO Drew Nelson shows His Royal Highness, the Duke of Edinburgh an MOCVD reactor during a visit at the start of the millennium.

To characterise the epiwafers, Nelson and Scott invested in microscopes to assess morphology; X-ray diffraction tools to determine crystallinity; and an electrochemical capacitance-voltage tool, known as a post-office profiler, to determine the doping levels in the epilayers. A home-built photoluminescence kit enabled the evaluation of the optical properties of the epiwafers.

As the facility took shape, Nelson and Scott started to put a team together, while securing their first orders. “I looked after the technology and production side of things, and Mike was more focused on sales,” explains Nelson.

Winning the first orders is never easy, particularly if the business is global. For EPI, they needed to target companies in Japan, as many of them were at the forefront of InP optoelectronics. To this end, EPI employed a local agency. This move paid dividends, with good sales obtained through them adding to successes in the US and Europe.

Initially, EPI only produced material for optoelectronic applications – principally detectors, modulators and lasers. But it did not take long before the portfolio broadened, first with the addition of InP for microwave systems, and then a family of GaAs products: initially lasers, then HBTs and pHEMTs.

These new products gave the industry a broader choice of suppliers of GaAs epiwafers. EPI now offered an alternative to: the French start-up PicoGiga, which had been offering merchant epi since 1983, and specialised in GaAs pHEMTs for direct broadcast TV; and to Quantum Epitaxial Designs (QED) of Bethlehem, PA, that started producing GaAs pHEMT and MESFET epiwafers in 1989.

EPI grew quite quickly throughout the early 1990s, while broadening its product base. “We ended up getting some pretty big contracts, and companies,” remarks Nelson. “We were recognised as the expert company for InP-based materials.”

As epiwafer sales blossomed, fortunes for the company’s backer, Shell, declined. All the big oil companies that had diversified in the 1980s went through a lean patch, leading them to focus on their core business. This led to a management buy-out of EPI, funded by a bank loan and company cash.

Rising sales continued through the 1990s, and by the end of the decade EPI needed to expand its capacity to fulfil demand. “The route to that was a stock market listing,” explains Nelson. “We also wanted to make sure that we were capturing as much of the wireless market that was emerging. So we negotiated a deal to join forces with Pennsylvania based QED.”

Floating in the summer of 1999 at $12.50 per share on the EASDAQ, the European version of NASDAQ, the new venture raised $70 million. This provided much needed funds for capital equipment for the Cardiff and Bethlehem facilities.

The new entity needed a new name. To come up with one, management quizzed staff for ideas by running a competition. The winning entry came from putting EPI and QED together, and taking letters three, four and five: IQE.

Nelson says that the merger was one of “roughly equals”. However, EPI owned 55 percent of the shares, and with IQE listed in London, it made sense to have the headquarters in Cardiff. Due to this, IQE’s core of the management team were those that had led EPI.

At the turn of the millennium, sales were flourishing, with the company continuing its drive to expand its business. It bought UK substrate supplier Wafer Technology, and set up a new facility, IQE Silicon. Situated right next to its Cardiff fab, this arm focused on the growth of silicon and SiGe.

Bursting the bubble

Good times rarely last forever. And they didn’t at IQE. Rising revenue had been fuelled by the rapid growth of the fibre optic industry, and when this went into rapid decline – associated with the well-documented bursting of the dot.com bubble – sales of InP wafers plummeted from around £3 million per month to just £300,000.

“We had to lay off a lot of staff,” remarks Nelson. “It’s always painful to lay off staff when you have recruited and trained them. But we did everything we needed to survive.”

In these tough times, IQE started to lay the foundations for the success that followed. Valuations for all III-V firms had fallen massively from giddy heights, and the time was ripe for further acquisition.

In 2006, IQE acquired the epi business of Emcore; the following year it bought MBE Technologies of Singapore; and in 2012 it acquired the epi business of RFMD.

“We ended up being consolidators of the industry,” says Nelson. “That gave us scale, which was critical, and gave us the biggest customers in the industry.” These customers were confident in working with IQE, because they knew it would be a long-term deal; and they valued the multi-site manufacturing, as this mitigates risk. From IQE’s perspective, more facilities enabled higher volumes, and greater purchasing power with its suppliers.

Further acquisitions and investments have broadened the portfolio. In 2009, the buying of NanoGaN of Bath, UK, added technology for realising high-quality GaN; purchasing Galaxy Semiconductor of Spokane, WA, in 2010, equipped IQE with capability in antimony substrates and infra-red technology; the investment in 2012 in Solar Junction strengthened IQE’s expertise multi-junction solar cells; and this year’s acquisition of Translucent’s technology has provided a capability in crystalline rare earth oxides (cREO).

Together with development and acquisitions of advanced nanoimprint lithography, and a broad portfolio of quasiphotonic crystal patents, IQE has developed a unique and very powerful set of complimentary technologies which will play a major role in the company’s future.

All the acquisitions are playing a crucial role in IQE’s strategy to evolve from just being an epiwafer foundry to a business that offers a broad range of innovative and in many cases unique materials solutions to its customers.

“Some, like cREO, facilitate putting compound semis onto silicon wafers, which allows us to get into a much larger market place,” enthuses Nelson. “You get the technical benefit of the advanced properties of compound semiconductors, and the almost infinite variety of properties you can engineer, with the cost and scale of the silicon industry, where you can manufacture with substrates up to 300 millimetres.”

Championing the cluster

The future looks very bright for IQE. But that’s not just due to the growth of IQE – it is also because the company is sitting at the heart of the world’s first compound semiconductor cluster, which Nelson has been instrumental in forming.

Nelson started thinking about this at the start of the decade, as a way to address the weaknesses in the UK’s compound semiconductor industry. “In 2011, I approached the economic minister for Wales at the time, to try to persuade them that there needed to be a much stronger infrastructure supporting compound semi. IQE was manufacturing wafers here, but we had virtually no customers in the UK.”

IQE joins the FTSE on 19 May 2000. Left to right are Chris Meadows, Investor Relations Manager at IQE, the CEO of the FTSE, IQE CEO Drew Nelson, and Howard Williams, Operations Director.

Illustrating this point is the re-shaping of Nelson’s former employer, BT, which made many great contributions to the development and manufacture of fibre-optic networks. “Today British Telecom imports 100 percent of its fibre-optic systems from China,” says Nelson. “And ironically, we probably build a significant amount of the InP chips that end up in those systems here in Cardiff.”

Nelson’s efforts at helping to develop a Compound Semiconductor cluster in South Wales also involved working within a group set up by the European Commissioner for Technology for the Digital Economy. Involved in a team looking at key enabling technologies, Nelson focused on how to rebuild the continent’s manufacturing capability in compound semiconductors. His solution: construct a sovereign capability for compound semiconductors in South Wales. “It seemed a very good way to provide a more competitive edge for the UK, and for Europe.”

The next step involved lobbying the Welsh Government and Cardiff University to invest in an Institute for Compound Semiconductors based at the University’s new innovation campus. Persuading them wasn’t easy, but collectively they ended up investing £75 million, which has since leveraged £17 million from the Research Partnership Investment Fund, and spurred the setting up of an EPSRC Manufacturing Hub for Compound Semiconductors, backed by £10 million.

“The vision there is to create an institute which will have capability to go up to 8-inch materials, compound semis on silicon, and to do early stage research across a broad range of materials,” explains Nelson. Some of the funding has been used to construct a new building, which could be ready as early as the end of next year. Until they move in, the researchers are working in a cleanroom that has been upgraded for 6-inch processing.

“The big difference now with the approach of the university is that they want to build the cleanrooms and use the tools with industrial discipline,” says Nelson. “So rather than just having labs that any student can come in and play with, the equipment is being run on a much more industrial-like and professional basis.”

This new approach may assist the efforts of the researchers, according to Nelson. As experiments require a change to one parameter while keeping all the others the same, the greater rigour of all the processes in the cleanroom should make it easy to identify the reason behind a change.

To take the best ideas that come out of the University and provide a pathway to commercialisation, IQE and the University have set up a joint venture, known as the Compound Semiconductor Centre (CSC). With funding from Cardiff University and some equipment from IQE, CSC, which is now in its third year, has more than ten significant collaborative research projects underway.

Another key partner in the cluster is Newport Wafer Fab. This 200 mm silicon facility passed into the hands of Infineon in 2015, when the German powerhouse bought International Rectifier. Infineon decided that it had more global fab capacity than it needed, so it would either sell or close the Newport fab by the end of 2017.

“I ended up leading a private equity buy-out for Newport Wafer Fab,” explains Nelson. “The direction of travel for that as part of the compound semi cluster is to transition from 100 percent silicon to building compound semi-on-silicon chips at 200 millimetre.” The later could include power and RF devices made from GaN-on-silicon, silicon photonics incorporating III-V devices, and structures that feature an intermediary layer of crystalline rare earth oxides.

Other key players in the cluster include: SPTS, a provider of etching and deposition equipment to the compound semiconductor industry; packaging expert Microsemi; and Swansea University, which has a large nano-health centre, and is setting up a centre for Integrative Semiconductor Materials.

Last but by no means least is the Compound Semiconductor Applications Catapult, an open access R&D facility focused on helping UK businesses exploit advances in compound semiconductor technologies.

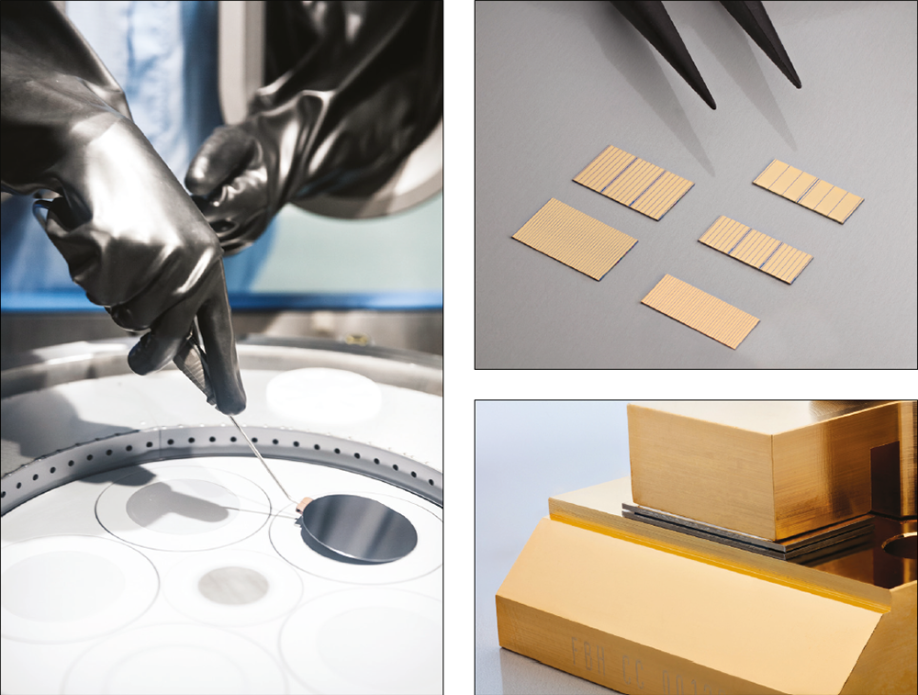

IQE’s facilities have grown over 30 years, and now include fabs in Greensboro, North Carolina (bottom left) and Singapore (top left). In Cardiff, capacity is increasing with the a new fab being built (bottom right) that will complement the one at St Mellons (top right).

The CS Catapult is moving into a building initially constructed for LG Semicon. “The main fab is now used as what I believe is Europe’s largest data centre, and the building next to it is package-andtest, which is highly suited for fitting out as an epi facility.”

That is the plan for this building, which is being re-purposed with support from Cardiff City Region. Other cluster partners will share this with IQE, which is setting up a compound semiconductor epifoundry there. “This is going to be, we believe, the biggest in the world for outsourced epi,” says Nelson. “It has the capability of housing 100 MOVD tools.” The Catapult will be located in a separate part of the building.

Working together, those within the cluster are covering all aspects of production, from wafers to chips, package devices and equipment. “So anyone can interact with the cluster at any point they wish, whether it is for production, for R&D, or for development,” say Nelson. With such a hubbub of activity, those wishing to work with the cluster may be unsure who to approach. To address this, a brand name has been set up, CS Connect, which can provide a point of contact for all interested parties.

The impact that the cluster is having is delighting Nelson, who is clearly passionate to see more high-tech manufacturing within the UK: “We’ve even got examples of fairly significant companies in Asia outsourcing high-tech manufacturing to the Cluster. This is a complete, 180-degree turnaround for the cluster from what you would expect – UK companies outsourcing all the hi-tech manufacturing to Asia.”

Thirty years on from the launch of his epiwafer company, it is clear that Nelson is not resting on his laurels. He is as enthusiastic as ever to drive success at IQE, but now this mission extends to triumphs for the cluster.

IQE’s key milestones

1988 Launch of Epitaxial Products International (EPI)

1999 EPI merges with QED and floats on the EASDAQ

2000 IQE floats on London Stock Exchange

2000 Launches subsidiary IQE Silicon and acquires Wafer Technology in Milton Keynes, UK

2006 Acquires Emcore’s Electronic Materials Division in New Jersey, USA

2007 Acquires MBE Technologies of Singapore

2009 Acquires GaN nanotechnology expert NanoGaN of Bath, UK

2010 Acquires antimony substrate maker Galaxy Semicondcutors of Spokane, WA

2012 Acquires the epi-business of RFMD in North Carolina, USA

2018 Acquires the pioneer of crystalline rare earth oxide layers, Translucent of Palo Alto, CA

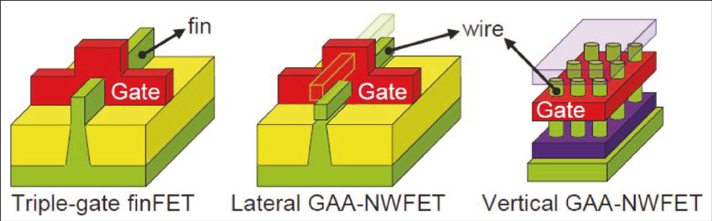

Compound semiconductor highlights at this year’s VLSI included tunnel FETs with a record-breaking subthreshold swing, GeSn transistors with a fin width below 10 nm, and InGaAs photoFETs setting a new benchmark for responsivity Richard Stevenson reports

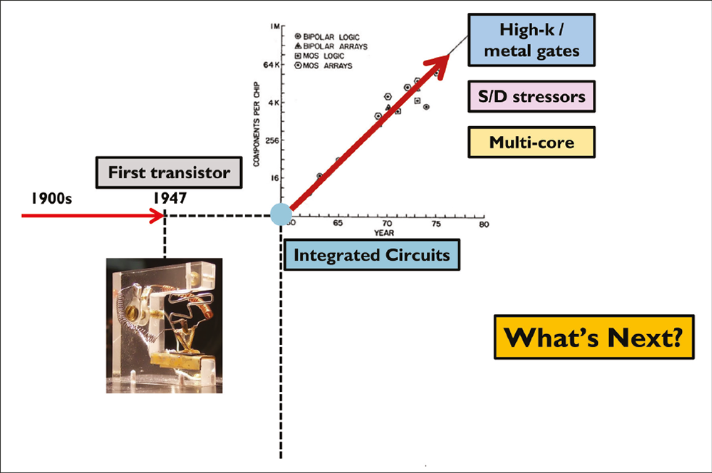

For a decade or more, our community has devoted much effort to the development of III-V transistors for maintaining the march of Moore’s Law. It has been argued that armed with a superior mobility to silicon devices, those made from compound semiconductors can operate at a lower voltage while maintaining current, and thus enable power scaling at future nodes.

Progress of these devices is continuing, with some of the latest breakthroughs reported at the 2018 Symposium on VLSI Technology and Circuits, held in late June in Honolulu, HI. At that gathering, where there were also reports of progress associated with III-V photodetectors, highlights included talks on: tunnel FETs made from InGaAs and GaAsSb with a sub-threshold swing that broke new ground; GeSn FinFETs with a fin width below 10 nm that set a new benchmark for transconductance; and tuneable InGaAs nanomenbrane photoFETs on flexible substrates, which are promising for lightweight, wide-angle imaging applications.

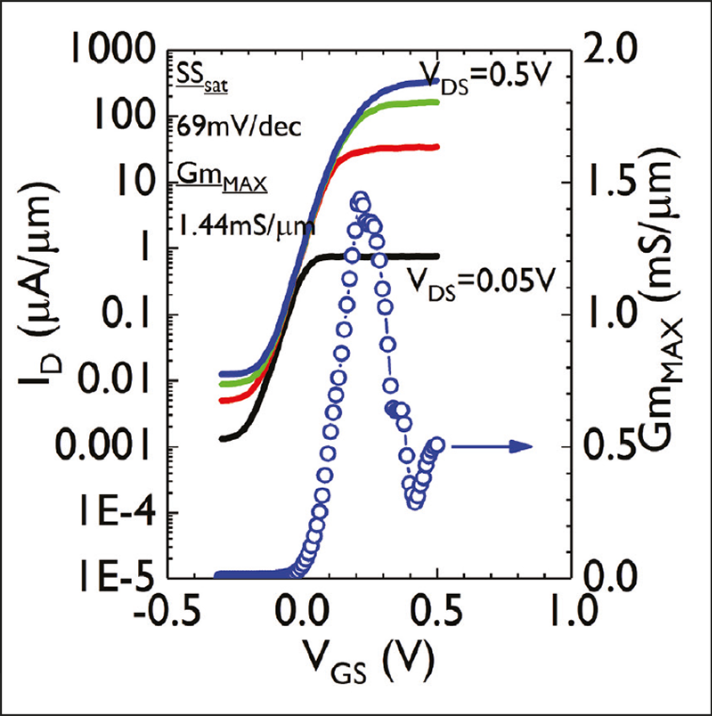

Superior sub-threshold swing

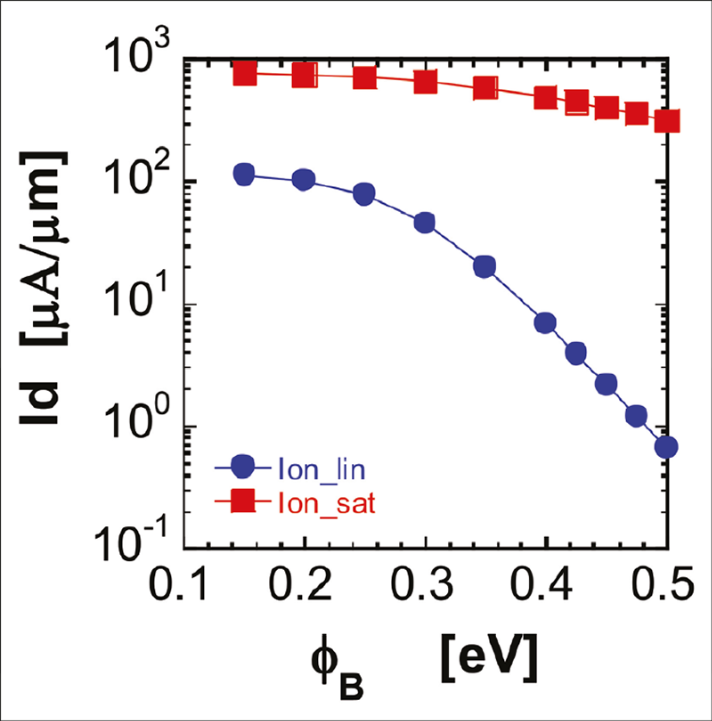

Makers of these record-breaking tunnel FETs, Alireza Alian and co-workers from imec, Belgium, claim that their best devices, which sport a vertical nanowire architecture, produce a record transconductance of just 47 mV/decade. This low value is important, because it allows the device to operate at a lower power supply voltage while still delivering a high current. For imec’s leading FETs, the drive current is 700 μA/μm at 0.35 V, for a fixed off-current of 1 nA/μm. That voltage is far lower than that used in today’s ICs, which operate at around 0.9 V, highlighting the promise of III-V tunnel FETs for all mobile applications, where they could lengthen battery life.

imec’s best results were obtained with nanowires with a 30 nm diameter. For insertion in a future node they would need to be “somewhere around ten nanometres”, says Alian.

Another group in Europe, based at Lund University, have also produced encouraging results with vertical nanowire devices. “They did it using grown wires,” says Alian. “We got quite similar results by etching the wires.”

In Alian’s view, the top-down approach that he and his co-workers adopt is better suited to high-volume manufacture. “It is believed to be more controllable – and less variability is expected than when you grow the wires.”

Fabrication of imec’s tunnel FETs begins with the growth of III-V layers on an InP substrate. The researchers employ this growth process, rather than MOCVD, because they believe it produces better interfaces. “CVD is usually at a higher temperature than MBE, so intermixing at interfaces is more severe,” argues Alain.

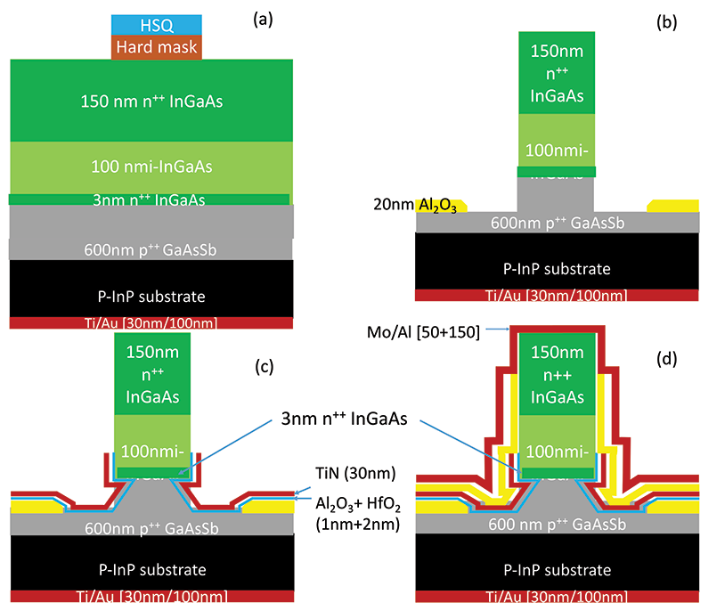

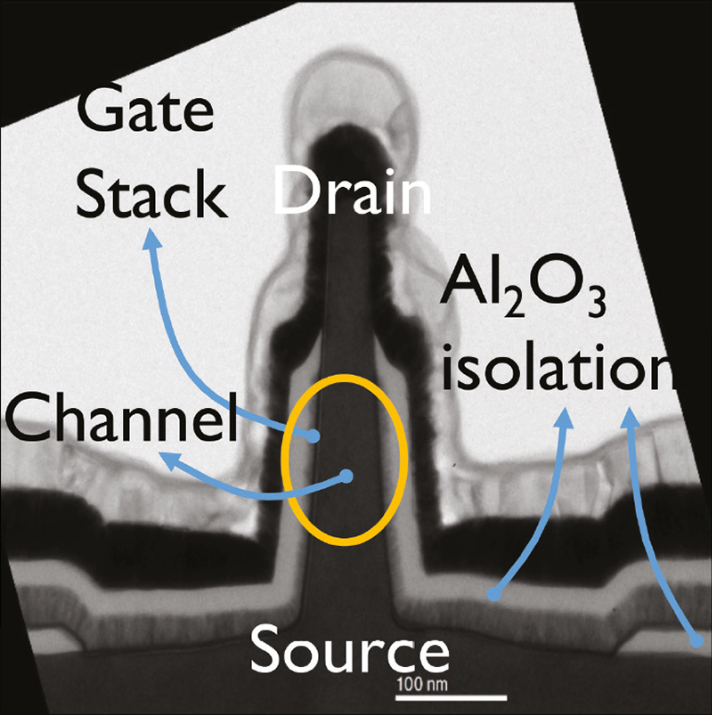

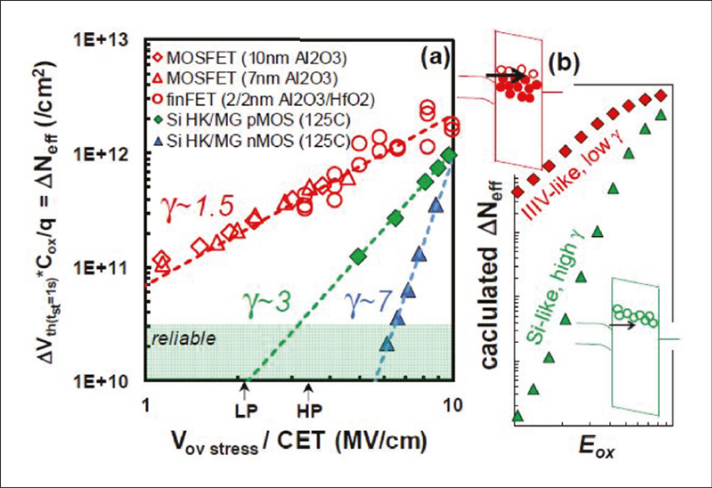

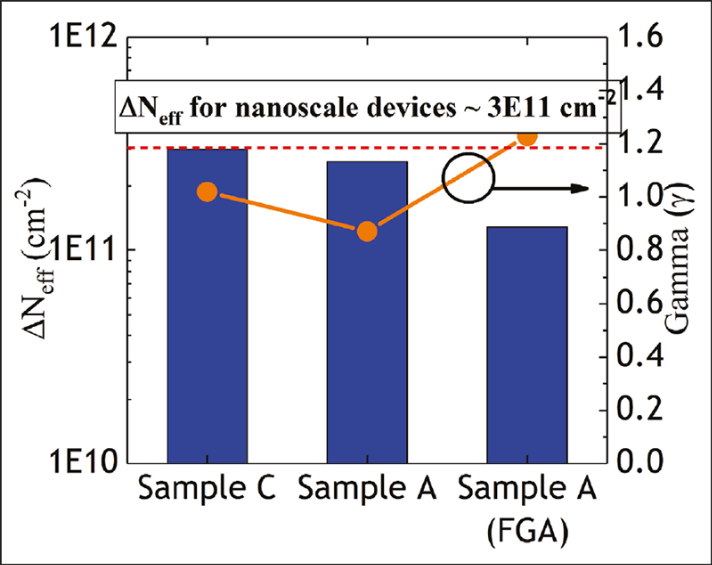

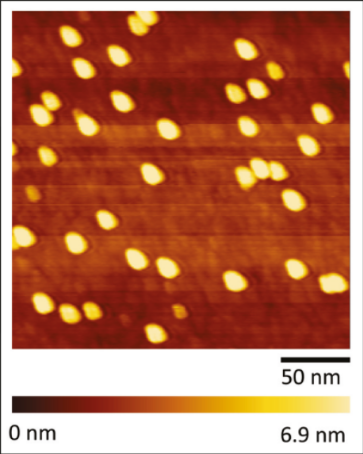

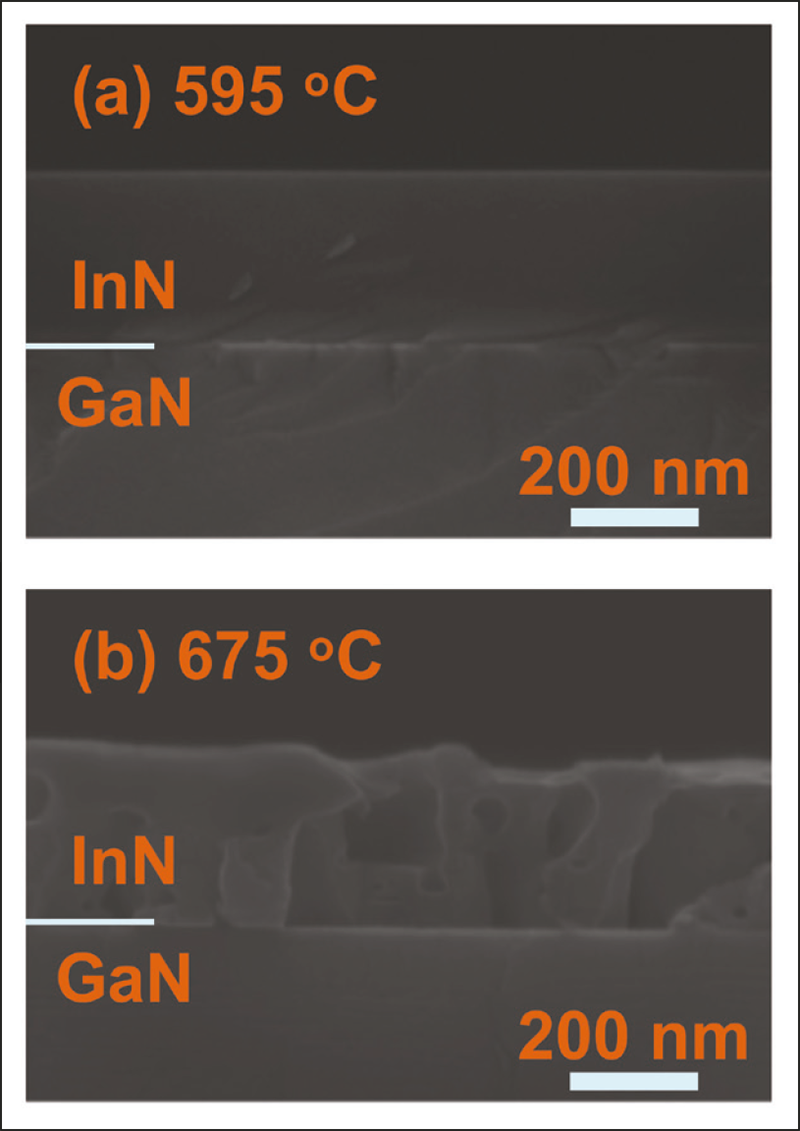

The team produced a range of tunnel FETs, formed from nanowires with diameters of either 30 nm, 50 nm, 70 nm or 90 nm. Electron beam lithography defines their diameter, prior to etching into the heterostructure at 100 °C with a methane-based plasma to create these structures. Atomic layer deposition adds a gate oxide, comprising 1 nm-thick Al2O3 and 2 nm-thick HfO2. Fabrication finishes with the addition of a top spacer, top and back contacts, and in some cases an anneal in forming gas at 350 °C (see Figure 1 for a device architecture).

Figure 1. Formation of imec’s tunnel FET begins with the growth of a heterostructure by MBE, and the use of lithography to define the diameter of the nanowires (a). Dry etching forms the nanowires (b), before a gate stack is added by atomic layer deposition (c), and a top spacer and top and back contacts are introduced (d).

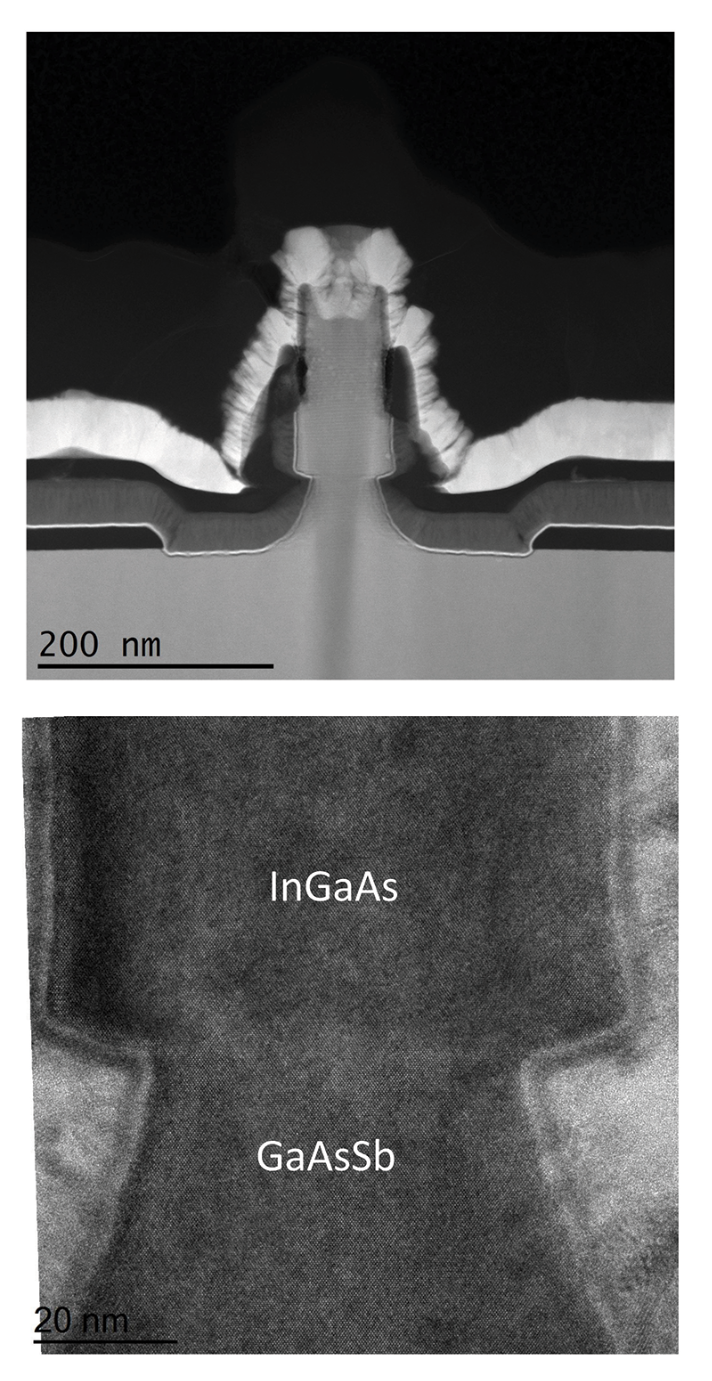

Measurements on various devices, which have been studied with several microscopy techniques (see Figure 2), reveal significant variations in the drive current and the threshold voltage for transistors with the same nanowire diameter. These variations, which could be addressed by optimising the process, are attributed to unintended differences in doping and nanowire diameter.

Alian and co-workers observed a negative differential resistance in the output characteristics of their transistors, confirming that device behaviour is dominated by tunnelling. Performance improves with annealing in the forming gas, thanks to a reduction in the density of interface traps in the InGaAs layer.

A sub-threshold voltage below 60 mV/decade is only observed in devices with a nanowire diameter of 30 nm and 50 nm. This suggests that narrower wires improve sub-threshold voltage, a conjecture backed by simulations of the band-to-band tunnelling current – they indicate that shrinking the nanowire diameter to 20 nm could decrease the subthreshold swing to 20-30 mV/decade.

Any shrinking of the diameter of the nanowires must go hand-in-hand with increases in the source doping and a reduction in gate-source overlap. “Achievinghigher doping is not difficult,” says Alian, who believes that it is easy to realise levels of 5 x 1019 cm-3. “For the overlap, it is possible, but variability is expected to become an issue.” However, this can be addressed by engineering.

Alian and co-workers are hoping to now investigate the effects of higher doping. After this, the team may go on to study devices with narrower diameters.

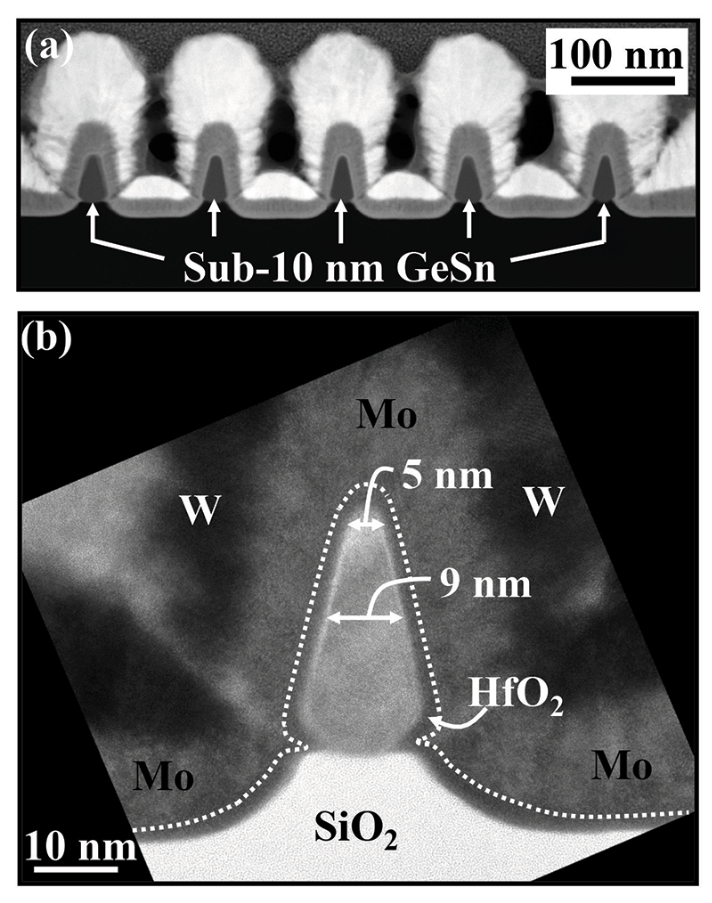

Very fine fins

A claim for record-breaking miniaturisation came from a partnership between the National University of Singapore, Nanyang Technological University and Applied Materials. This collaboration believes that it has broken new ground by making GeSn pFETs with a fin width below 10 nm. The width at the top of the fin, produced on a 200 nm GeSn-on-insulator substrate, is just 5 nm.

Figure 2. Scanning transmission electron microscopy of the tunnel FET produced by the team at imec (a) can reveal the high quality of the InGaAs and GaAsSb layers (b).

This is not the ultimate limit, though – team spokesman Xiao Gong from National University of Singapore believes that optimizing the sidewall angle of the GeSn fin could lead to even smaller fin widths of about 3-5 nm. “The question is, at such small fin width, how high a mobility or source injection velocity can we achieve.”

Gong says that the team’s devices, which could make an impact at the sub 3 nm node, are produced with a process that is repeatable and straightforward.

Figure 3. (a) Darkfield transmission electron microscopy images of the GeSn p-finFETs produced by the team from the National University of Singapore, Nanyang Technological University and Applied Materials. (b) A highresolution transmission electron microscopy of a GeSn fin surrounded by the high-κ dielectric and the metal gate.

“The GeSn fins were first formed using an ICP dry etch to achieve a smallest fin width of about 15 nanometres. A digital etch process was then employed to trim it down to sub-10 nanometres.”

The only step in the fabrication process that is not suitable for high-volume manufacturing is the patterning of the wafer by electron-beam lithography. But Gong says that this weakness can be overcome by turning to optical lithography.

Fabrication of the devices begins with CVD of a 10 nm-thick film of Ge0.95Sn0.05 on a silicon substrate. Using Ge0.95Sn0.05, rather than pure germanium, leads to a 55 percent hike in high-field hole mobility, according to experiment.

The next steps in device fabrication are: the definition of the channel; source and drain implantation, using boron; activation of the dopants, by heating the wafer to 400 °C for 60 s; forming the fins with a chlorinebased ICP etch, and then trimming with a digital etch; adding a gate stack, using process temperatures below 250 °C; etching the gate; and adding source and drain contacts (see Figure 3 for images of the devices).

A range of FinFETs have been produced with channel lengths from 50 nm to 200 nm, fin widths from 9 nm to 20 nm, and fin heights of 30 nm.

Measurements reveal that the smaller the fin width, the greater the suppression of short-channel effects. This helps to lower the sub-threshold swing, which fell from a minimum of 90 mV/decade for FETs with a 30 nmwide fin to a minimum of 63 mV/decade for a variant with a 9 nm-wide fin.

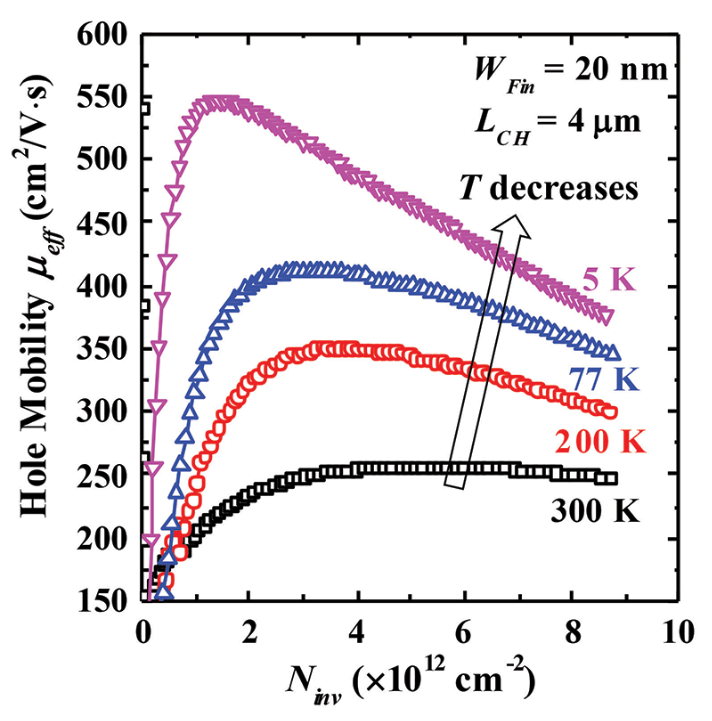

Other important characteristics of the transistors are a transconductance that can be as high as a record-breaking 900 μs/μm, an on-current that can hit 420 μA/μm at 1 V above threshold, a high hole mobility (see Figure 4) and an on-off ratio of 104. When judged in terms of the ratio of transconductance to saturated sub-threshold swing, the team’s best device hits 10.5, a value that is claimed to be a record.

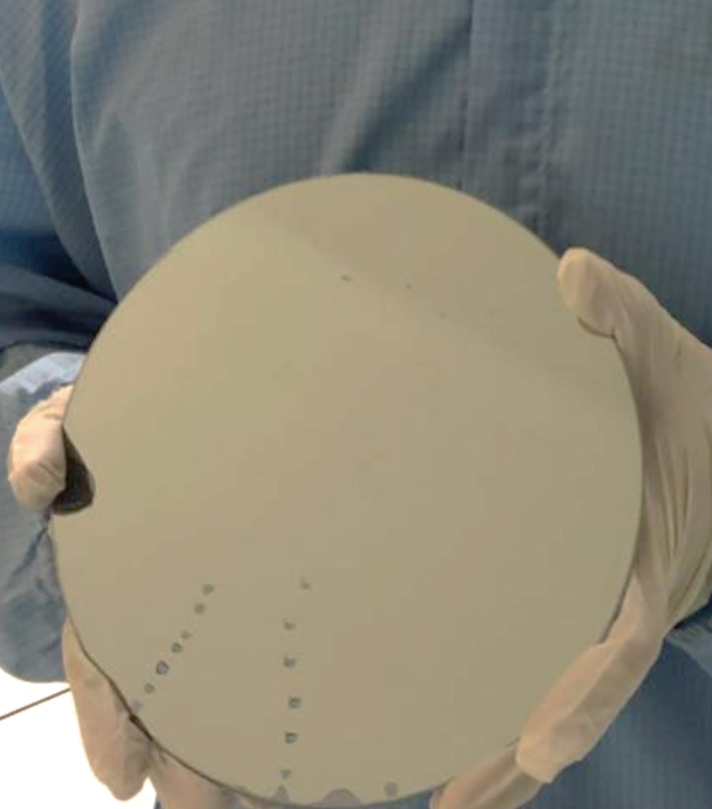

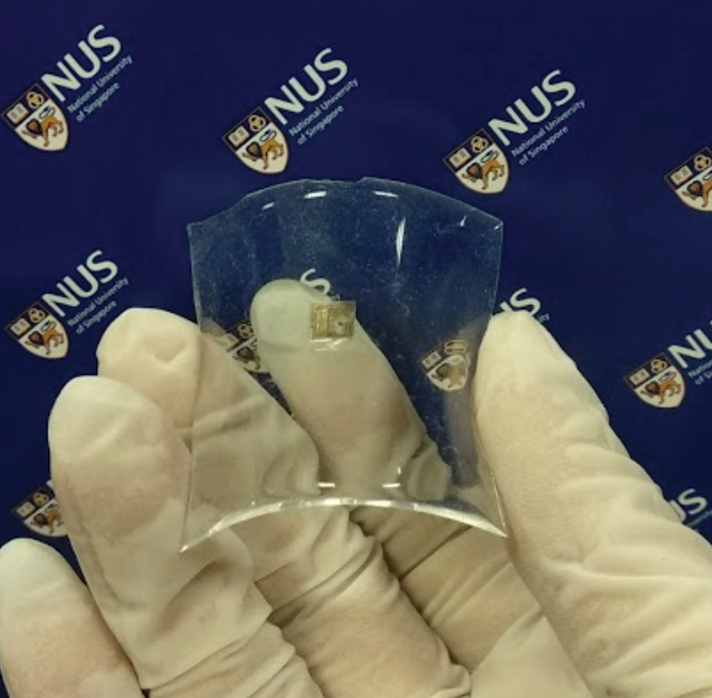

The 200 mm GeSn-on-insulator substrate used by the team from the National University of Singapore, Nanayang Technological University and Applied Materials to produce sub-10 nm pFETs with a record-breaking ratio of transconductance to saturated sub-threshold swing.

This figure-of-merit is important, according to the team, because it captures several key metrics. “Saturated sub-threshold swing gives you the information of the gate stack quality and on-off ratio for the current at a high drain-source voltage,” says Gong, while the transconductance indicates the drive current that may be realised in the on-state. “For a transistor, we would like the ratio of transconductance to saturated sub-threshold swing as high as possible.”

Figure 4. The effective mobility as a function of inversion carrier density, for GeSn pFETs produced by a partnership between researchers at the National University of Singapore, Nanyang Technological University and Applied Materials.

One of the next goals for the team is to replicate the good performance of the sub-10 nm GeSn p-finFETs with GeSn n-finFETs. “Gate stack and source/drain engineering for nFETs will be done to reduce the interface trap density and reduce the source/drain series resistance,” explains Gong, who reveals that the team may also investigate the use of GeSn as the channel in TFETs.

Flexible photo-transistors

Two major changes in the coming decades will be the introduction of smart vehicles and autonomous drones. Both will benefit from lightweight imagers operating in the near and short-wave infrared – and if these devices could cover large surfaces, alongside detectors, they could also aid the development of ultra-light machines with wide-field imaging capability.

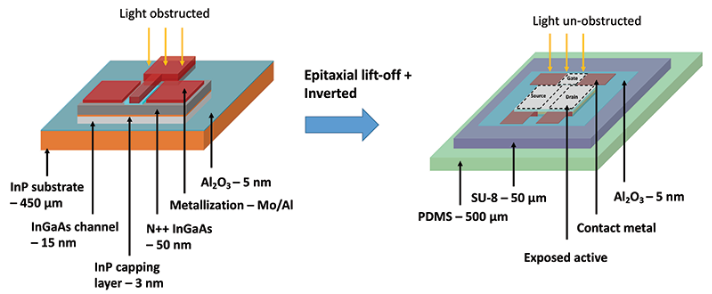

Figure 5. Researchers at imec and the National University of Singapore create a flexible, high performance device by using epitaxial lift-off to mount, on a polymer, an InGaAs-on-InP MOSHEMT with an exposed InGaAs channel.

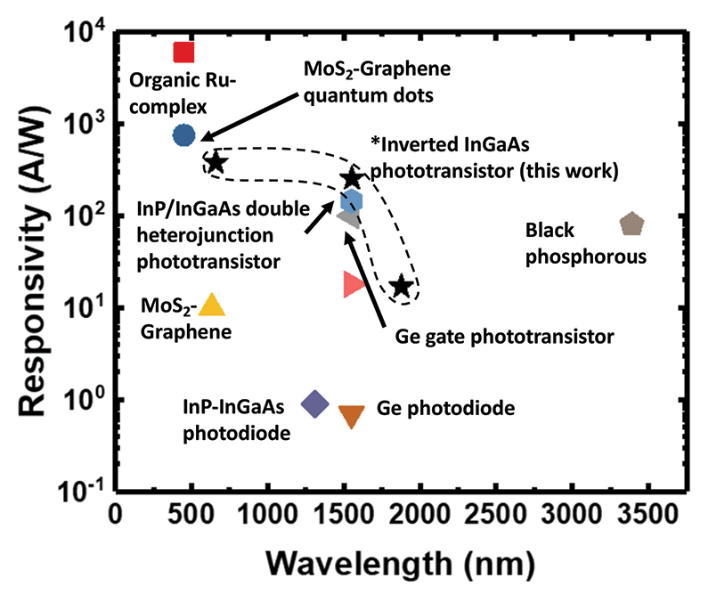

A promising option for such detectors is being pioneered by a team from imec and the National University of Singapore. Their approach, detailed at the latest VLSI meeting, involves the use of epitaxial lift-off to expose the InGaAs channel of an InGaAs-on-InP MOSHEMT and create a flexible device that is more sensitive than existing silicon and III-V photodetectors in the near and short infrared (see Figure 5).

Spokesman for the team, Yida Li from the National University of Singapore, says that the motivation behind this is the aim of building a device that is flexible and lightweight. “This may allow us to enable imaging arrays on large-area surfaces to replace bulky hyperspectral imagers.”

Li and co-workers decided to detect the light with high-quality layers of InGaAs, which they believe offer some advantages over more popular, but less mature, two-dimensional materials, such as graphene and MoS2. “We have exploited one key advantage of thinfilm devices by lifting off and inverting the device, to increase its photosensitive area, while allowing it to be flexible,” argues Li.

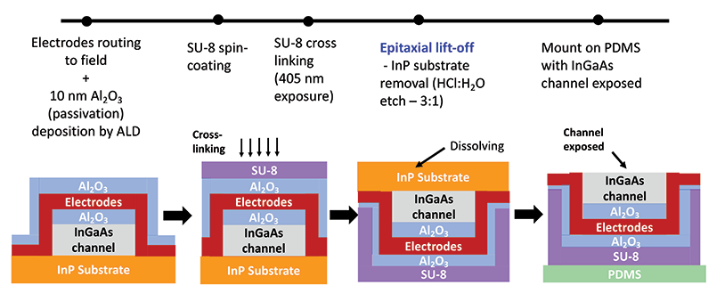

Figure 6. The photoFET is fabricated with a series of steps that include spin-coating, epitaxial lift-off and exposure of an InGaAs channel.

Fabrication of the photoFETs begins with the growth of an InGaAs MOSHEMT on an InP substrate. Following meas isolation and the routing of electrode contacts to the field area, this epiwafer is bonded to an epoxy-based negative photoresist, SU-8, before the InP substrate is removed and the InGaAs channel exposed (see Figure 6 for details)

“The SU-8 is used to protect the photo devices from the chemical etch process, as well as to serve as a flexible backing for the ELO devices,” explains Li.

He believes that these detectors could be produced with high-volume processes. “In this work, we explored the transfer of complete devices with metallization. This may allow for entire arrays of connected devices to be transferred rather than individual devices, leading to increased density and throughput.” Alternatively, production could draw on high-precision heterogeneous pick-and-place, which Li says is a base technology in advanced wafer-level packaging.

The photoFET, on a polymer substrate, shows no signs of degradation when flexed with a radius of 10 cm.

Device measurements reveal that for a gate bias range of 6 V, photocurrent can be tuned by over five orders of magnitude. The on-state photoresponsivity is 380 A/W at 660 nm, and 15 A/W at 1877 nm, values that are claimed to be more than double those for existing silicon and III-V photodetectors. No degradation in performance is observed when the device is flexed with a radius down to 10 cm.

To improve performance in the short-wave infrared, the team can adjust the composition of InGaAs. “There is nothing that stops us from lowering the bandgap with higher indium content or moving to a lower-bandgap III-V for longer wavelength sensitivity,” says Li, who points out that such a move would need to strike a balance between dark current leakage and sensitivity.

Figure 7. The responsivity of the InGaAs photoFET is far higher than that of many rival technologies.

The next goals for the team are to improve device performance through optimisation of the process, and to investigate opportunities to scale up to larger arrays.

This effort, and those that have led to record values for both the sub-threshold swing of vertical nanowire tunnel FETs and for the transconductance of GeSn pFETs with sub 10 nm fins, highlight the innovation within the compound semiconductor industry. Further breakthroughs in these areas will be reported at next year’s VLSI – and prior to that, at the next IEDM, to be held on 1-5 December in San Francisco.

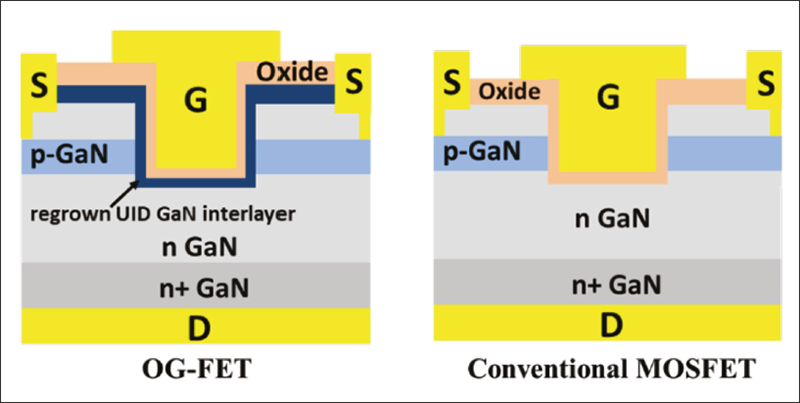

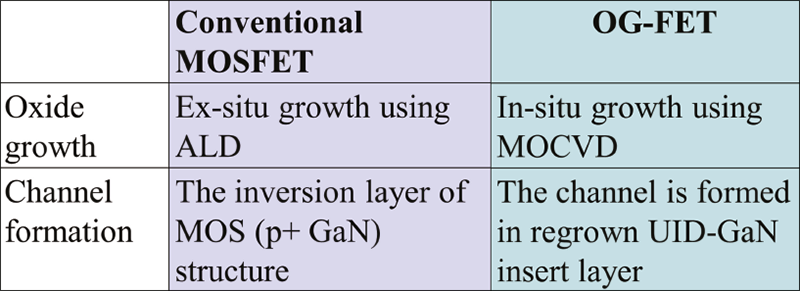

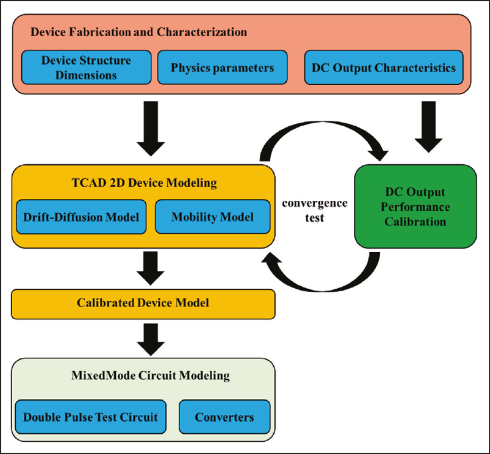

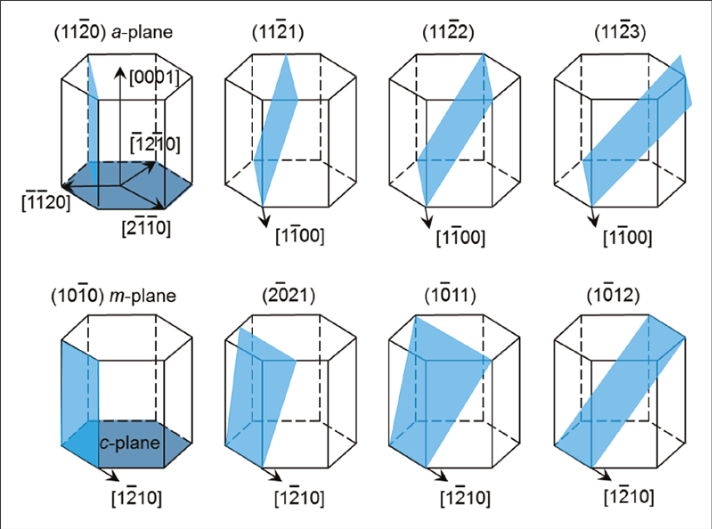

GaN FETs featuring a thin unintentional doped GaN interlayer as the channel and an in-situ grown gate-dielectric can boost efficiency at the system level, thanks to a higher channel mobility and lower on-resistance. By Dong Ji and Srabanti Chowdhury from the University of California, Davis, and Chirag Gupta and Umesh Mishra from the University of California, Santa Barbara

Power converters are widely used in power electronic systems, where they convert one form of electrical energy to another. They are used to form rectifiers, which convert AC voltages to those that are DC; they create inverters that provide the DC to AC conversion; and they step up and down DC and AC voltages.

Due to the widespread use of power converters, any increase in the efficiency of power electronics can play a crucial role in reducing the global carbon footprint. Currently, two-fifths of all the energy that is consumed is first converted into electricity, and this figure may rise to three-fifths with increasing use of electric and plug-in hybrid vehicles and high-speed rail transportation. And by 2030, it is anticipated that as much as 80 percent of electrical energy will pass through power electronics between generation and consumption.

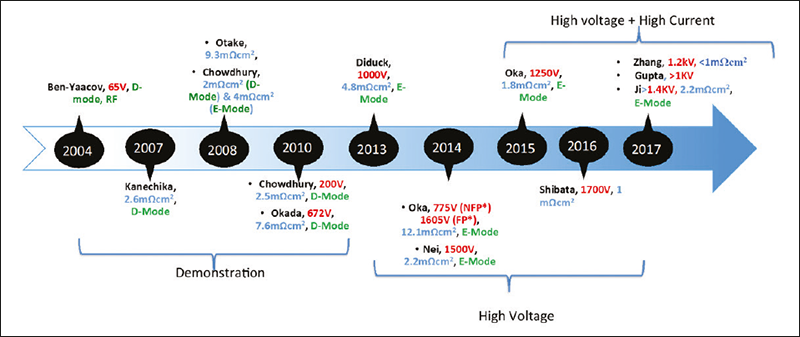

To help to increase the efficiency of power electronics, in 2014 ARPA-E launched a new programme called SWITCHES – it is short for Strategies for Wide Bandgap, Inexpensive Transistors for Controlling High-Efficiency Systems. This effort, involving five universities and nine companies, has focused on the development of 1.2 kV power transistors that have the potential to realize functional cost parity with silicon-based devices.

Our team from the University of California, Davis, and the University of California, Santa Barbara, has played its part in this programme. Our contribution has been the development of a novel device – an in-situ oxide, GaN interlayer based MOSFET – that sets a new benchmark for DC performance at 1.2 kV.

The power electronics revolution

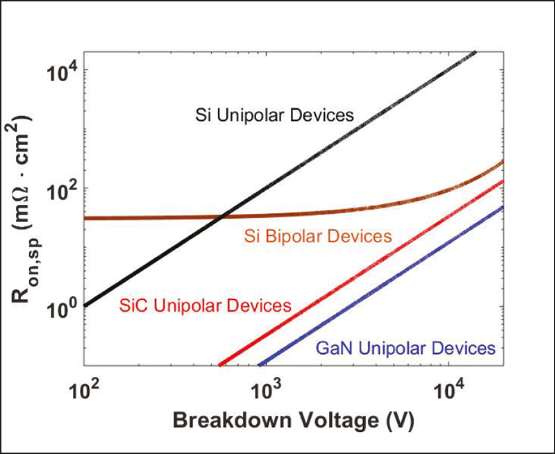

Today silicon, in the form of the MOSFET and the IGBT, dominates the market for power semiconductor devices. However, this pair of incumbent transistors is reaching a performance plateau, and almost all improvements are incremental.

To reach a new level of performance for power switching, there needs to be an uptake in devices made from wide bandgap materials, such as GaN and SiC. Devices made from these materials are able to set a new benchmark for the trade-off between the breakdown voltage and the on-resistance (see Figure 1).

Figure 1. The tradeoff between the specific on-resistance (Ron,sp) and the breakdown voltage for silicon and it two leading challengers, SiC and GaN