When researchers develop a technology, they often do so with a product in mind. But there are times when things don’t work out in the way they intended – and the technology ends up being used in a different manner.

That may well be the case for the technology that engineers at imec have developed to form high-quality III-Vs on a silicon substrate. When efforts started around a decade ago, the ultimate goal was the fabrication of compound semiconductor MOSFETs on silicon.

That effort is still underway, but more recently this III-V-on-silicon technology has also been used as a way to enable the growth of lasers on silicon. That’s important, as improvements in the performance of silicon ICs are now under threat from on-chip and chip-to-chip data transfer rates, which are getting close to their limit. The solution is to switch from electrons to photons – hence the introduction of laser on silicon.

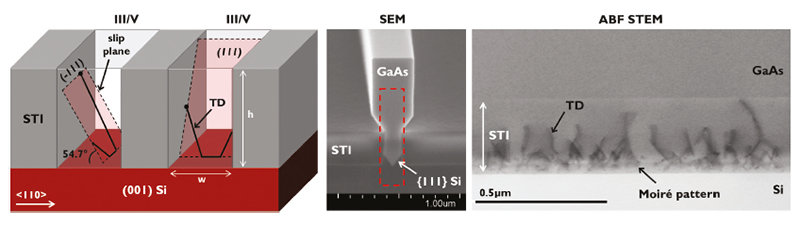

The researchers at imec are producing high-quality III-V material on silicon by a technique known as aspect ratio trapping. Defects are inevitable, due to the signifi cant lattice-mismatch between the silicon and the III-Vs, but these imperfections are annihilated at the walls of the trench. What’s more, by having a V-shape at the bottom of the trench, planes can be selected that prevent anti-phase domains – a destroyer of device performance.

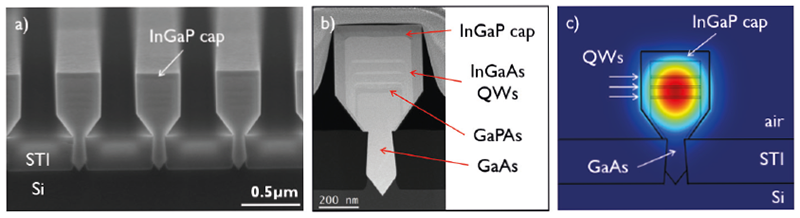

By controlling the growth rates of the III-Vs on various facets, imec’s engineers defi ne the shape of the material that emerges from the trench: it can be rectangular, triangular or hexagonal in nature (see imec’s feature “Gaining an edge with nano-ridges” to discover the details of their craft).

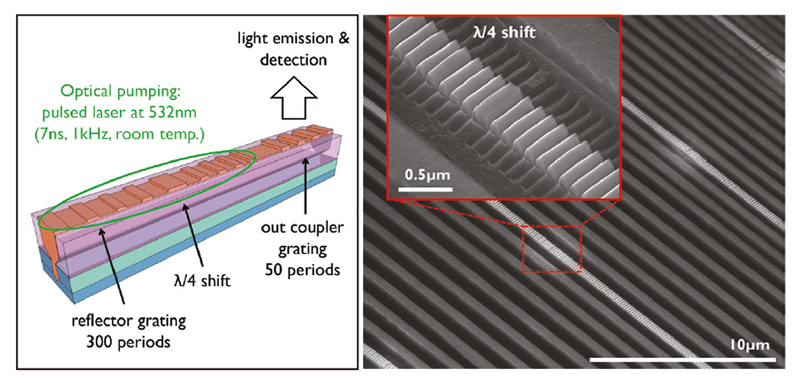

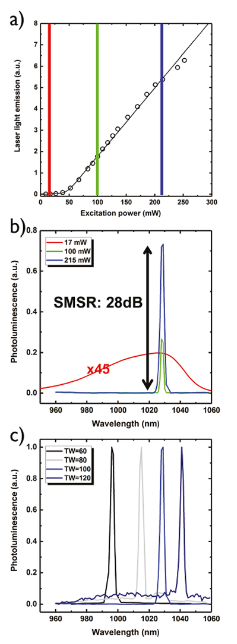

imec’s work on nano-ridge lasers is still in its infancy. So far, the team have produced optically pumped lasers on trenches with widths from 60 nm to 120 nm. By inserting a phase-shift grating, a single-mode emission peak is ensured.

One of the next goals will surely be the progression from optically pumped to electrically pumped lasers. Given the dimensions, success will not be easy. But imec has a great track record in innovation, so I, for one, am optimistic.

Wolfspeed has announced new LDMOS and GaN HEMT product offerings that enable smaller systems with greater reliability and efficiency.

“The acquisition of Infineon’s RF power business has enabled Cree’s Wolfspeed business to transition to the next level of the RF power semiconductor business,” said Lance Wilson, research director at ABI Research. “Historically, Wolfspeed has been a principal player in GaN technology but the addition of Infineon’s LDMOS portfolio has put them into the top echelon of high-power RF.”

The acquisition brings LDMOS technology and expertise to Wolfspeed, enabling the company to provide the optimal RF power solution to meet customers’ needs, regardless of the type of technology used. The expansion includes Wolfspeed’s new 28 V 2620-2690 MHz Asymmetric Doherty Transistor, which is an LDMOS Doherty transistor that uses LD12 technology. This and other LD12 components use a plastic overmold package that delivers the same performance as open cavity packages, offering significant increases in efficiency at a lower cost.

“Wolfspeed is committed to supporting the growth of our LDMOS portfolio, as shown by the release of our new 28 V Asymmetric Doherty Transistor,” said Gerhard Wolf, Wolfspeed’s vice president and general manager of RF.

“The expansion of our LDMOS portfolio delivers on the promise of continued innovation for cellular applications, like improved 4G networks and the shift to 5G networks. In the radar market, Wolfspeed is providing aerospace and defence operators better target discrimination and a longer detection range with the launch of the highest output power GaN products on the market, including a 1200 W packaged GaN HEMT.

The 1200 W GaN HEMT is said to set a new industry benchmark for performance by delivering the highest output power for a GaN L-Band radar product on the market today. The device’s high-output power enables fewer devices to be used, resulting in simplified system architectures, lower materials costs, reduced energy consumption and increased system reaction time that is critical in defense and aerospace settings.

Optical communications firms Acacia and Oclaro are working together to create fully interoperable CFP2-DCO (digital coherent optics) modules based on Acacia’s Meru DSP. Oclaro plans to launch a new CFP2-DCO module that will feature plug-and-play compatibility with the Acacia CFP2-DCO, providing customers with two proven coherent optics suppliers for the 100/200G CFP2-DCO form factor. The modules will support transmission speeds of 100G and 200G for use in access, metro and data centre interconnect markets.

CFP2-DCOs are becoming increasingly important for higher-speed optical networks because they integrate the coherent DSP into the pluggable module. The digital host interface enables simpler integration between module and system resulting in faster service activation and a pay-as-you-grow deployment model for telecommunication providers whereby the cost of additional ports can be deferred until additional services are needed.

“Our 43Gbaud Coherent Transmitter Receiver Optical Sub-Assembly (TROSA) is at the heart of our CFP2-DCO. The TROSA leverages InP PIC technology from Oclaro’s highly successful CFP2-ACO to achieve industry leading optical performance in a small form factor,” said Beck Mason, president of the Integrated Photonics Business at Oclaro. “By establishing a fully interoperable solution with Acacia, our customers will have two sources of supply for these critical components, enabling them to efficiently upgrade their networks to higher speeds.”

The CFP2-DCO form factor is being introduced by multiple network equipment manufacturers in switch, router, and transport platforms.

The CFP2-DCO modules support four times higher density than current generation 100G CFP-DCO solutions by doubling the data rate in a smaller, lower power, pluggable module enabling customers to quickly and cost-effectively roll-out 200G networks.

In addition to proprietary operating modes, both companies intend to support the requirements of the Open ROADM MSA for interoperability at 100G. “Network operators and our system partners are excited about the ramp of our CFP2-DCO module,” said Benny Mikkelsen, CTO of Acacia Communications.

“By partnering with Oclaro to ensure interoperability with their Meru-based CFP2-DCO module, we believe we will be better positioned to address the DCO market as industry trends shift favorably toward the CFP2 form factor. We are excited about our relationship with Oclaro and believe that broader adoption of 200G CFP2-DCO modules will be mutually beneficial to our two companies and the customers we serve.”

Plessey Semiconductors is partnering with Smart Glasses firm Vuzix. The two companies are working to develop the necessary technologies for a new generation of AR Smart Glasses, based around the combination of Plessey’s microLED light source product family, Quanta-Brite, and Vuzix’ extensive expertise and IP in Smart Glasses and essential optic technologies.

Plessey has successfully demonstrated how its monolithic microLED technology can be used to deliver Smart Glasses technology for a wide range of AR and MR (mixed-reality) applications for use both indoors and out.

In addition, Vuzix has already developed an evolving family of Smart Glasses culminating in the Vuzix Blade, the next generation smart display with see-through viewing experience via proprietary waveguide optics.

Formed from glass with precision nanostructures, the waveguide is a key component in an AR/MR product, enabling users to see high-resolution computer-generated graphics, images and information superimposed over images from the physical or real world.

In the development of its next-generation product, Vuzix has selected Plessey’s microLED-based Quanta-Brite light engine, which delivers extremely high efficiency and an improvement in lumen output compared to other light sources currently available on the market.

Quanta-Brite is based on Plessey’s GaN-on-silicon technology, with an integrated monolithic array of RGB pixels with advanced first level micro-optical elements to create a bright, largely collimated and highly uniform light source for the illumination of DMD and LCOS display engines.

The resulting optical system is up to 50 percent smaller, lighter, simpler and cheaper than incumbent solutions and the high performance microLED emitters combined with minimal optical system losses result in significantly increased power efficiency.

Size, weight and power reduction are key considerations in AR/MR wearables. Quanta-Brite has been designed specifically for the next generation of Vuzix personal display systems.

“Plessey’s Quanta-Brite microLED technology can be a major enabler of the future of augmented reality,” said Vuzix President and CEO Paul Travers. “As well as delivering high-efficiency, low-power and small-size illumination capabilities, the very high level of luminescence of the Quanta-Brite light source can also enable the development of end products with a sleeker form factor, which is a key attribute of our waveguide based Smart Glasses and critical to mass market adoption.’

“This development with Vuzix, a leading actor in the exploration of next-generation augmented reality, is a significant endorsement of Plessey’s GaN-onsilicon microLED approach,” said Keith Strickland, CTO at Plessey.

“Monolithic microLED technology is fast emerging as the only one that can provide high luminance in a very small form factor with minimal energy consumption, necessary for reducing costs and enabling lightweight batterypowered products for a range of emerging consumer and industrial applications.”

According to the Consumer Technology Association (CTA), headsets and eyewear outfitted for AR and VR applications are set for record sales this year of $1.2 billion in the US market alone.

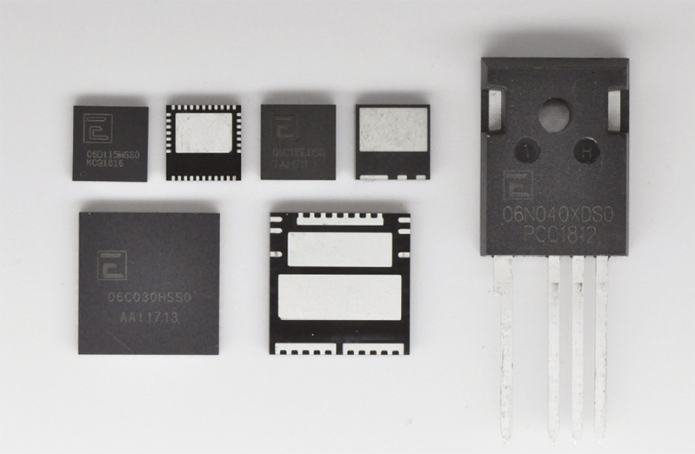

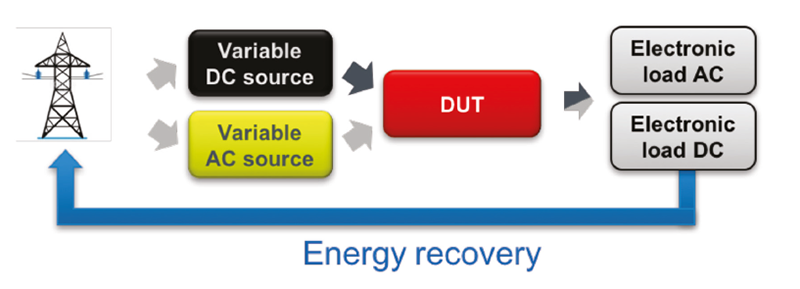

Infineon is starting volume production for CoolGaN products by the end of 2018, the company announced during PCIM Europe. Engineering samples of these products are now available.

Infineon’s CoolGaN is claimed to the one of most reliable and globally qualified GaN solutions in the market. During the quality management process not only the device is tested, but also its behaviour in the application.

At 100 ppm (parts per million), its predicted lifetime is about 55 years, exceeding the expected lifespan by 40 years. CoolGaN enables for example doubled output power in a given energy storage slot size, freeing up space and realising higher efficiency at the same time.

Full production of CoolGaN 400 V and 600 V e-mode HEMTs will start by end of 2018. CoolGaN 400 V will be available in 70 mΩ in SMD bottom-side cooled TO-leadless and top-side cooled DSO-20-87 package.

CoolGaN 600 V comes in top-side cooled DSO-20-87 package and bottom-side cooled DSO-20-85. With 70 mΩ and 190 mΩ 600V CoolGaN devices in bottom-side cooled TOleadless and DFN 8x8 packages, the 600V CoolGaN portfolio will be complemented.

Rohm and GaN Systems have announced a GaN power semiconductors collaboration, with the goal of contributing to the continuing evolution of power electronics. This strategic partnership builds on GaN Systems’ capabilities in power GaN transistors along with Rohm’s expertise in semiconductor design and manufacture.

The companies have agreed to jointly develop form-, fit-, and functioncompatible products using GaN semiconductor dies in both GaN Systems’ GaNPX packaging and Rohm’s traditional power semiconductor packaging.

In addition, GaN Systems and Rohm will work together on GaN semiconductor research and development activities to propose ground-breaking solutions for the industrial, automotive, and consumer electronics fields. And to contribute to greater energy savings and increased power densities in the power electronics market, both companies will continue to collaborate to expand their line-up of GaN products and broaden the range of choices.

“GaN has rapidly made its ascent into power electronics applications and this partnership exemplifies how important GaN has become in a complete power electronics offering,” said Jim Witham, CEO of GaN Systems. “We’re proud to partner with Rohm, a company well known for developing industry-leading technologies.

By combining our joint expertise and capabilities, we’re enabling more businesses to access and experience the benefits of GaN in achieving higher power, more efficient, smaller, and lighter power electronics.”

“Rohm has targeted the power device business as one of our growth strategies. We offer leading-edge products such as SiC power devices and provide power solutions that integrate control technologies, including gate drivers that maximise device performance. We are also developing GaN for next-generation power devices. By leveraging the superior technologies and expertise of both companies, we are able to accelerate the development of high-performance solutions to solve the needs of the power market,” said Katsumi Azuma, senior MD of Rohm Semiconductor.

Kaiam, a US manufacturer of advanced data centre optical transceivers, and the Chinese optical module firm Broadex have announced a partnership agreement where Broadex would manufacture and supply high-end transceivers into the China market.

The two companies announced the signing of a memorandum of understanding (MOU) for furthering cooperation on volume production of QSFP28 100G-CWDM4 transceivers based on Kaiam’s LightScale2 platform. The LightScale2 architecture is said to have fundamental advantages in cost and performance and to be ideally suited for high-volume applications. The agreement allows Broadex to manufacture these units in China and directly address Chinese customers who require local production. This also complements Kaiam’s in-house manufacturing in the UK in Livingston, Scotland, and provides further capacity to address the high-volume data centre market.

“We anticipate very strong demand for 100G transceivers based on our LightScale2 technology,” said Dietmar Zapf, GM / VP of manufacturing at Kaiam. “In addition to the production lines already running at our Livingston, UK facility, we need to develop and secure further expanded capacity for manufacturing these products in high volume. The MOU signed with Broadex would allow us to leverage Broadex’s manufacturing expertise and infrastructure and expand our capacity in the next 3–6 months to meet high demand.”

“We are glad that Kaiam chose to continue working with us for manufacturing its new non-hermetic transceivers for data centre applications,” said Yong Ding, VP and CTO of Broadex Technologies. “We have been producing OSA-level components for Kaiam in high volumes for several years now. The LightScale2 platform is optimised to deliver maximum value and performance in the data centre environment at dramatically lower costs. We will work aggressively to quickly ramp to high volumes with high yields.”

“Kaiam is eagerly anticipating expansion into the China market with the assistance of our valued partners at Broadex,” stated Jeremy Dietz, VP of Global Sales and Marketing at Kaiam. “The two companies will combine on business growth activities in and around China to strengthen Kaiam and Broadex’s market share in optical transceivers for data centres as well as PLCs for 5G rollouts.

“The MOU includes details of mutual technology cooperation and manufacturing arrangements on timeline, cost roadmap, local sourcing and China market development.”

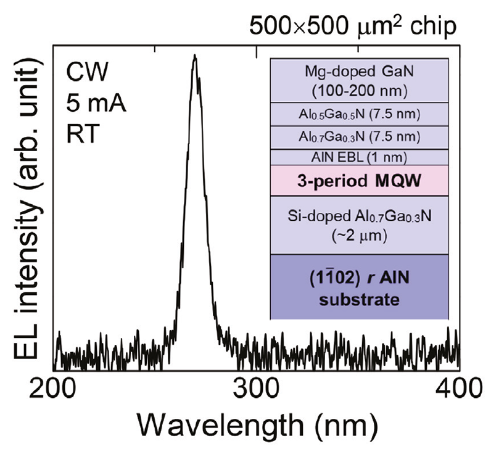

UV-Optical sources start-up Bolb, based in Livermore, California, has announced a new line of ultraviolet C-band light-emitting diodes (UVC LED) featuring record single-chip performance for universal disinfection.

For the past two decades, researchers have been stymied by the light-absorbing hole-supplier layer in the device structure of a UVC LED. Attempts at removing this narrow bandgap layer always lead to a significantly degraded current voltage performance, which translates to higher heat generation and shorter device lifetimes. Bolb says its new LEDs featuring the UVC-transparent holesupplying layer do not suffer any voltage tradeoff. This means its packaged LEDs can simultaneously achieve 12.2 percent EQE and 9.5 percent wall-plug efficiency (WPE). For example, 10~11 mW of UVC power can be obtained from a single 0.5 mm by 0.25 mm LED when driving at 20 mA forward current from production LEDs, while maintaining a 5.8 V forward voltage, at an optimised disinfection wavelength of 265 nm to 275 nm. Such a single chip performance is claimed to be to five times that of the competitors’ offerings at similar wavelengths. Unprecedented performance can be achieved with arrays of such emitters, or a single larger emitter designed for higher drive currents according to the company.

The development paves the way for UVC LEDs to achieve efficiencies approaching that of visible LEDs within the next few years, and enables wideranging applications in hospitals, restaurants, packaging plants, agriculture and homes.

At PCIM Europe, GaN Systems unveiled two wireless power amplifiers for the wireless charging market for highpower consumer, industrial, and transport applications. These new solutions include the 100 W power amplifier with ranges from 70 W to 100 W and the 300 W power amplifier with ranges from 150 W to 1 kW.

The 100 W power amplifier [GSWP100WEVBPA] is for applications in the consumer market for items such as laptop computers, recreation drones, domestic aide robots, power tools, and fast-charging of multiple smart phones. The 300 W power amplifier [GSWP300WEVBPA] is targeted for the industrial and transportation markets for applications that include delivery drones, warehousing robots, medical units, factory automation, contractor power tools, eBikes, and scooters.

Both power amplifiers have a range of features including current or voltage control, built-in protection circuitry, EMI filtering, and configurable output power. The amplifiers combine GaN Systems power transistors with high frequency GaN E-HEMT drivers from pSemi.

“Our GaN solutions are creating opportunities for the development of high-power, high efficiency power systems in applications such as wireless power transfer and charging,” stated Paul Wiener, VP, strategic marketing for GaN Systems. “The power ecosystem has changed. There is now availability of high dv/dt level-shifters, fast response IC sensing and control, low-loss high frequency magnetics, and high performing GaN transistor and amplifier capabilities that are enabling smaller, lighter, lower cost, and more efficient power systems.”

At PCIM Europe, GaN Systems unveiled two wireless power amplifiers for the wireless charging market for highpower consumer, industrial, and transport applications. These new solutions include the 100 W power amplifier with ranges from 70 W to 100 W and the 300 W power amplifier with ranges from 150 W to 1 kW.

The 100 W power amplifier [GSWP100WEVBPA] is for applications in the consumer market for items such as laptop computers, recreation drones, domestic aide robots, power tools, and fast-charging of multiple smart phones. The 300 W power amplifier [GSWP300WEVBPA] is targeted for the industrial and transportation markets for applications that include delivery drones, warehousing robots, medical units, factory automation, contractor power tools, eBikes, and scooters.

Both power amplifiers have a range of features including current or voltage control, built-in protection circuitry, EMI filtering, and configurable output power. The amplifiers combine GaN Systems power transistors with high frequency GaN E-HEMT drivers from pSemi.

“Our GaN solutions are creating opportunities for the development of high-power, high efficiency power systems in applications such as wireless power transfer and charging,” stated Paul Wiener, VP, strategic marketing for GaN Systems. “The power ecosystem has changed. There is now availability of high dv/dt level-shifters, fast response IC sensing and control, low-loss high frequency magnetics, and high performing GaN transistor and amplifier capabilities that are enabling smaller, lighter, lower cost, and more efficient power systems.”

At IMS 2018, NXP introduced new RF GaN wideband power transistors and also expanding its Airfast third-generation silicon-LDMOS portfolio of macro and outdoor small cell solutions for 5G.

The new GaN offerings include the A3G22H400-04S wideband power transistor suited for 40 W base stations. It yields up to 56.5 percent efficiency and 15.4 dB of gain and covers cellular bands from 1800 MHz to 2200 MHz. There is also the A3G35H100-04S GaN transistor providing 43.8 percent efficiency and 14 dB of gain. This device enables 16 TX MIMO solutions at 3.5 GHz.

Silicon-LDMOS products include the A3T18H400W23S, a 1.8 GHz device with Doherty efficiency up to 53.4 percent and gain of 17.1 dB. And the A3T21H456W23S, covering the full 90 MHz band from 2.11 GHz to 2.2 GHz. There is also the A3I20D040WN ultra-wideband LDMOS chip offers peak power of 46.5 dBm with 365 MHz wideband class AB performance of 32 dB of gain, 18 percent efficiency at 10 dB OBO. Finally, the A2I09VD030N has peak power of 46 dBm with class AB performance of 34.5 dB gain, 20 percent efficiency at 10 dB OBO.

The RF bandwidth for this product is 575 MHz to 960 MHz.

NXP says that the breadth of its range of RF power technologies – which include GaN, silicon-LDMOS, SiGe, and GaAs – allows product options for 5G that span frequency and power spectrums with varying levels of integration.

Exagan has delivered GaN-on-silicon transistors and switching systems for pocket-sized fast chargers. Rebecca Pool reports.

As the dust settles on this year’s PCIM Europe, myriad power electronics companies are taking home a vast array of GaN-based devices.

For example, GaN Systems showcased 100 V and 650 V GaN E-HEMTs, Transphorm unveiled 650 V GaN FETs while EPC demonstrated its low-voltage enhanced-mode GaN FETs, targeting automotive, power supply and data centre applications, and more.

At the same time, France-based Exagan, also a key power electronics player, launched its 650 V G-FET power transistor alongside an integrated driver and transistor switching system, G-DRIVE, aimed at fast charger markets.

Described as being easy to design into electronic systems, the products are compliant with the USB power delivery 3.0 type C standard. And as Exagan president and chief executive, Frédéric Dupont, puts it: “The market potential here is enormous, including portable electronic devices as well as homes, restaurants, hotels, airports, automobiles and more.”

“In the near future, users will be able to quickly charge their devices by plugging a standard USB cable into a small, generic mobile charger,” he adds.

G-GET and G-DRIVE products produce by Exagan are aimed at fast charging markets

Since spinning out of CEA-Leti and Soitec in 2014, Exagan has firmly focused on developing 650 V GaNon-silicon products for photovoltaic, automotive and PC markets and more. So why focus on the charging market right now?

According to Dupont, silicon power devices simply cannot fulfil fast charging applications, opening the door to GaN-based systems. But moreover, the chief executive reckons his company can deliver more intelligent and cost-effective GaN device solutions for this application.

“This is a place where GaN can really have a play, but the challenge is the cost and providing a complete solution – this is why you won’t see many GaN players addressing this segment,” he says. “However, Exagan can bring a lot of value here in the short-term.” Indeed, thanks to a rich heritage of heteroepitaxy development from France-based CNRS-CRHEA, CEALeti, and Soitec, Exagan has been ahead of the pack on production, and consequent costs, from word go.

Indeed, thanks to a rich heritage of heteroepitaxy development from France-based CNRS-CRHEA, CEALeti, and Soitec, Exagan has been ahead of the pack on production, and consequent costs, from word go.

During processing, a stack of buffer, insulating and strain management layers is deposited between the silicon substrate and GaN epi-layers to relieve crystal stresses and prevent cracking.

As a result, Exagan has been able to take GaN-onsilicon FET fabrication to larger wafer sizes, focusing on 200 mm production at X-Fab’s CMOS foundry in Germany, as many other GaN players grapple with smaller, 150 mm wafer sizes.

“Most companies are at six inches today but we have been working at eight inch, which is a good size for GaN,” points out Dupont. “This is important for costs, as most of the silicon power electronics market is currently being manufactured at eight inch... and we are using the same 200 millimetre CMOS infrastructure and equipment.”

“In the future we will see some silicon power devices moving to twelve inches but we think GaN will stick with eight inches,” he adds. “I don’t want to say forever but certainly for a long time as the cost structure is already very competitive.”

Costs aside, Dupont is also certain that GaN-based systems are ideal for fast charging applications. As he points out, heteroepitaxial devices, such as GaN-onsilicon FETs, are fabricated as lateral devices.

“Compared to vertical SiC devices, these transistors are suited to integration and co-packaging,” he says. “So while SiC devices are very suitable for high current and high power applications, GaN is a good choice for fast charging applications and, indeed, any application that can benefit from system in package integration.”

“We have always believed that GaN should be approached as a system solution, rather than a transistor solution, this is why we are offering our intelligent GaN Power solutions to the market” he adds.

And for the future, Dupont says Exagan will be focusing on co-packaging silicon driver ICs with GaN transistors to achieve the best combination of cost, performance and functionality, rather than integrating the driver electronics onto the GaN transistor chip to produce a monolithic IC.

“Customers want to have a whole solution, not just a transistor,” says Dupont. “And they also want to know how to drive it, how to control it, how to design a transformer and so on.”

“We have to make sure our products have what a designer needs for a particular application... and many customers want to use an external silicon driver, this is why we developed G-FET,” he adds. “Meanwhile, some customers and applications need a more integrated solution, and this is offered with G-DRIVE.”

Right now, Exagan is sampling and finalizing application development of G-FET and G-DRIVE products with its customers and will ramp production with foundry partner X-Fab according to demand. The company is also working with TÜV NORD’saerospace and electronics arm, HIREX Engineering, on device testing and qualification in a range of applications.

“The power electronics industry has been very conservative about new technologies but wide bandgap materials – both SiC and GaN – are revolutionizing this space,” says Dupont. “I do hope in a few years you will have a small GaN-based charger in your wallet, that can charge your phone, laptop, and anything you want to charge.”

From data centres to automotives, GaN device maker Transphorm eyes more and more applications as market penetration gathers momentum. Rebecca Pool investigates.

Earlier this summer, California-based Transphorm has launched its third generation 650 V GaN FETs, designed for high-voltage power conversion applications.

Targeting industrial, data centre, renewable and power supply applications, the latest devices offer a 4 V threshold – an industry first for GaN FETs and eliminating the need for a negative gate drive – lower electromagnetic interference and reduced device price.

The latest move builds on a series of critical developments from the company. Transphorm released JEDEC-qualified GaN FETs in late 2016, swiftly following this up with automotive-qualified GaN FETs in March 2017. These were targeting on-board charger and DC-to-DC systems applications in plug-in hybrid and battery electric vehicles.

By May 2017, Transphorm’s 650 V GaN FETs had been integrated to 3 kW AC-DC power supplies from US-based Bel Power Solutions, designed for enterprise reliability server, router and network switching subsystems.

And only months later, Yaskawa Electric was using Transphorm’s 650 V, GaN FETs in its 100 W to 400 W servo motors, designed for the industrial multi-axis automation systems. Yaskawa ploughed some $15 million into Transphorm shortly afterwards, to accelerate GaN product development.

Importantly, earlier this year, Transphorm revealed its GaN FETs are being used in Corsair’s latest power supply unit for gaming applications, as well as Taiwanbased Seasonic Electronics’ high-end power factor correction platform for battery chargers, PCs, servers as well as gaming power supplies.

Past power supply products typically rely on silicon superjunction MOSFETs but by moving to Transphorm’s 650 V GaN-on-silicon FETs, in the typical bridgeless totem-pole power factor correction topology, each company has increased product performance.

For example, Corsair has raised its power supply AC to DC efficiency by about 2 percent to more than 99.4 percent. Meanwhile, the switch from silicon to GaN also increased the power output to 1600 W, some 6.5 percent higher than the previous product generation. Enclosure size was also reduced by 11 percent.

Similarly, Seasonic’s move from a silicon-based platform to one that integrates Transphorm’s GaN FETs raised platform efficiency by 2 percent to more than 99 percent while increasing power density by a hefty 20 percent.

As Philip Zuk, Vice President of Technical Marketing at Transphorm, points out: “Corsair’s power supply is now very, very difficult to buy. The company has seen huge demand for the product from the gaming community and it’s also being used in the supercomputers [that drive] cryptocurrency mining and artificial intelligence applications, which are real power hogs.”

Steps to success

Clearly being in production with Yaskawa, Bel Power, Corsair and now Seasonic, has raised the profile of Transphorm’s GaN FETs. According to Zuk: “This is big news for us... and now, production really is starting to ramp.”

The Transphorm Vice President is keen to point out the development advantages of having products ‘in the field’. As he highlights, the company owns each stage of FET development, and insight gained during customer projects can be applied to its GaN-onsilicon technology to raise FET quality, reliability and performance.

Indeed, Zuk also reckons his company’s transition from first to third generation platform – accompanied by developments in packaging, increases in yield and reductions in die size – has cut costs by some 35 percent.

Importantly, the resulting rising demand for the GaN FETs doesn’t stop with gaming and other niche applications. According to Zuk, the company is now seeing traction from data centres, desperate for efficient power supplies that will help reduce power consumption. He also expects automotive interest will follow.

“Our near-term revenue is being driven by the early adopters, gaming, artificial intelligence, crypto-mining and data centres,” he says. “But ultimately, these niche opportunities will roll-out into less price elastic applications, such as automotive applications, including onboard charging, inverters and DC-to-AC conversion.”

“Indeed, a nice thing about being in production is the actual failure in time [data] we can get, which a lot of automotive customers are looking for,” he adds.

Crucially, Zuk is adamant that Transphorm can scale wafer production alongside rising demand. The company has reactors at sites in Goleta, California, and Aizu, Japan, and anticipates that 6-inch production can boost today’s capacity of 5 million to 10 million parts per year to more than 50 million parts per year by 2020. What’s more, the company has 8-inch production in R&D, and is ready to transition to the larger wafer size with market demand.

Transphorm has facilities to put its GaN FETs through their paces.

“If we suddenly had to build 50 million parts then that’s a nice challenge to have and we definitely have the capability to ramp to this,” assures Zuk.

Production aside, Zuk is also seeing some technology issues being swept aside. Transphorm’s FETs are based on the so-called cascode topology and from word-go, Zuk has been busy educating industry on the pros and cons of this transistor type versus the alternative enhanced-mode device. “This has been an uphill battle as many [design engineers] have wanted to use e-mode [devices] but I am seeing that barrier come down now,” he says.

Competition from rival technology, SiC, is also key. Rohm and Wolfspeed deliver 650 V SiC MOSFETs, for example, and as Zuk points out, diodes based on this wideband gap material have been in the marketplace for nearly two decades.

However, design engineer reticence on GaN is now dwindling, and this can only propel GaN further into the market. “My competition is not other GaN suppliers, it is silicon carbide, and what has stopped GaN from being more quickly adopted is uneasiness,” highlights Zuk. “But customers have now multiple GaN projects in development and are over this fear-factor.”

Looking to the future, Zuk is confident that silicon, SiC and GaN will co-exist, with decisions largely relying on price pressures and what the customer knows to design in.

Transphorm’s near-term revenue is being driven by gaming, artificial intelligence, crypto-mining and data centres

Better optics, brighter beams and a higher throughput are propelling cathodoluminescence from the lab to the fab by Jean Berney from Attolight

Our industry prides itself on the production of countless high-quality, reliable devices, which can be degraded at the nanoscale by threading dislocations, stacking faults, inclusions and point defects. Often these imperfections arise during the epitaxial process, due to differences in the lattice or thermal expansion coefficients between the substrate and subsequent layers. However, they can go unnoticed until the end of the line, or even appear in shipped product, where they pose a serious threat to the device’s capability and reliability.

If unnoticed, a killer defect can turn out to be incredibly costly. It is not just the expense associated with undertaking unnecessary production steps on a chip that is destined for failure. The cause of the defect may also need tracing – and when it is exposed, it can reveal a drift in the manufacturing process, and a need to scrap much material. There is also the worst case scenario: chips fail in the field, resulting in angry customers that take their business elsewhere; and the need for expensive failure analysis.

What’s needed is a reproducible, non-destructive defect inspection method that is fast enough for use in production. And at Attolight of Lausanne, Switzerland, we have a cathodoluminescence tool that does just that, the Säntis 300.

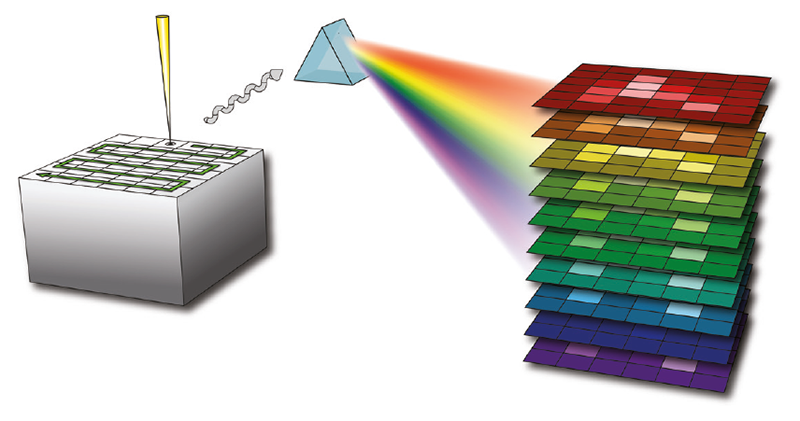

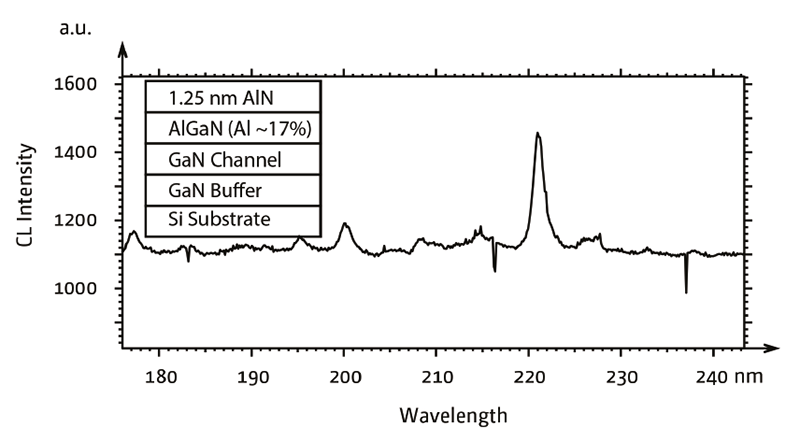

Cathodoluminescence is a characterisation technique that involves directing a beam of electrons at a sample, and recording the light that is emitted from it. Much can be resolved, because the electron beam can be focused down to a few nanometres. This allows a sample to be mapped with nanometre resolution, beating light’s diffraction limit by several orders of magnitude. What’s more, cathodoluminescence can be spectrally resolved, offering tremendous insight into material properties (see Figure 1).

Cathodoluminescence is even capable of detecting threading dislocations, a defect responsible for short circuits in power transistors. This may raise a few eyebrows, given that a threading dislocation has a diameter of an atom, and normally it cannot be resolved by an electron probe that is one or two orders of magnitude larger. But cathodoluminescence offers unparalleled sensitivity to defects, due to the light emission process.

In the cathodoluminescence process, electrons that hit the surface subsequently impinge on the semiconductor, slow down and undergo multiple scattering events. Every time there is scattering, electrons within the semiconductor are excited from the valence band to the conduction band to form electron-hole pairs. These pairs eventually recombine, emitting photons in the visible range.

As the cathodoluminescence emission spectrum is directly related to the difference in energy between the valence and conduction bands, it is extremely sensitive to the electronic band structure – and ultimately extremely sensitive to any atomic change or atomic defect. A mere vacancy or dopant inclusion can disrupt the material’s band structure over length scales up to tens of nanometres. Consequently, even though a defect may be far smaller than the electron probe, it affects cathodoluminescence over tens of nanometres, and its presence can easily be detected with a state-of-the-art cathodoluminescence scanning electron microscope.

The emission energy of the cathodoluminescence depends on the nature of stacking faults, local strain variations and point defects, such as dopant inclusions or vacancies. Threading dislocations act as non-radiative recombination centres, quenching cathodoluminescence. Defect sensitivity can be as good as 1016 atoms cm-3, making this, to our knowledge, the most sensitive non-destructive method for uncovering defects.

It is easy to see why cathodoluminescence’s high sensitivity to defects makes it a great technique for performing failure analysis and R&D characterization. However, in a high-volume manufacturing environment, how can it be practical to sample a full wafer every ten nanometres? The good news is that it doesn’t have to be this way, thanks to cathodoluminescence’s greatest weakness becoming its advantage: carrier diffusion.

Figure 1. Acquisition of a cathodoluminescence map. The electron beam scans the surface of a wafer. At each point, light is emitted, spectrally resolved so that a hyperspectral map (a map made of multiple colours) is measured.

Carrier diffusion: a curse to a blessing

When electron-hole pairs recombine at the place of generation, cathodoluminescence stems from the precise location of the focused probe. But in a defect-free semiconductor that’s not always the case, as electron-hole pairs can diffuse over hundreds of nanometres before recombining.

At first glance, that suggests that electron-hole pair diffusion reduces the image resolution. But that’s not the case.

Consider a killer defect, such as a threading dislocation. The defect disrupts the local electric field, and traps electron-hole pairs that are nearby. As these pairs cannot diffuse or recombine radiatively, local cathodoluminescence is quenched. For electron-hole pairs generated further from the defect, the chances of diffusing towards it are far less, making radiative recombination more likely. Due to these factors, defects appear in cathodoluminescence images as very small dark spots, limited by the probe size and interaction volume, that fade away over a few hundreds of nanometres.

Sometimes defects may radiate. However, they will always modify the carrier wave function in their vicinity, and provide a distinctive cathodoluminescence spectrum. This may be used to identify a defect or a population of defects, even if they have an atomic size.

Note that a map can even be acquired by spacing out measurement points by hundreds of nanometres. So long as the spacing between measurement points is smaller than the diffusion length, the mapping technique will uncover defects. It is this feature that makes cathodoluminescence the ideal low-sampling technique for spotting loosely distributed defects without having to destroy the sample.

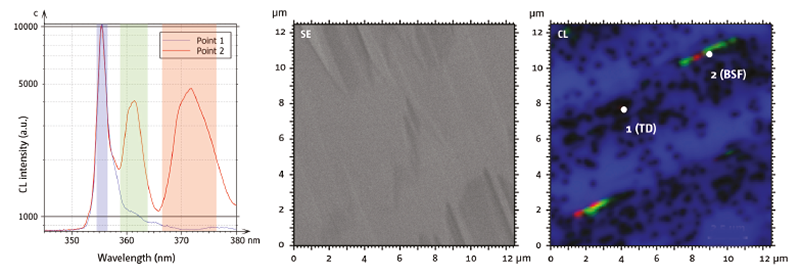

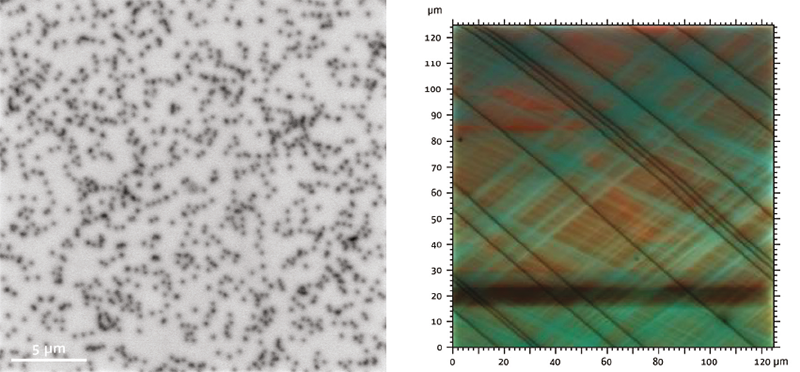

Figure 2. (left) Spectra from point 1 (on a dislocation) and point 2 (stacking fault). (centre) Secondary electron microscope map acquired simultanously to (right) hyperspectral map, having a colour for each defect band. The blue band shows threading dislocations, the green and red band show stacking faults on a GaN template.

A poor reputation

Cathodoluminescence is not a new technique. The phenomenon was first reported as far back as 1879, and cathodoluminescence microscopy has been known since the 1960s. However, use of this technique has been limited to the laboratory, where it has a poor reputation, due to the lack of dedicated instruments.

While collecting cathodoluminescence emitted by the sample is simple in principle, it is not in practice. Difficulties occur, because in the electron microscope that provides the well-defined electron beam, there is competition for the same space by the objective lens of the light and that of the electron microscope.

Up until now, the solution has been to insert a conical mirror, in either a parabolic or elliptical form, into an existing electron microscope.

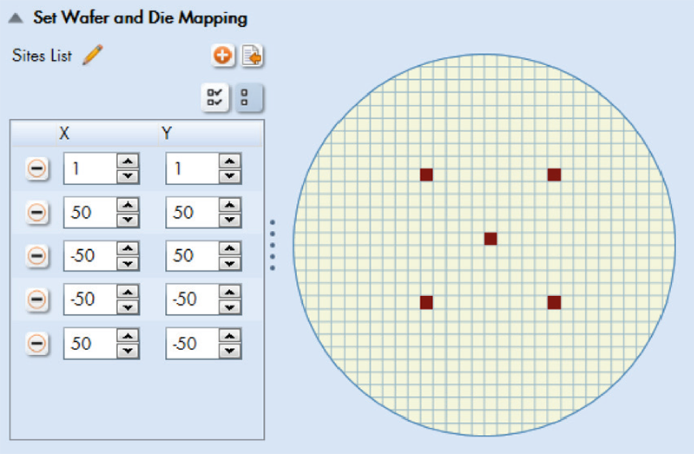

Figure 3. Wafer map showing a wafer with the user defined measurement locations.

One of the many downsides of this approach is that the conical mirror exhibits significant off-axis aberrations, impairing imaging when the wafer is probed anywhere except at the exact focal point of the mirror. Aberrations are so significant that light emitted from the edges of the cathodoluminescence map hits the aperture stop, so it is clipped before reaching the detector – a measurement artefact called vignetting.

Additional drawbacks are that: secondary electron detection is affected by the mirror, making it hard to reach the microscope’s ultimate resolution; and electron microscopes are not designed to work at the optimal conditions for cathodoluminescence, which are a low beam energy and a high current. Instead, a high electron beam current is often traded for a very high resolution at low current.

All these issues have hampered cathodoluminescence, which has a reputation for a lack reproducibility and stability, and lengthy alignment times. These drawbacks motivated us to build the first dedicated cathodoluminescence scanning electron microscope, the Allalin, and its fullwafer counterpart, the Säntis 300.

The latter breaks new ground by bringing cathodoluminescence to high-volume semiconductor production. It has been constructed to produce the highest resolution cathodoluminescence maps possible, and deliver an unprecedented signal-tonoise ratio. Measurement physics, not technology, is the tool’s ultimate limit.

Fantastic features

One of the key features of the Säntis 300 is its entirely new cathodoluminescence collection objective, which has zero off-axis aberration and zero photon loss – allowing for perfectly uniform, reproducible, and quantitative measurements with the highest possible collection efficiency. This approach eliminates alignment time and maximises the signal-to-noise ratio to its physical limit – no matter where the electron probe is placed.

Another attribute of our tool is its state-of-the-art field emission gun technology. The advanced gun trims aberrations by a factor of three and produces higher brightness. A higher probe current is used without compromising resolution. This helps us to dramatically improve the signal-to-noise ratio, speeding cathodoluminescence measurements of weakly emitting specimen, and in some cases making it possible to image a sample.

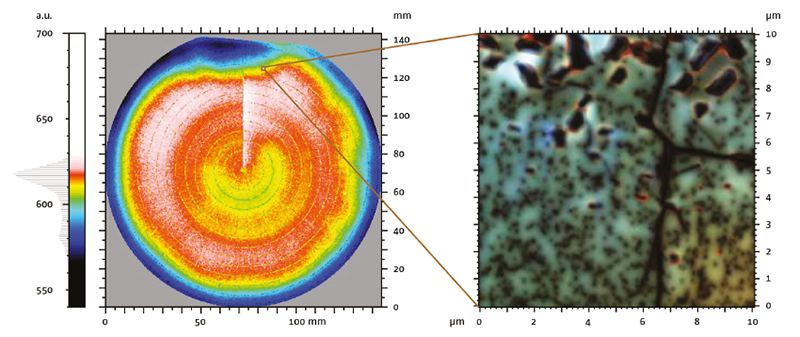

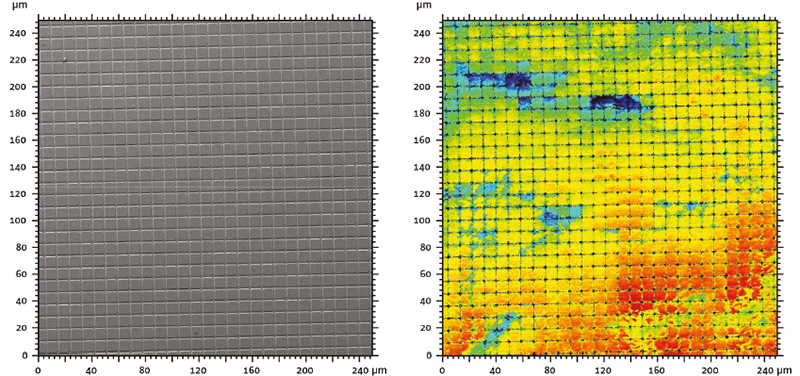

Figure 4. Full-wafer brush image of a 150 mm LED wafer (left) and red-green-blue cathodoluminescence map representation (right).

One of the potential pitfalls of a high brightness gun is that it can introduce unwanted electron-electron interactions. To prevent this, we use a very simple, elegant design that ensures electrons are separated from one another at the source, and don’t interact as they travel to the sample.

We also employ an electron microscope objective lens that leaves a large opening, to allow the inclusion of a high-numerical-aperture light microscope that collects as much light as possible. Our tool is designed so that the optimum focal plane of the electron microscope matches the focal plane of the light microscope. With this approach the user can always work with the smallest probe size.

To realise mapping with sub-micrometre resolution, the beam energy in a cathodoluminescence tool must be below 10 keV. We adhere to this requirement, optimising the objective lens of the electron microscope to deliver a massive electron beam current in the 3 keV to 10 keV range. This is accomplished while maintaining a probe size below 10 nm, to ensure that it takes very little time for users to produce highresolution cathodoluminescence maps.

Figure 5. (left) Dark spots corresponds to threading dislocations on a GaN template. (right) Lines represent stacking faults, the dark spot close to the centre is a threading dislocation on SiC.

When we set out to design a quantitative cathodoluminescence detector, one of our primary goals was to maintain the high collection efficiency and spectral resolution when steering electrons away from the optical axis. To accomplish this, we designed a high numerical aperture reflective objective that is optimized to fit in an electron magnetic lens and excel on three fronts: in achromatism, ensuring freedom from colour-related distortion; in aplanatism, to eradicate image distortion; and in thermal characteristics, so that the objective is stable with regard to temperature changes.

Another attribute of this reflective objective is that it avoids the tiny aperture stop, which standard systems use to achieve high spectral resolution at the expense of low light throughput and vignetting.

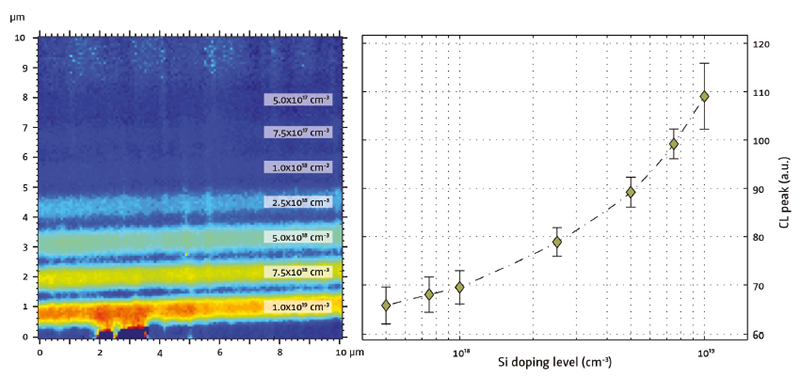

Figure 6. (right ) Graph showing changing silicon-dopant concentration in a staircase GaN structure measured with high precision using cathodoluminescence. In addition, the precise positioning of the electron beam allows to extract optical signatures of small sized areas within a device, non-destructively in top view, or on cross sectioned samples. (left) CL map of the staircase structure.

Thanks to its great design, the Säntis 300 can produce cathodoluminescence intensity maps at a rate of 100 ns per pixel, while realising a dynamic contrast of two-tothree orders of magnitude with materials with adequate emission efficiency, such as III-Vs with a direct band gap. This throughput is sufficient for characterising layers in a high-volume semiconductor fab.

It is worth noting that the Santis 300 system is capable of more than just cathodoluminescence. In its most powerful configuration, it also offers: scanning electron microscopy imaging; UV-visible and nearinfrared hyperspectral imaging, including an individual pixel optical signature; and panchromatic fast imaging (see Figure 2 and 8 for simultaneous scanning electron microscopy imaging and hyperspectral imaging).

Figure 7. Cathodoluminescence spectrum of 1.25 nm thick AlN etch stop layer. The Säntis 300 is UV capable and sensitive enough to measure spectral signatures over very thin layers that emit photons in the UV spectral range.

Modes of operation

Another feature of the Säntis 300 is its three acquisition modes: step and repeat, across wafer pixel, and full wafer brush.

The step and repeat mode is the one that is most likely to be used in a high-volume fab for non-destructive control of buried defects. When the tool operates in this mode, the user specifies a wafer map by predetermining a list of measurement locations (as shown in Figure 3) that will be investigated and specifies acquisition parameters. The tool then sequentially loads wafers, focuses the electron beam onto them and acquires, simultaneously, secondary-electron and cathodoluminescence maps at each measurement location. Wafers are repeatedly characterized, allowing statistical process control at the highest possible spatial resolution for characteristics such as the distribution of defects, their size, and their spectral signature.

If engineers need to carry out in-depth analysis, they can produce hyperspectral cathodoluminescence maps from wavelengths as short as 200 nm in the UV to 1700 nm in the mid-infrared, using over a thousand channels – or colours – per pixel. Alternatively, they can acquire fast single-channel maps.

Running in the across wafer mode, the Säntis 300 operates with a medium electron-beam spotsize and produces cathodoluminescence intensity maps of full wafers or partial areas of wafers. Operating in this manner takes full advantage of optical signature acquisition. Variations of material across the substrate can be detected. Two hours are needed to map a 150 mm wafer, and partial scanning is proportionally faster.

Engineers will primarily use the across wafer mode for non-destructive process development. This includes efforts at yield improvement, which target uniformity characterization. Studies are related to the likes of buried defect density and impurity variations. Success that results from this approach includes faster development cycles and shorter ramping times.

Operation in the third mode, full-wafer brush, involves defocusing the electron probe and measuring the whole wafer with a low spatial resolution – it is 300 μm. Full 150 mm wafers can be measured in about 13 minutes. This approach generates a massive hyperspectral map of the wafer, enabling a measurement of the variation of material composition across the substrate (see Figure 4).

One of the powerful features of the full wafer brush mode is that it allows an engineer to set upper and lower control limits on the input signal – this enables automatic identification of step-and-repeat locations, which require high-resolution characterization. Operated in this manner, the statistical process control of the Säntis 300 can be extended from optical characteristics and image analysis to X-Y location acquisition coordinates. This allows process profile wafer mapping to be inferred and used as an additional parameter for non-destructive production control, with a fast feedback loop to the process tool.

A versatile tool

As defects are an issue for the production of any device, our Säntis 300 can make a valuable contribution in fabs that are manufacturing LED, microLEDs, SiC and GaN power and RF chips, photovoltaics, and III-V photonics. For all these devices, substrates and epitaxial layers are the base of the pyramid on which devices are built. It is challenging to detect sub-surface defects with nanometre resolution on substrates with diameters up to 300 mm, but the Säntis 300 is up to the task: it can specifically recognize, isolate and quantify most of the defects of interest, including buried defects.

Figure 8. Intermediate process check. (left) Secondary electron map measured simoultanously to (right) hyperspectral cathodoluminescence map showing wavelength shifts over more than 700 microLED structrures.

Our tool is capable of rapid measurements and automatic counting of threading dislocations in a GaN or SiC blanket layer, for densities up to 5 x 109 cm-2. In the example shown in Figure 5, 882 dislocations are identified in a scan area of 25 μm by 25 μm, corresponding to a density of 3 x 108 cm-2.

Even if a layer does not emit light, it might absorb light coming from sublayers and could be indirectly observed this way. This issue can be addressed by cathodoluminescence mapping where the Säntis 300 provides pinhole detection of a non-luminescent layer on top of a luminescent layer.

The optical signature returned by cathodoluminescence is heavily influenced by the type of impurity, and by the level of doping or the impurities in a material. However, characterisation of doped areas is possible with the Säntis 300, according to cross-correlation studies with other techniques, such as secondaryion mass spectrometry (see Figure 6, variations in the emission peak can directly be correlated with the doping concentration. The silicon-dopant concentration can be inferred with high precision).

Thanks to the precise positioning of the electron beam, optical signatures can be taken from smallsized areas within a device. This can be a top-view, or if destruction of the sample is permitted, a profile of the cross-section.

Plasma etching plays its part in the manufacture of many devices. Unfortunately, it can introduce defects on landing layers or impurity loading on a sidewall. These imperfections can be picked up with the Säntis 300, which can also assess the integrity of an etch stop layer (see Figure 7).

One of the most challenging devices to characterise is the micro-structured LED array. That’s because conventional optical methods have insufficient resolution. What’s more, a series of process steps produce a structure that is influenced by interactions that cannot be accounted for during the characterization of a particular step.

Addressing these issues is the Säntis 300, which can perform the critical intermediate process checks. In addition, it allows engineers to determine process uniformity over large fields with high spatial resolution – this holds the key to yield improvement and faster process development (see Figure 8 for an example of imaging microLEDs with the Säntis 300).

For emitting devices, such as LED and lasers, a full wafer scan can be performed using pre or post singularizing of the dies. During this measurement, undertaken at either room temperature or at the functioning temperature of the device, the electron beam activates the device, while optical collection fully characterizes the wavelength, intensity and other parameters of interest. Adopting this approach allows rapid sorting of the die.

Our examples of the use of the Säntis 300 offer an insight into the versatility and importance of quantitative cathodoluminescence. We believe that the launch of this tool promises to revolutionise material characterisation in compound semiconductor fabs all over the world.

Technavio’s analyst for research on lighting, Sunil Kumar Singh, argues that LED chipmakers are not finding it easy due to overcapacity, thin margins and partial commoditisation of the device interview by Richard Stevenson

Q - Is the LED now a commodity market?

A - LED lighting is becoming a commodity. For street lighting applications, or LED light bulbs that are replacing conventional lighting sources, there is a little commoditisation. But for backlighting applications, for automotive, this is not a commodity market right now.

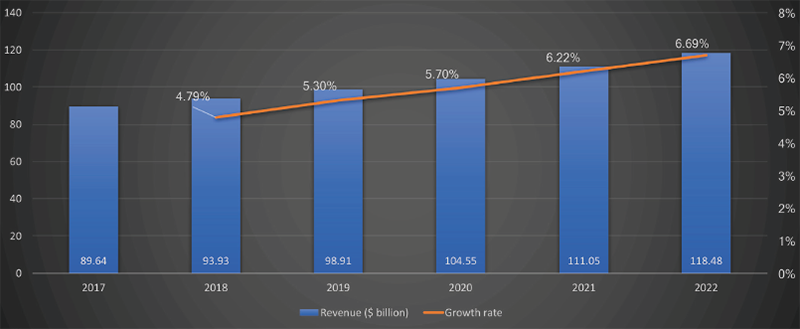

Q - What is the LED market worth today, and how will it evolve in the coming years?

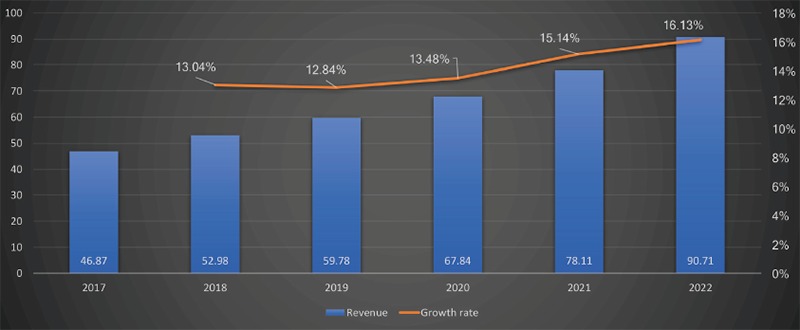

A - The LED market is growing at less than ten percent, and the current valuation is $25 billion to $30 billion. There are three major applications: one is [general] lighting, the second is automotive lighting, and the third is backlighting.

The general lighting market includes LED replacement of conventional lighting sources and street lighting. These are growing. This is why the trajectory of the LED market is growing at a little over ten percent.

The valuation of the LED lighting market is close to $45 billion to $47 billion, and the overall general lighting market is over $90 billion. So the proportion of LED lighting is more than 50 percent of the overall revenue generated. But this proportion will go up from 50 percent to 60 to 62 percent post 2020, and by 2025 it will contribute 80 to 85 percent. So this is a good trajectory for LEDs.

LED penetration in automotive is increasing, as many of the mid-range automobiles are also integrating LEDs for interior and exterior lighting.

The display industry is growing at a slower pace, and backlighting, because of the reduction in the selling price, has actually declined. Sales of portable PCs are declining, and large-area displays are also declining. Demand from emerging applications such as video walls and digital signage is expected to contribute to the backlighting market. However, the volume shipped for these emerging applications will not be very high.

The majority of low-cost devices are [deployed in] a standard back-lighting unit. They have LEDs, but the volume shipped is getting less. So that’s another reason why LED lighting will be a bigger market than backlighting.

We have ultra-high definition TVs coming, and Samsung is getting out of the OLED market and manufacturing quantum dot TVs, so some are saying that the backlighting market may grow. But there is still a decline in the average selling price of the devices.

Q - What are the emerging applications?

A - Horticultural lighting is one of the areas. We also have applications such as LED light strips – that market is gaining good growth. And we have architectural lighting, which has been one of the contributing sectors of the LED industry for much time. But there is still a lot that is happening in this space.

There are also LED wallpapers, portable lighting and LED watches. There is also accent lighting, and LEDs used with IoT devices.

Q - There was a time when ‘the big five’ ruled the LED market. How would you describe the current fortunes of Nichia, Toyoda Gosei, Cree, Lumileds and Osram?

A - When it comes to companies like Toyoda Gosei, Cree, Osram, and Nichia, they are big vendors. It’s just that LEDs used to be manufactured by very few vendors, and now they are manufactured by many vendors.

Now we have LED lighting vendors such as Philips, GE Lighting, Stanley Lighting, Acuity Brands Lighting, Hella, Zumtobel Group, Eaton, Everlight, Seoul Semiconductor, Innotek, Kyocera, Bridgelux and Dialight. Some of these are renowned names in the LED lighting industry, and some of them also have end-to-end solutions of LEDs, right from LED chips to various LED lighting products manufactured in-house.

For lighting, the chip design and the chip making are not the final products – the final product is the LED luminaire. So the success in these particular industries depends on how well one can control the overall value chain of the industry. So a company that has big chip manufacturing and limited customers is finding it tough against a company that is manufacturing the chip and the final product.

At one time Cree, Nichia, Toyoda Gosei, Lumileds, Osram and Souel Semiconductor had up to 70 to 80 percent market share, but now all these vendors put together have less than 50 percent market share. So we are talking about high fragmentation in this market. But these [big] vendors are operating in all the sections of the market, from manufacturing LEDs to luminaires, so they are controlling their own supply and distribution, and are selling their own lighting products.

Q - These companies devoted much effort to protecting their IP. How important is IP today?

A - IP is very important. But it’s not just to do with the chip design – it can also be the manufacturing process.

The rate of growth in the global general lighting market will pick up slightly over the next five years, according to Technavio.

Q - Is there much to be gained by offering class-leading LEDs today? Or is cost the key?

A - The cost is the main thing. The cost of the product includes that of the LED package, the optics, mechanical/thermal components, assembly, and the LED driver. Of these, the LED driver attracts the highest cost, followed by manufacturing, mechanical/thermal components and others.

For manufacturing, the back-end process contributes more than 50 percent of the overall production cost, followed by the phosphor, substrate, epitaxy, and wafer processing.

The cost of the chip back in 2013 or 2014 was a little above a dollar. There are two factors behind its decline. One is the overcapacity of LED chips, that has forced all vendors to reduce the price; and the other is the manufacturing efficiency.

The cost of an LED chip has gone down to less than $0.60 per unit for LEDs, and close to $0.80 per unit for high-brightness LEDs.

Q - How dominant is China today in LED chip manufacturing?

A - China is dominant when it comes to chip manufacturing. Look at the number of fabs that have been established. Back in 2008, China had close to 28 fabs. In 2016 it was in the range of 70 to 75 fabs, and now it will be even more than that. The total number of fabs in the world is in the range 170 to 180.

Q - Is there much consolidation within China’s LED chipmaking sector?

A - No. There is not much consolidation. Consolidation is happening at a very slow rate. Very small players get acquired or merge. Bigger companies such as Cree and Nichia have acquired small vendors.

Q - Are companies within China making much profit?

A - We studied the LED market in China back in 2016. We looked at two scenarios: whether companies had subsidies from the government; and what would happen after the subsidies went. Since then we have been tracking that market.

When companies had subsidises between 2011 and 2015 – during the twelfth five-year plan, which was directed at energy efficiency, with the government wanting LED companies to be established – profits were close to 8 percent to 10 percent. But, now after the subsidies are over and the companies are on their own to supply chips, profits are reduced to 5 percent to 7 percent, and for some companies 2 percent to 3 percent.

The LED lighting market will deliver double-digit growth over the next few years.

Q - Veeco shipped many of its K465i MOCVD tools to China in 2009 and 2010. Given the overcapacity that followed, and investment in new tools, is there a big market for second-hand MOCVD tools?

A - There was always a demand for Veeco tools in 2009 and 2010. But we are talking about a time for two-inch epitaxy. Now the path, for the majority of investment is four-inch. And after that it’s six-inch.

MOCVD tools from 2009 and 2010 have a life cycle of seven to ten years, depending on the application. So these tools do not have much of a second-hand market. In the 70 to 75 fabs in China, there is no demand.

Q - For sales in China, are Chinese makers of MOCVD tools, such as Amec and Topec, about to overtake Veeco?

A - Amec’s Prismo D-Blue MOCVD platform is gaining popularity among the customer base of LED chipmakers, as it delivers high-volume manufacturing of GaN, InGaN and AlGaN ultrathin layered structures required for highbrightness LEDs. Topec is one of the market participants focusing on developing MOCVD equipment domestically.

The global general lighting market will continue to be dominated by residential and commercial lighting.

Q - What is the most common platform for making LEDs? Is it now 6-inch sapphire?

A - The majority is now 4-inch.

Q - Who are the leading suppliers of sapphire substrates?

A - Some of the companies are Rubicon Technologies, Crystal Applied Technologies, Precision Micro-optics, Monocrystal, Kyocera, Crystalwise Technology, TeraXtal Technology, DK Aztec, Gavish, and Hansol Technics.

Q - How common is the use of patterned sapphire?

A - Patterned sapphire suppliers include Rubicon Technologies, Sinopatt, Jing’An, Rigidtech, ECEC, and Crystal-Optech. Rubicon have their complete product line as patterned sapphire. But there are some other vendors that have a product mix.

The GaN HEMT is now a formidable, mass-produced device, combining great efficiency with excellent reliability and robustness. By Richard Stevenson

If you spend all of your time looking forward it’s easy to lose sight of how far you’ve come.

That’s a trap that many of us can fall into when we are considering the variant of the GaN HEMT that operates in the RF domain. Often, the future is the focus – sales are tipped to rocket to more than a billion dollar per year by the start of the 2020s.

Take that perspective and it’s easy to forget the progress that has been made to date. It is now more than a decade since the launch of the first GaN HEMT operating in the RF, and over that timeframe devices have been deployed in many different applications. And now, revenues are significant. According to market analyst Yole Développement, GaN RF device sales to the military will net $201 million this year, while those for base stations and satellite communications will accrue $150 million and $29 million, respectively.

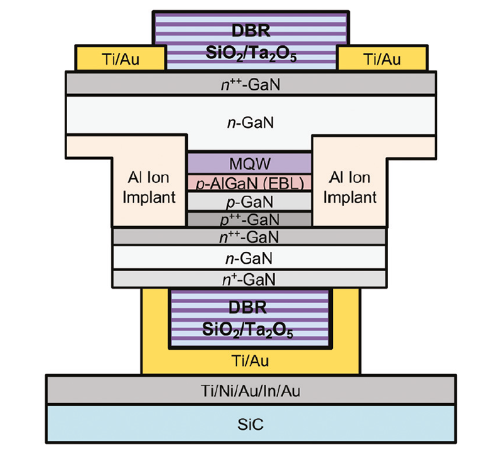

A snapshot of how far the GaN RF industry has come, and the challenges that lie ahead, was provided at this year’s CS Mantech, held at the Hyatt Regency in Austin, TX, from 7-10 May. That meeting featured a session on RF devices that included presentations detailing: the creation of E-mode and D-mode HEMTs, via variations in the form of stress in the device; the development of an efficient 15 W/mm GaN technology for serving pulsed radar in the C-band; improvements to a 0.25 μm process for radar and 5G applications; and opportunities to refine the mass production of high-reliability GaN HEMTs for wireless communication.

The benefits of stress

One of the biggest weaknesses with GaN technology is the lack of truly normally-off enhancement mode and depletion mode integrated devices. Due to the chemical inertness of GaN and its alloys, etching is not easy, and it often leads to an increase in the gate leakage in enhancement-mode devices. An alternative, fluorine implantation, also introduces damage to the semiconductor material, thereby impairing reliability.

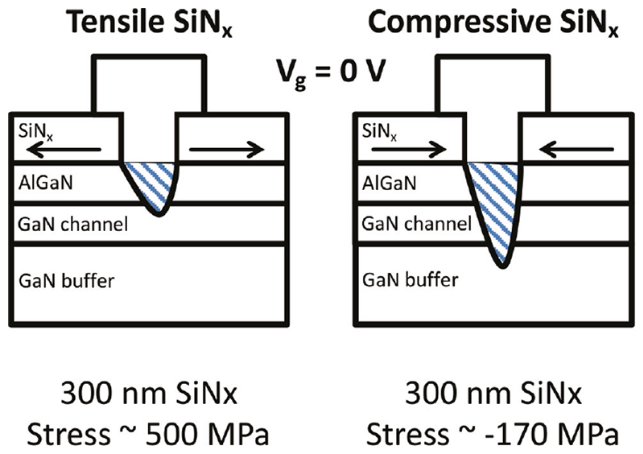

A very promising solution, described by Konstantin Osipov from Ampleon, involves the addition of a SiN passivation layer. This applies stress to the AlGaN barrier – which is under tensile strain due to lattice mismatch – and it ultimately controls the density of the two-dimensional electron gas under the gate region (see Figure 1). Armed with this lever, the team can realise either partial or complete depletion of the transistor channel, and thus fabricate enhancement and depletion mode devices on the same wafer.

According to Osipov, introducing the SiN layer also produces a reduction in the gate leakage current and the elastic energy stored in AlGaN at the drain side of the gate. “So theoretically, [our technology] should lead to significant reliability improvement.”

Development of the technology can be traced back to efforts by Osipov to reduce the gate leakage current with SiN layers with different compositions. This trial revealed that differences in SiN composition led to variations in the threshold voltage.

“I’ve tried to understand the physical reason behind this phenomenon,” explains Osipov. “The only reasonable explanation that I’ve found is internal compression in the silicon nitride layer that is transferred to AlGaN.”

After confirming this assumption with simulations, Osipov went on to create a simulator virtual enhancement-mode device that featured highly compressive SiN. After this, he developed an experimental process for making integrated enhancement-mode and depletion-mode devices.

Figure 1. Adjusting the strain in SiN can lead to depletion in the channel of the GaN HEMT, and a shift in the threshold voltage by more than 1 V.

Note that the use of external stressors is actually a tried and tested technology. “In silicon technology, external stressors are used for electron and hole mobility enhancement, despite the fact that silicon is not even a piezoelectric material,” says Osipov.

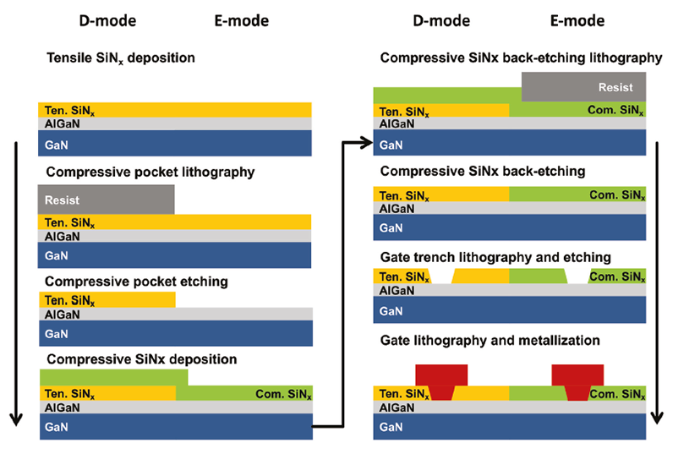

Fabrication of the team’s devices began by loading 4-inch, n-type SiC substrates into an MOCVD reactor and growing an iron-doped buffer layer, an unintentionally doped GaN channel, and a 10 nmthick Al0.26Ga0.74N channel. After adding a Ti/Al metal stack to form ohmic contacts, a 300 nm-thick SiN passivation layer was grown across the whole wafer (see Figure 2(a)).

The next steps involved: using photolithography and etching to open windows in the passivation layer where enhanced-mode HEMTs would be formed; depositing a compressive SiN layer over the whole wafer, before using photolithography and etching to remove this at locations where depletion-mode devices would be added; and then using a sputtering process to compete fabrication of 100 nm gates.

Measurements of DC characteristics revealed that there is a threshold difference of more than 1 V between the enhancement mode and depletion mode devices. For the enhancement mode HEMTs, DC performance is claimed to break new ground, in terms of on-resistance, peak transconductance and gate leakage.

The researchers attribute this success to their technology. One of its merits is that it produces a ‘virtual’ gate recess effect, while maintaining the thickness of the AlGaN barrier. Another virtue is that the sputtered iridium process, developed at FBH, avoids damage to the semiconductor surface during fabrication. Thanks to this, the devices exhibit ideal normally-off behaviour and avoid any trade-off between AlGaN thickness and threshold voltage – that can lead to low parasitic input and output resistances.

Figure 2. The team from Ampleon and FBH Berlin have produced E-mode and D-mode HEMTs side by side with a process that includes the deposition of tensile and compressive layers of SiN.

One weakness of the enhancement-mode devices is that they can be compromised by back etching of the tensile SiN layer. However, this issue can be avoided.

“Technically it’s not a problem to leave a few tens of nanometres of tensile silicon nitride and cover it with a compressive film,” says Osipov. “In this case, compression from the thicker layer will easily overcome the tensile stress of silicon nitride underneath, and the overall stack stress will be compressive.”

The team have made some RF measurements. “The damage from tensile silicon nitride removal negatively influenced RF performance of E-mode transistors,” admits Osipov. However, the cut-off frequency for these devices is still higher than that for depletionmode variants.

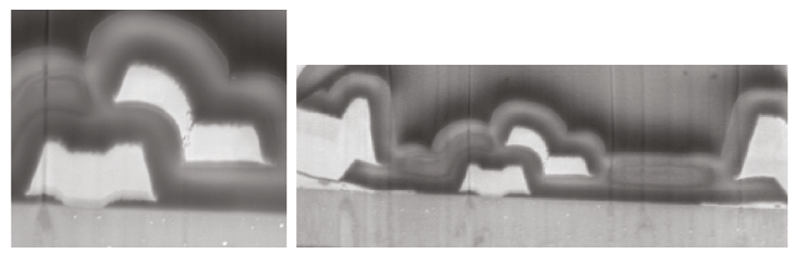

Figure 3. Scanning electron microscopy images of Integra Technologies’ 0.25 μm GaN die design that has a breakdown voltage of more than 250 V.

Empowering pulsed radar

For radar systems used for weather, air traffic and the military, the most desirable attributes for an amplifier are a high output power and a high efficiency. While those made from GaN HEMTs are already delivering a performance that is good enough to serve in many of these applications, there is demand for an even higher efficiency – this could trim the size, weight and power dissipation of the electronics, and lead to smaller, lighter and more efficient systems.

The key figure of merit for the HEMT is its power density, which is the product of its current density and the bias voltage. For AlGaN/GaN HEMTs, for typical bias voltages of 28 V to 50 V, the current density tends to peak at around 1 mA/mm. This can be doubled by switching to more novel material combinations, such as InAlN/GaN, InAlGaN/GaN and N-polar GaN. However, due to the conservative nature of the radar industry, it can take more than ten years to transform a laboratory technology into an approved product. Given that hurdle, there is much to recommend to any approach that offers a shorter path to technology maturity.

At Integra Technologies of El Segundo, California, they are adhering to that view, and using voltages of up to 100 V to increase the power density.

At CS Mantech, company spokesperson Gabriele Formicone provided an update of the company’s latest progress. He argued that two of the most important breakthroughs have been the higher power densities and the higher impedance, aiding broadband matching. However, the pinnacle of the team’s success, according to him, is the realisation of a power density of 15 W/mm at C/X-band, using a production-ready GaN-on-SiC technology. “[This] is much more cost effective compared to alternative approaches, among which is GaN on diamond.”

Migrating to higher voltages will not be an issue in the radar sector, which has traditionally used travelingwave tubes. “100 to 150 volts is still orders of magnitude safer than 10,000 volt traveling-wave tubes supplies,” says Formicone. “Therefore, we do not see any downside in migrating from the nominal 28 volt to 50 volt power supply to 100 volts to 150 volts in high-performance radar, electronic warfare and industrial, scientific and medical applications.”

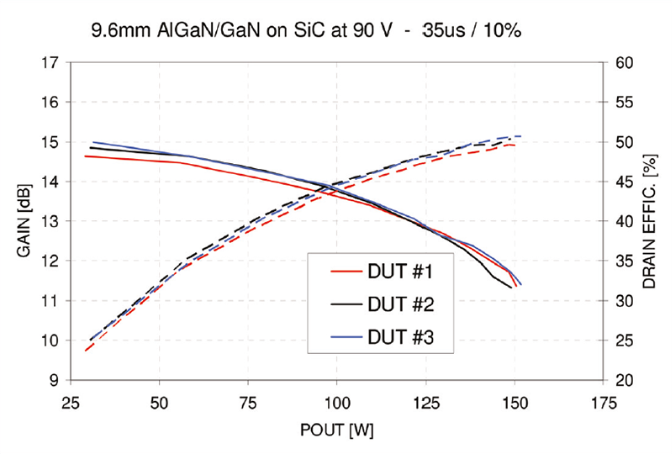

The team’s latest results were obtained with its 0.25 μm GaN-on-SiC HEMT process, which produces devices with a breakdown voltage in excess of 250 V. Chips are housed in a ceramic package, and performance evaluated at 7.9 GHz using 35 μs pulses and a 10 percent duty cycle – these operating conditions are claimed to be of interest in some radar remote sensing applications.

Using a 90 V bias, devices can deliver 150 W with 11 dB of power gain. Operating in this manner, drain efficiency is 50 percent, corresponding to a power-added efficiency of 46 percent. Crank up the voltage to 100 V and there is little improvement in output power, but drain efficiency still exceeds 40 percent.

Figure 4. Measurements were made on three of Integra Technologies’ 9.6 mm GaN-on-SiC HEMTs, operated under 90V bias. Testing took place at 7.9 GHz, using a pulse width of 35 μs and a duty cycle of 10 percent.

The lack of improvement is explained by the 100 V device being a first iteration. “An improved design would show good performance at 100 volts too,” argues Formicone. “Additionally, as voltage increases to 100 volts, load impedance tends towards 50 ohm, which requires a more careful test fixture/circuit design to properly match, given the narrow width of the transmission lines.”

Integra will extend this technology to even higher voltages. Benefits will not be limited to a smaller, lower cost die for a given power level, but will extend to improved broad band matching.

The move to higher voltages should not prove too tricky, as Integra is not heading into uncharted territory – at lower frequencies, it has already produced parts that operate at 150 V and offer efficiencies of 80 percent. “At higher frequency it is always a bit harder,” says Formicone, “but Integra has been pursuing this technology roadmap for a few years already with very interesting results.”

Integra’s AlGaN/GaN X-band FET.

Refining the process

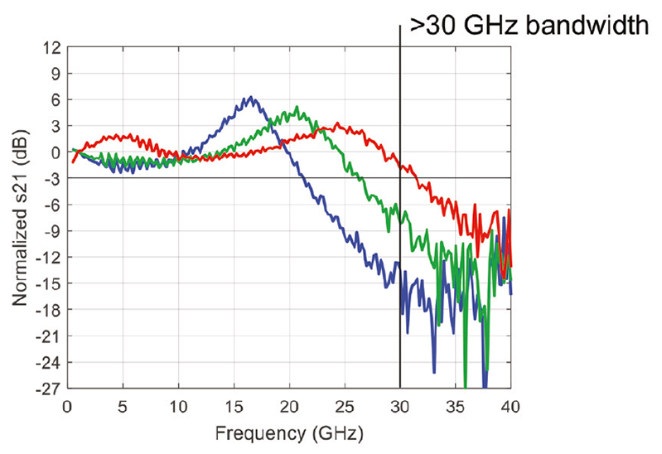

At WIN Semiconductor, efforts have been underway to improve the performance of GaN-on-SiC MMICs fabricated on a dedicated 100 mm line. These devices are targeting radar and 5G applications.Refinements to the company’s 0.25 μm process, described to delegates at CS Mantech by Yi-Wei Lien, have increased small signal gain by 1.8 dB to 20.3 dB and driven up the power-added efficiency at 10 GHz from 59.6 percent to 64.7 percent.

Higher levels of performance are claimed to result from a combination of a superior epitaxial process and optimisation of the processing. Thanks to these advances, there are reductions in gate-lag and drainlag by 25 percent and 11.6 percent, respectively. That’s a big deal, because it implies that there are fewer traps, and ultimately a reduction in the current collapse of the transistors.

GaN MMICs produced with the latest process are also free from a kink-effect that plagued the previous generation. The kinks, seen in DC measurements of the source-drain current as a function of drain-source voltage, are associated with hot electrons – they are trapped at a low drain-source voltage and de-trapped at a higher voltage.

Another improvement in WIN’s technology has been the integration of the RF power amplifier with an RF switch, in the form of a symmetric transistor with a 0.25 μm gate located at the centre of the source-drain region. Testing, using a pulse width of 50 μs and a duty cycle of 10 percent, reveals a rise time of 36 ns and a fall time of 13 ns.

In addition to these impressive switching speeds, the switch is reliable. High-temperature reversebias testing at -50 V and 150 °C reveals that during 1000 hours of operation, the switch’s on-resistance, threshold voltage, and the saturation drain current vary by less than 12 percent.

High-volume manufacturing

From the perspective of Sumitomo Electric Device Innovations, the GaN HEMT is now, without doubt, a device in mass production. At CS Mantech, company spokesman Fumikazu Yamaki emphasised this point by reporting developments in robustness and packaging.

To ensure that a product can offer many years of service, it needs to combine high reliability with a high degree of ruggedness – a capability to cope with operating conditions beyond those that were intended. Yamaki and co-workers have devoted much effort to realising this, evaluating progress in terms of increases in the safe operating area. For a GaN HEMT with an intended drain-source voltage of 50 V at 2.1 GHz, the peak drain voltage during operation can hit 160 V, but the breakdown is still far higher: it is 220 V. Thanks to this margin, it is argued that the device has sufficient ruggedness for mismatched and unexpected load impedances.

Reliability of the company’s HEMTs is also very high, with DC high-temperature operating life tests revealing a mean-time-to-failure of 23 million hours at a channel temperature of 200 °C. Note that in base stations, high power amplifiers may have channel temperature this high.

One recent development at Sumitomo is the housing of devices in plastic packages, which are needed to meet the cost and size requirements associated with 5G. In these packages it is essential to include die level humidity protection. An improved surface passivation film can provide this, according to Sumitomo’s 200 hour tests at 130 °C using relative humidity of 85 percent.

These efforts at Sumitomo underline the progress that has been made with the GaN HEMT. It is a fully fledged commercial device, and with further progress being made by not only this Japanese outfit – but also the likes of Integra, Ampleon and WIN – there is good reason to believe the positive forecasts of the market analysts.

Aspect ratio trapping enables the fabrication of nano-ridge lasers on silicon substrates by Bernardette Kunert, Robert Langer, Marianna Pantouvaki and Joris Van Campenhout from IMEC and Dries Van Thourhout from Ghent University

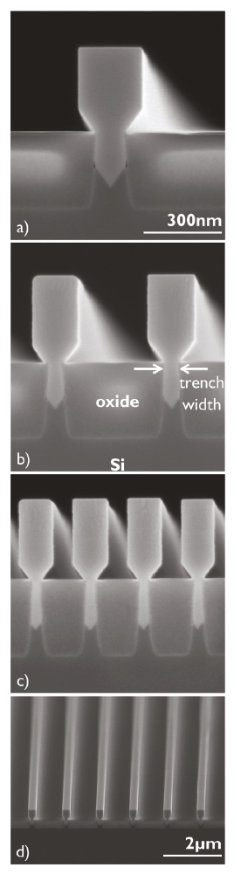

Figure 1. Cross-sectional, scanning electron micrograph images of cleaved GaAs nano-ridges. (a), (b) and (c) show GaAs nano-ridges on top of 100 nm, 40 nm and 20 nm wide oxide trenches, respectively. All structures were deposited in a single growth. (d) a tilted top-view scanning electron micrograph image of an nano-ridge array on top of 100 nm-wide trenches. Some of the images are modified and reprinted from B. Kunert et al. Appl. Phys. Lett. 109 091101 (2016) with the permission of AIP Publishing.