It would be easy to think that CPV is dead and buried. After all, many big names have exited the business in the last few years, including GreenVolts, SolFocus, Semprius and Soitec. And the price of silicon panels prices is now so low that the costs associated with CPV, which involves the focusing of sunlight on III-V cells, will have to be far lower than first anticipated to ensure success.

But there are rays of hope. Since the start of 2017, Soitec’s technology has been in the hands of the Canadian firm STACE, which has announced plans to increase manufacturing capacity for its CPV technology. What’s more, Arzon Solar is keeping Ammonix’s technology alive, Morgan Solar and SunCore are still in this business, and in Europe many firms are involved in a project to develop a new-generation of module that will make CPV more competitive.

The latter effort, detailed at the conference Advances in Concentrator Photovoltaics for Space and Terrestrial Applications, addresses several weaknesses in the design and manufacture of many CPV systems (see p.28 for a report of this meeting).

One issue is that as volumes are low, economies of scale cannot be exploited. But that can be overcome by borrowing technologies developed in the LED industry, to form cells with a secondary optic. And by making these cells small, another issue is addressed: thermal management. Small cells are easier to cool, trimming the bill of materials and the weight, which saves on shipping.

Another lever that can be pulled to improve the competitiveness of CPV is to move to a higher level of concentration. Those in the European project are doing just that, developing a second generation of FullSun module that operates at 1000 suns, rather than 625.

Field trials will take place at the University of Cypress later this year, using modules sporting three different makes of cell: a lattice-matched design from IQE, and inverted metamorphic from Azur Space Solar, and a device from Solar Junction that features a dilute nitride for the bottom junction.

Let’s hope that the results offer some good news for CPV. It will be very tough for this technology to make inroads into the solar industry, but I’d be delighted if it did.

Diamond Microwave, a specialist in high performance microwave power amplifiers, has announced the launch of a range of compact microwave GaNbased pulsed solid-state power amplifiers (SSPA) in a new ‘slimline’ format, which includes 200 W and 400 W models at X-band. At the same time the entire SSPA product range has been rationalised, and further new models have been added that include a 1 kW C-band design and a rack-mounted 1 kW X-band amplifier.

The DM-X200-04 and DM-X400-04 are compact pulsed X-band GaN SSPAs with minimum peak pulsed output power specified at 200 W (+53 dBm) and 400 W (+56 dBm) respectively over a 1300 MHz bandwidth, operating with pulse widths up to 100 μs and with duty cycles up to 15 percent. Saturated power gain is nominally 55 dB. Both models feature built-in phase control to optimise power combining and are a compact alternative to vacuum tube amplifiers (TWT) in demanding defence, aerospace and communications applications. The amplifiers are slimline versions of the flagship DM-X200-02 and DM-X400-02 ‘smart’ high-power amplifiers (HPA), measuring only 150 mm x 197 mm x 30 mm. These amplifiers can be combined with an external Diamond Microwave two-way power combiner to realise a DM-X1K0-03 and to achieve in excess of 900 W peak pulse power. The DM-X200-04 and DM-X400-04 incorporate an internal electronically-adjusted phase shifter, which is used to optimise the combining phase and can be applied if alternative combiners are used.

The designs are flexible in layout and architecture and can be tailored to meet individual specifications and enclosure requirements. N-type output connectors are fitted as standard, but waveguide can be offered as an option.

“The amplifiers based on our new slimline platform are ideal for applications that do not require the sophisticated Ethernet monitoring provided by the ‘smart’ amplifier platform,” said Richard Lang, managing director of Diamond Microwave. “Both common platforms feature standardised mechanical and electrical interfaces, and all our designs can readily be customised to meet individual requirements. For example, we have recently produced a high-linearity model, and also a design that can employ either gate-pulsing or drain-pulsing to suit the class of amplification required.”

While standardising on interfaces and operating characteristic across its models, Diamond Microwave’s broadband 2.0 GHz – 6.0 GHz amplifier has adopted a new enclosure design that is extremely compact for its power output. A further two new models have also been added to the range: a 1 kW pulsed C-band amplifier at 5.2 – 5.9 GHz, and an X-band 1kW amplifier that is mounted in a 19 inch rack enclosure.

Osram OPTO Semiconductors is expanding its Oslon Black family for the infrared range with six new automotive IREDs. The 850 nm versions are intended for exterior applications such as night vision, pedestrian protection, pre-field recognition and lane detection.

The new 940 nm versions are suitable above all for interior automotive applications such as driver monitoring, seat occupancy detection and gesture recognition. Thanks to different wavelengths and lenses these products cover a wide range of customer requirements and can be operated at up to 5 A in pulsed mode.

The new products show a high maximum pulse current of up to 5 A, compared to 3 A previously. The IREDs are particularly bright, with an optical output of up to 2.0 W in continuous operation.

The six new IRED versions are available in different wavelengths and beam angles. SFH 4715AS A01, SFH 4716AS A01 and SFH 4717AS A01 all have a wavelength of 850 nm and a beam angle of ±45°, ±75° and ±25° respectively. SFH 4725AS A01, SFH 4726 A01 and SFH 4727AS A01 all have a wavelength of 940 nm and a beam angle of ±45°, ±75° and ±25° respectively.

A high refractive index silicone is used for the lens, giving it a particularly low profile so that only very little light is lost from the sides. The maximum operating temperature of the IREDs is 125°C. The high optical pulse outputs and the wide range of integrated lens options allow system designers to select the right IRED for virtually any application without having to install secondary optics. Infrared light sources in a wavelength range less than 900 nm are perceived by the human eye as a red glow. This red glow is largely suppressed at 940 nm.

After assessing planned purchases by suppliers, IHS Markit projects that 330 MOCVD reactor chambers producing GaN LEDs will be installed in 2018, leading to a growing surplus.

Focus Lighting and Shenzhen MTC have announced MOCVD expansion plans in recent months, while Sanan, Osram Opto, HC Semitek and others will also expand in 2018.

At the MOCVD shipment peak, 754 reactor chambers shipped in 2010. However, allowing for the greater production capacity of today’s more modern reactors, the actual wafer and die area capacity added in 2018 will be similar to that peak year.

In the last two years, the GaN LED wafer and die surplus has been quite small. Capacity utilisations have been high, but in an environment of uncertain demand and falling prices, suppliers were reluctant to make further investments, writes Jamie Fox, principal analyst, lighting and LEDs group, IHS Markit. Chinese companies are once again taking advantage of subsidies, to respond to growing demand. Mid-power LEDs in lighting, automotive headlights and signage are among the areas that did well in 2017, and they will continue to grow in 2018 – even allowing for the fact that some portion of the announced orders might be canceled or deferred into the following year. The expected over capacity will have a bigger effect on some markets, including lighting, and less on automotive and other markets, where the newer entrants are not qualified and the barrier to entry is much higher.

In 2017, the GaN LED surplus was 7.4 percent, which IHS thinks will grow to 15.8 percent in 2018 and 28.3 percent in 2019 (with an average capacity utilisation of 78 percent in 2019).

This IHS Markit forecast takes into account the available GaN LED supply – AMEC and Veeco will likely be working at full capacity, to meet expected higher demand in the coming years. Shipments in 2018 may even be limited by available supply, rather than demand.

CREE has signed a non-exclusive, worldwide, royalty-bearing patent license agreement with Nexperia BV, a Dutch company.

The agreement provides Nexperia access to Cree’s GaN power device patent portfolio, which includes over 300 issued US and foreign patents that describe inventive aspects of high electron mobility transistor (HEMT) and GaN Schottky diode devices.

The portfolio addresses novel device structures, materials and processing improvements, and packaging technology. The patent license involves no transfer of technology.

“Cree was founded to develop novel compound semiconductor materials like GaN and SiC and to create devices that capitalize on their unique properties,” said John Palmour, Cree co-founder and CTO of Wolfspeed, a Cree company.

“Cree’s decades of innovation are now yielding devices that enable market introductions of new power management and wireless systems. To help facilitate the growth of these new markets, Cree is licensing its GaN power device patents for GaN power-management systems.”

Other licensees of Cree power IP include Mitsubishi, which has a license to manufacture and sell freestanding GaN substrates from 2009; Transphorm which has a license to manufacture and sell GaN HEMT and GaN Schottky diode devices for power conversion; and Nippon Steel Corporation.

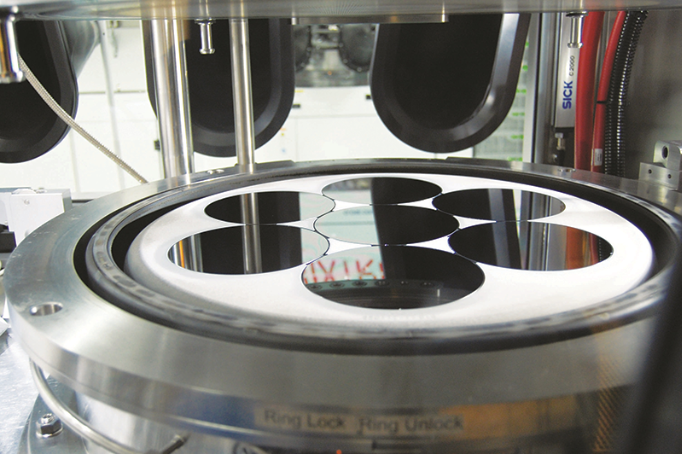

Belgian research hub Imec and fabless company Qromis, have announced their development of high performance enhancement mode p-GaN power devices on 200 mm engineered Coefficient of Thermal Expansion (CTE)-matched substrates, processed in Imec’s silicon pilot line.

The substrates are offered by Qromis as commercial 200 mm QST substrates as part of their patented product portfolio. The results were presented at the CS International Conference (April 10-11, Brussels, Belgium).

Today, GaN-on-silicon technology is the industry standard platform for commercial GaN power switching devices for wafer diameters up to 150 mm/6 inch. Imec has pioneered the development of GaN-on-silicon power technology for 200mm/8 inch wafers and qualified enhancement mode HEMT and Schottky diode power devices for 100 V, 200 V and 650 V operating voltage ranges, paving the way to high volume manufacturing applications. However, for applications beyond 650 V such as electric cars and renewable energy, it has become difficult to further increase the buffer thickness on 200 mm wafers to the levels required for higher breakdown and low leakage levels, because of the mismatch in coefficient of thermal expansion (CTE) between the GaN/AlGaN epitaxial layers and the silicon substrate. One can envisage to use thicker silicon substrates to keep wafer warp and bow under control for 900 V and 1200 V applications, but practice has learned that for these higher voltage ranges, the mechanical strength is a concern in high volume manufacturing, and the ever thicker wafers can cause compatibility issues in wafer handling in some processing tools.

Carefully engineered and CMOS fab-friendly QST substrates with a CTE-matched core having a thermal expansion that very closely matches the thermal expansion of the GaN/AlGaN epitaxial layers, are paving the way to 900 V-1200 V buffers and beyond, on a standard semi-spec thickness 200 mm substrate. Moreover, QST substrates open perspectives for very thick GaN buffers, including realisation of freestanding and very low dislocation density GaN substrates by >100 micron thick fast-growth epitaxial layers.

These features will enable commercial vertical GaN power switches and rectifiers suitable for high voltage and high current applications presently dominated by silicon IGBTs and SiC power FETs and diodes.

“QST is revolutionizing GaN technologies and businesses for 200mm and 300mm platforms”, stated Cem Basceri, president and CEO of Qromis. “I am very pleased to see the successful demonstration of high performance GaN power devices by stacking leading edge technologies from Qromis, Imec and Aixtron,” Basceri said.

In this specific collaboration, Imec and Qromis developed enhancement mode p-GaN power device specific GaN epitaxial layers on 200 mm QST substrates, with buffers grown in Aixtron’s G5+ C 200 mm high volume manufacturing MOCVD system. Imec then ported its p-GaN enhancement mode power device technology to the 200 mm GaN-on- QST substrates in their silicon pilotline and demonstrated high performance power devices with threshold voltage of 2.8 volt.

“The engineered QST substrates from Qromis facilitated a seamless porting of our process of reference from thick GaN-on-silicon substrates to standard thickness GaN-on- QST substrates using the AIX G5+ C system, in a joint effort of Imec, Qromis and Aixtron,” stated Stefaan Decoutere, program director for GaN power technology at Imec.

The careful selection of the material for the core of the substrates, and the development of the light-blocking wrapping layers resulted in fabcompatible standard thickness substrates and first-time-right processing of the power devices. Imec acknowledges funding from the Electronic Component Systems for European Leadership Joint Undertaking under grant agreement No 662133 (PowerBase).

By employing a device structure in which electrical current flows vertically from or to a substrate, Toyoda Gosei says it has been able to produce a GaN power transistor chip with operating current of over 50 A, the highest ever reported for vertical GaN transistors. It has also achieved high-frequency (several megahertz) operation.

Its newly developed vertical GaN power transistors (MOSFETs) and Schottky barrier diodes was presented on panel displays at the Techno-Frontier 2018 Advanced Electronic & Mechatronic Devices and Components Exhibition, held at Makuhari Messe, Chiba, Japan from April 18 to April 20.

The world’s first full vertical-GaN DC-DC converter equipped with these devices will also be demonstrated at the company’s booth. The company says this technology could be used to make lighter, more compact and higher efficiency power control units for automobiles, DC-DC converters, high frequency power sources, and higher output wireless power supplies.

KLA-Tencor has entered into a definitive agreement to acquire Orbotech at an equity value of approximately $3.4 billion and an enterprise value of $3.2 billion.

With this acquisition, KLA-Tencor will significantly diversify its revenue base and add $2.5 billion of addressable market opportunity in the high-growth printed circuit board, flat panel display, packaging, and semiconductor manufacturing areas.

“This acquisition is consistent with our strategy to pursue sustained, profitable growth by expanding into adjacent markets,” commented Rick Wallace, president and CEO of KLA-Tencor. “This combination will open new market opportunities for KLA-Tencor, and expands our portfolio serving the semiconductor industry.”

Wallace continued, “Our companies fit together exceptionally well in terms of people, processes, and technology. In addition, KLA-Tencor has had a strong presence in Israel over the years, and this combination further expands our operations in this important global technology region.”

“This acquisition is a true testament to Orbotech’s strong leadership and success,” said Asher Levy, CEO of Orbotech Ltd. “I firmly believe that this deal benefits our employees and creates additional value for our shareholders. Together with KLA-Tencor, we will significantly increase growth potential, accelerate our product development roadmap, and enhance customer offerings.”

Levy added: “Orbotech will continue to operate under the Orbotech brand as a standalone business of KLA-Tencor based in Yavne, Israel.”

Total cost synergies are expected to be approximately $50 million a year within 12 to 24 months following the closing of the transaction, and the transaction is expected to be immediately accretive to KLA-Tencor’s revenue growth model, non-GAAP earnings and free cash flow per share.

The transaction has been approved by the board of directors of each company and is expected to close before the end of calendar year 2018, subject to approval by Orbotech’s shareholders, required regulatory approvals and the satisfaction of the other customary closing conditions.

KLA-Tencor intends to fund the cash portion of the purchase price with cash from the combined company’s balance sheet. In addition, KLA-Tencor intends to raise approximately $1 billion in new long-term debt financing to complete the share repurchase.

Integra Technologies, a supplier of high-power RF and microwave transistors and amplifiers, has announced a pair of 135 W and a 130 W GaN-on-SiC transistors for S-band radar applications. IGT2731M130 is a 50 Ω matched highpower GaN HEMT transistor, suppling a minimum of 130 W of peak pulsed power, a gain of 13.5 dB and a drain efficiency of 55 percent, at pulse conditions of 300 μs/10 percent duty cycle. It operates at the instantaneous operating frequency range of 2.7 to 3.1 GHz, and is a depletion mode device. It requires a negative gate bias voltage and bias sequencing.

IGT3135M135 operates at the instantaneous operating frequency range of 3.1 to 3.5 GHz, supplying up to 135 W of peak pulsed power. This transistor is also a 50Ω matched highpower GaN HEMT transistor and is also a depletion-mode device that requires a negative gate bias voltage and bias sequencing.Both products come in Integra’s package PL44A1, size is at 20.32 mm wide and 10.16 mm long. Earless, they are 10.16 mm wide and 10.16 mm long. Assembled via chip and wire technology, using gold metallisation, both units are housed in a metal-based package and sealed with a ceramicepoxy lid.

Together with the Fraunhofer Institute for Applied Optics and Precision Engineering, TEMICON and Continental, Osram Opto Semiconductors has been working since October 2017 on the development of compact and low-profile optical components for data visualisation or illumination.

The purpose of the IBELIVE project, which is being funded by the German Federal Ministry for Education and Research (BMBF), is to deliver universal processes for space-critical applications. The project partners directly address a number of different markets, including compact and powerful head-up projection displays, ultra-thin camera flashes and selective direct display backlighting.

The IBELIVE research project (the acronym is from the German for Innovative Hybrid Diffusers for Low-Profile Lighting Systems with Tailored Light Distribution) is set to run for three years. The objective is to develop particularly compact multifunctional optical components. The background to this research work is the absence of any significant ways of further reducing the profile of the LED chips currently being used as light sources. In contrast, there is still great potential for miniaturising the optics.

In the course of the project the consortium will investigate flexible design and manufacturing processes for space-critical applications for data visualisation or illumination. The planned reduction in the thickness of the optical elements and the combinability of various optical functionalities in a microstructure will give designers much greater flexibility in integrating the components in the devices. Another benefit is an improvement in energy efficiency, as a much greater proportion of the generated light can be used for the applications. The partners bring years of experience to the research project in the fields of optics simulation, microstructuring of surfaces and opto-electronic system integration. The project covers the entire value-added chain from the development of optics and volume production to testing of the new technology in sample applications.

In addition to coordinating the project, Osram Opto Semiconductors is responsible for the system concept and for the design of two application-based demonstrators and is also researching installation and testing concepts. Continental is designing and developing two compact head-up displays with different projection light sources. The hybrid diffusers to be developed for this purpose play a central role in creating images and making efficient use of light in the head-up displays. Research here will focus on image quality as perceived by the driver.

The Fraunhofer Institute for Applied Optics and Precision Engineering is developing methods and algorithms for designing hybrid diffuser optics, as well as technologies for generating deterministic surface structures. The tasks assigned to TEMICON include using interference lithography to overlay nanoscale structures and developing injection stamping and molding technologies for replicating thin two-sided hybrid diffuser optics as series products.

“The IBELIVE research project brings together a powerful consortium with many years of experience in photonic materials and the necessary knowhow. Our findings will strengthen Germany as an industrial force and provide further evidence of our powers of innovation”, said Ulrich Streppel, Key Expert Modelling at Osram Opto Semiconductors.

Deposition equipment firm Aixtron has announced that it is providing the latest MOCVD technology to the German aerospace supplier Azur Space Solar Power. The AIX 2800G4 series system, with an 8x6 inch configuration, is intended for the further expansion of the production of multi-III-V space and concentrator solar cells, which are mainly used in the solar panels of satellites. Aixtron will deliver the customised system in the second quarter of 2018. Azur Space has been successfully using Aixtron’s planetary technology for a long time. The AIX 2800G4 system follows the predecessor models of the G3 series and enables the production of 6-inch epitaxial wafers from GaAs on germanium. Azur Space states that it benefits not only from the homogeneity of the processed wafers, but also from the economic advantages of the AIX 2800G4 – with maximum throughput and yield combined with the most efficient use of resources.

Jürgen Heizmann, managing director of Azur Space, says: “Applications in the aerospace industry have special requirements regarding the longevity and performance of solar cells. Aixtron’s equipment technology delivers this quality. With the introduction of the AIX 2800G4, we have deliberately set a very decisive, long-term course to continue to be able to supply competitive high-performance solar cells for the construction of space satellites in the future”.

Bernd Schulte, president of Aixtron SE, comments: “Our AIX 2800G4 system has earned an excellent reputation in the semiconductor industry as a reference system for the production of high quality epitaxial layers for GaAs-based devices. We are pleased to continue to support Azur Space as a longstanding customer in the expansion of its production.”

Veeco Instruments has announced that ON Semiconductor has ordered its Propel High-volume Manufacturing (HVM) GaN MOCVD system, based on successful beta evaluation of the tool. As the industry’s first single-wafer cluster platform, the Propel GaN MOCVD system is designed for high-voltage power-management devices used in data centres; automotive, information and communication technology; defence; aerospace and power distribution systems, among other applications.

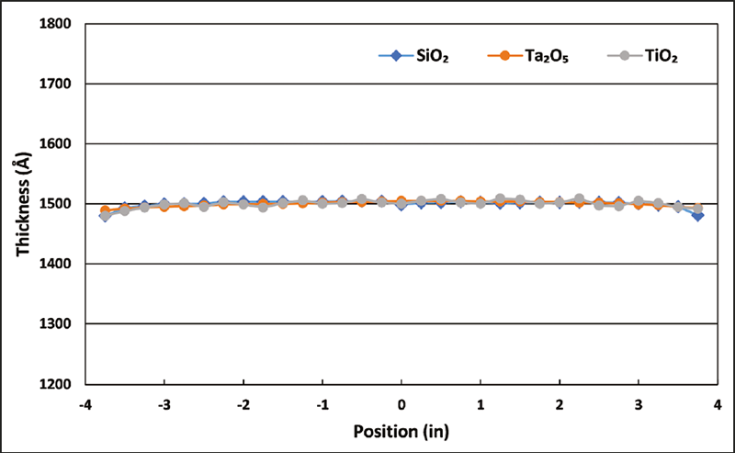

“Our prior learning with Veeco’s K465i GaN MOCVD system drove us to investigate the Propel HVM platform for our production ramp,” said Marnix Tack, senior director of corporate R&D and Open Innovation at ON Semiconductor. “The beta test results demonstrated superior device performance with high uniformity and within-wafer and waferto-wafer repeatability, while meeting our cost-of-ownership targets for six and eight-inch wafers. As such, the Propel HVM system proved to be the most suitable platform for our power electronics manufacturing needs.”

Veeco’s Propel HVM System is based on the company’s single-wafer system with proprietary IsoFlange and SymmHeat technologies that provide homogeneous laminar flow and uniform temperature profile across the entire wafer. The system is designed for the production of power electronics, laser diodes, RF devices and advanced LEDs.

“The Propel HVM platform is rapidly gaining traction in the industry as innovative companies like ON Semiconductor recognise the benefits of GaN-on-silicon, which will partially replace current silicon technology for power electronics,” commented Peo Hansson, senior vice president and general manager of Veeco MOCVD operations.

“With its highly controlled doping, run-to-run stability, superior wafer uniformity, high productivity and uptime, Propel HVM extends the benefits of our TurboDisc platform to a unique singlewafer architecture. These capabilities benefit customers that seek a superior solution for manufacturing while providing a path for scaling to eight-inch wafers and expansion to RF and other advanced applications.”

According to market research firm Yole Développement, the GaN power device business was worth $14 million in 2016, and projects that it will reach $460 million by 2022, with a compound annual growth rate (CAGR) of 79 percent. GaN-based devices will be used increasingly in RF amplifiers, LEDs and high voltage applications among others, primarily due to their abilities to operate at high frequency, power density and temperature with improved efficiency and linearity.

Veeco discussed the power of its MOCVD and wet etch systems in the ‘5G: Where Are We and What’s Next?’ track at the CS International Conference this week in Brussels, Belgium.

Somit Joshi, senior director of MOCVD marketing presented a session titled, ‘Enabling GaN RF and Power Electronics through Innovative MOCVD and Wet Etch Process Technologies’, on Wednesday, April 11, and the Veeco team also accepted the CS Industry 2018 Award for Innovation for its GENxcel R&D MBE System at the awards ceremony held during the conference.

Osram and Nichia have announced their intention to expand and strengthen their LED and laser license co-operation agreements, which were originally signed in 2002 and 2010.

Since 2011, the two companies have spent more than €2.5 billion in research and development, according to Aldo Kamper CEO of Osram Opto Semiconductors.

Now, the two companies have agreed to enter into negotiations of a cross license covering approximately 7000 new patent applications including approximately 2000 granted patents from Nichia and Osram (all figures are worldwide figures), covering automotive, general lighting, LCD backlights, display, medical and industrial applications and full range of optoelectronics products.

“On all levels of the value chain from semiconductor epitaxy to phosphor material, packaging and further downstream technologies, significant progress has been made in the past eight years and protected by a variety of new patents on both sides”, said Hiroyoshi Ogawa, president of Nichia.

In order to capture their technological achievements in all existing as well as emerging application areas for opto-electronics products and technologies, Osram and Nichia will discuss a cross license that will cover the many additional patents based on post-2010 inventions.

Kamper added: “I fully share this view. As a consequence, our companies will be able to leverage each other’s technological advancements, while both companies’ customers will benefit from an industry leading protection in IP related matters”.

CREE has acquired assets of Infineon Technologies AG Radio Frequency (RF) Power Business for approximately €345 million.

Infineon continues to drive key growth areas such as electro-mobility, autonomous driving, renewables and technologies for a connected world.

The business holds a leading market position offering transistors and MMICs (Monolithic Microwave Integrated Circuits) for wireless infrastructure radio frequency power amplifiers based on both LDMOS and GaN-on-SiC technologies.

The transaction includes the main facility in Morgan Hill (CA) which includes packaging and test operations for LDMOS and GaN-on-SiC; approximately 260 employees in the US locations as well as in Finland, Sweden, China and South Korea; and a transition service agreement to ensure business continuity and a smooth transition under which Infineon will perform substantially all business operations for approximately the next 90 days. Infineon will support the transaction with a long-term supply agreement for LDMOS wafers and related components out of its fab in Regensburg, Germany, and will also supply assembly and test services out of its facility in Melaka, Malaysia.

“We are looking forward to combining our strengths with Cree,” said Gerhard Wolf, VP and general manager, RF Power Products at Infineon. “With our highly skilled and dedicated team, advanced technologies and commitment to business excellence, we look forward to serving our customers seamlessly as the 5G mobile standard ramps up.”

The state-of-the-art backend manufacturing in Morgan Hill, as well as a leading intellectual property (IP) and technology portfolio are also part of the transaction. The transaction does not include the Infineon Chip Card & Security (CCS) operations in Morgan Hill that will remain at the site and continue to operate as part of Infineon. Cree funded the acquisition from cash and borrowings on its revolving line of credit. The Infineon RF Power business will become part of Cree’s Wolfspeed operating segment and is targeted to increase annual revenues by approximately $115 million in the first twelve months post acquisition. “The acquisition strengthens Wolfspeed’s leadership position in RF GaN-on-SiC technologies and provides access to additional markets, customers and packaging expertise,” said Cree CEO Gregg Lowe. “This is a key element of Cree’s growth strategy and positions Wolfspeed to enable faster 4G networks and the revolutionary transition to 5G.”

“Cree is a strong new owner for this portion of our RF business and has an excellent reputation in the industry,” said Reinhard Ploss, CEO of Infineon. “We are excited about the business rationale and the prospects for the combined businesses. At the same time, we will be able to focus our resources more effectively on Infineon’s strategic growth areas and will retain a strong technology portfolio for the wireless market.”

Infineon and Cree have a long-standing history of collaboration and shared business interests. The acquired Infineon RF Power team and capabilities will complement Wolfspeed’s existing offerings and expertise with additional technology, design, packaging, manufacturing, and customer support.

China’s production capacity for LED wafer and die increased dramatically between 2010 and 2018. The country has transformed itself from a small player in the LED market, to become the country with the biggest production capacity. Indeed, the production capacity of China is larger than the rest of the world combined.

This planned growth by Chinese companies was more than an attempt to meet demand; instead the goal was to increase the country’s market share. In fact, San’an (China) is now clearly ahead of Epistar (Taiwan), as the world leader in wafer and die production capacity.

In a world of $0.01 packaged 2835 mid-power LEDs for general lighting in Asia, LED vendors from other countries are realizing they cannot compete with China’s subsidies and low costs.

Vendors outside China are therefore now typically focusing on other LED categories for growth and profitability, including high power instead of low power, automotive instead of lighting, ultraviolet instead of visible, and light engines instead of packaged LED.

Another dynamic is that most non-Chinese companies have not expanded their capacity in recent years. In fact, many of them have not invested in MOCVD at all, which means capacity may even decline over time, as older machines go offline. These companies instead buy die from China and sell it as packaged LED or light engines. In some cases, they outsource to China their entire production of packaged LEDs. The current trend of expanding production capacity – along with further expansions in China – likely means this trend will continue.

LG Innotek revenue declined in its fourth quarter of 2017, and the company announced it would instead focus on higher-end products and ultraviolet LEDs. This is a direct response to the growth of Chinese capacity and the Chinese. Other companies have followed a similar strategy, but they have been able to avoid revenue declines by focusing more on the high-end market, along with automotive and signage, in addition to lighting.

The emerging market for SiC and GaN power semiconductors is expected to reach nearly $1 billion in 2020, energised by demand from hybrid and electric vehicles, power supplies and photovoltaic (PV) inverters, writes Richard Eden, principal analyst, power semiconductors, IHS Markit, in a new report.

Adoption of SiC and GaN power semiconductors in the main powertrain inverter in hybrid and electric vehicles will lead to revenue rising at a compound annual growth rate (CAGR) of over 35 percent after 2017, reaching $10 billion in 2027, he says.

By 2020, GaN-on-silicon transistors are expected to achieve price parity with silicon MOSFETs and IGBTs, while also providing the same superior performance. Once this benchmark is reached, the GaN power market is expected to reach $600 million in 2024, and climb to over $1.7 billion in 2027. Prospects for continuing strong growth in the SiC industry are high, fuelled predominantly by increasing sales of hybrid and electric vehicles. Market penetration is also growing, particularly in China, with Schottky barrier diodes, MOSFETs, junction gate field-effect transistors (JFETs) and other SiC discretes already appearing in mass produced automotive DC-DC converters and on-board battery chargers.

It looks increasingly likely that powertrain main inverters – using SiC MOSFETs, instead of Si insulated-gate bipolar transistors (IGBTs) – will start to appear on the market in three to five years. As there are many more devices used in main inverters, than in DC-DC converters and on-board chargers, the required quantity will also rapidly rise. There might come a time when inverter manufacturers eventually choose custom full SiC power modules over SiC discretes. Integration, control and package optimisation are the major strengths of module assemblers.

Not only will the number of per-vehicle SiC devices increase, but new, global registration demand for both battery electric vehicles (BEVs) and plug-in hybrid electric vehicles (PHEVs) will also increase ten-fold between 2017 and 2027, as many global governments aim to reduce air pollution and lower dependence on vehicles burning fossil fuels. China, India, France, Great Britain and Norway have already announced plans to ban cars with internal combustion engines in the coming decades, replacing them with cleaner vehicles. The prospects for electrified vehicles generally, and for wide band-gap masssemiconductors specifically, are therefore very good.

The biggest inhibitor to massive growth for SiC components could be GaN components. The first automotive AEC-Q101 qualified GaN transistor was launched in 2017 by Transphorm, and GaN devices manufactured on GaNon-silicon epiwafers boast considerably lower costs. They are also easier to manufacture than anything produced on SiC wafers. For these reasons, GaN transistors could become the preferred choice in inverters in the late 2020s, ahead of more expensive SiC MOSFETs.

The most interesting story for GaN power devices in recent years has been the arrival of GaN system integrated circuits (ICs), which are GaN transistors co-packaged with Si gate driver ICs, or monolithic, all GaN ICs. Once their performance is optimised for mobile phone and laptop chargers and other high-volume applications, usage may become prevalent in wider applications. In contrast, commercial GaN power diode development never really started, because they would not offer significant benefits over Si devices, and developing them proved too costly to be viable. SiC Schottky diodes already work well for that purpose and a have a good pricing roadmap.

Luminar, US-based startup, is ramping capacity for its InGaAs LiDAR sensing platform. First units have started shipping to Luminar’s four strategic partners with more development programs being added as production ramps up.

The team’s receiver, which is claimed to be the most photon efficient, highest dynamic range InGaAs receiver is designed to be paired with the company’s own ASIC chip.

The new Luminar system debuted last year. Since then, OEMs and technology companies have tested and validated the early hardware that fed development of the highly manufacturable platform.

To meet production targets, Luminar expanded its manufacturing to a 125,000 square foot complex in Orlando’s Central Florida Research Park. This gives Luminar the capacity to produce more than 5,000 units a quarter by year’s end.

Efficient Power Conversion (EPC) has announced the EPC2050, a 350 V GaN transistor with a maximum RDS(on) of 65 mΩ and a 26 A pulsed output current. Applications include EV charging, solar power inverters, motor drives, and multilevel converter configurations, such as a 3-level, 400 V input to 48 V output LLC converter for telecom or server power supplies.

The EPC2050 is 1.95 mm x 1.95 mm (3.72 mm2) integrating a half bridge with gate driver occupies in five times less area than a comparable silicon solution. Despite the small size of the chip-scale packaging, EPC2050 handles thermal conditions more efficiently than plastic packaged MOSFETs, according to the company.

“The performance and cost gap of silicon with eGaN technology widens with the 350 V, EPC2050, that is almost 20 times smaller than the closest silicon MOSFET.” said Alex Lidow, EPC’s CEO.

The EPC9084 development board is a 350 V maximum device voltage, half bridge featuring the EPC2050, and the Silicon Labs Si8274GB1-IM gate driver. This 51 mm x 38 mm board is designed for optimal switching performance and contains all critical components for easy evaluation of the 350 V EPC2050 eGaN FET.

The EPC2050 eGaN FET is priced for 1K units at $3.19 each and the EPC9084 development board is priced at $118.75 each from Digikey.

Integra Technologies, a US designer of high-power RF power transistors and module, is launching several new 50Ω (fully matched) RF power transistors and integrated RF power modules for pulsed radar applications at this year’s International Microwave Symposium in Philadelphia, PA.

IIGNP0912L1KW is a 50Ω GaN/SiC, RF power module for L- Band avionics systems operating over the instantaneous bandwidth of 0.960 - 1.215 GHz. This integrated amplifier module supplies a minimum of 1000W of peak pulse power, under the conditions of 2.5 ms pulse width, and 20 percent duty cycle, while offering excellent thermal stability. IGT5259L50 is a 50 Ω GaN/SiC transistor, offering 50W at 5-6 GHz for pulsed C-band radar applications.

IGN1214L500B is a high-power GaN/SiC HEMT transistor that supplies 500W at 1.2 - 1.4 GHz, and offers 50V drain bias, 15.5dB gain, and 65 percent efficiency. This transistor is designed for long-pulse L-band radar applications.

Along with these products, Integra will be discussing upcoming products to be released, including RF power modules up to 2000 W, X-band transistors, and a line of devices with advanced thermal control.

“We’re thrilled to mark IMS 2018 as Integra’s break out moment in providing the industry’s most advanced standard and semi-custom RF power devices,” says Integra’s CEO Suja Ramnath. “Our R&D team has been working diligently to push the boundaries of power and efficiency and we invite all radar system designers to partner up with us and ‘Find Your Power’.

As Apple and Sony turn to microLEDs to deliver next-generation displays, Plessey readies to capture market share with its GaN-on-silicon technology, reports Rebecca Pool.

Yole Développement expects more than 300 million displays, based on microLEDs, to be shipped by 2025, dwarfing today’s relatively negligible sales. Meanwhile, Research and Markets puts compound annual growth at 53.2 percent, with the global market reaching $19.89 billion by 2025.

One company intent on capturing market share is Plessey. Having supplied GaN-on-silicon LEDs for several years now, the UK-based LED manufacturer has made a success of growing structures on silicon instead of sapphire.

With its relatively high thermal conductivity, a silicon substrate enables devices with smaller heat sinks and small-scale formats. Factor in the tantalizing prospect of using relatively cheap, large silicon wafers on depreciated CMOS lines, and progress has been quick for Plessey.

Plessey would like to ramp up UK production, but according to marketing director, Myles Blake, this is unlikely ‘as investment appetites stand’.

Launching LED production at its Plymouth facility in 2010, the company unveiled industry’s first commercially available GaN on 6-inch silicon LED in 2013. Single chip, high-power packaged LEDs and horticultural lighting units followed in 2016.

Now, with new market growth in mind, Plessey has revealed its intention to deliver the industry’s first monolithic microLED displays by 2018. The company’s microLED arrays comprise highly efficient emitters that are as small as a micron and provide some 100,000 nits at 1 W, television-equivalent brightness at only 5 mW. Crucially, using these arrays can overcome the tortuous fabrication issues that plague the lion’s share of microLED displays.

Today’s microLED displays are assembled on a CMOS backplane, one sub-pixel at a time. A 4K television has some 25 million sub-pixels, going some way to explain why most microLED displays have been limited to smartwatches and smartphones.

But as Plessey marketing director, Myles Blake, points out, an array of Plessey GaN-on-silicon microLEDs can be mass transferred onto the CMOS backplane, dispensing with the pick and place minefield and delivering a cheaper, higher yielding manufacture process.

“Display size is purely limited by the size of the silicon, and we are producing our own backplanes that are scalable to any size we like,” highlights Blake. “This allows us to perform rapid custom development, and we can develop a custom backplane in just weeks.”

As Apple, Sony, Foxconn and more embrace microLEDs for spectacularly high resolution, high brightness, low-power displays, industry analysts predict the market will explode.

“Also, due to the capability of the [pick and place] handlers, the size of today’s [emitters] is limited to around 50 microns pixel pitch... but we’ve proven pixel production to one micron, and theoretically we can go down to sub-micron pixel sizes,” he adds.

Blake won’t yet reveal display yield figures, but has announced Plessey’s intention to license its GaN-on-silicon technology to microLED manufacturers. The company is also working with UK-based optical thin film coating supplier, Artemis Optical, to develop very high brightness, low-power head-up displays that are said to be smaller and cheaper than today’s devices.

“We really need to get ourselves out into the microLED market place and build up partnerships throughout the supply chain as quickly as possible,” he says.

Indeed, it’s no secret that the complex and lengthy microLED display supply chain is rather fragmented as bringing together LED production, display manufacturing and assembly isn’t easy. Still as Blake points out: “We are already talking with a large number of display manufacturers and it is never too early to do this. The manufacturing chain is now coming together.”

So what next for Plessey? Right now fabrication takes place on 6-inch wafers and looks set to remain on this wafer size for the foreseeable future.

“We have proven the capability of GaN-on-silicon on 8-inch wafers with our existing MOCVD reactor stacks but we don’t yet have the full equipment set beyond epitaxy to run this wafer size,” says Blake. “And we have yet to start on twelve inch production.”

Plessey also hit the headlines earlier this year with its plans to move towards an intellectual property licensing model rather than ramping UK production. At the time, Plessey chief executive, Michael LeGoff, cited a lack of investment funds, and according to Blake, the company would ‘love to scale production’ but adds that ‘as investment appetites stand, this almost definitely won’t happen in the UK’.

According to Blake, the Plymouth facility currently has two reactors, with associated processing equipment, and could eventually house 14 reactors. Given each reactor can churn out some two million 1mm2 die every week, the potential increase in output rates is significant.

“We will use and also expand this manufacturing capability within the bounds of the current facility,” says Blake. “This will be for research and development, and will include a level of manufacturing... but this is small compared to the [multi-billion dollar] microLED market predictions.” Clearly the marketing director has high hopes for microLEDs. As he asserts: “I believe that augmented reality and virtual reality will go bonkers during the next few years, with microLEDs providing the foundation to supply the anticipated spike in demand.”

GaN template manufacturer, Seren Photonics, is to scaleup processes for microLED displays. Rebecca Pool reports.

Earlier this year, UK-based manufacturer of GaN templates, Seren Photonics, revealed that it had secured £500,000 to scale-up MOCVD growth processes and drive green LED epitaxy on semi-polar GaN development forward.

The cash forms the first tranche of a £1 million funding round and follows several years of 2- and 4-inch semi-polar and non-polar template development targeting wavelength-stable, efficient green LEDs with high light output and reduced droop.

But importantly, it comes at a time when Apple, Sony and many more along the supply chain are eyeballing technologies that can deliver the spectacularly high resolution, high brightness, low power micro-LED screens that the display industry craves.

As Seren Photonics Chief Development Officer, Bedwyr Humphreys, puts it: “Our technology makes longer-wavelength [green, yellow and orange] InGaN/GaN based LEDs more wavelength-stable over a wide range of operating conditions and delivers the potential for improved efficiency through superior electron-hole recombination rates.”

Seren has already demonstrated that the template process can run in a pilot-scale environment and is now honing yields and process control.

“Our aim is to set up our own manufacturing facility at the emerging Compound Semiconductor Cluster in South Wales in around 18 months, whilst continuing to work with our existing partners,” adds Humphreys. “By this time, we want to be able to say: ‘Yes, we have the confidence that the product is doing what we expect it to and, yes, we have significant commercial traction to create a facility and make it a success’.”

Road to green success

Seren Photonics first emerged in 2009 to fabricate high efficiency InGaN/GaN nano-rod LEDs, pioneered at the University of Sheffield, UK. But within a few years, the company had switched focus and was using its growth-on-nanorod and AlN buffer layer approach to produce low-defect-density GaN templates for low-droop blue LEDs and high efficiency green LEDs.

Recent collaboration with Australia-based BluGlass sees Seren working to transfer its semi-polar GaN template process onto the semiconductor manufacturing developer’s MOCVD platform. Later this year, Seren plans to demonstrate the process on 4-inch wafers.

“Our research and development customers are happy to be playing on two inch wafers but LED customers and tech giants need a minimum of four inch wafers,” says Humphreys. “Six inch wafers aren’t a problem either and we will move onto these when they are required.”

According to Humphreys, tier one companies are interested in semi-polar templates to fabricate blue LED devices with reduced droop. Meanwhile, Asia-based tier two companies are drawn to samples of green LED epiwafers.

“Tier one companies tend to have a long-term mindset and are happy to take the template and develop the rest themselves,” points out Humphreys. “But tier twos, particularly those in Asia, simply want a device wafer that they can run through their fab, optimize the process and commercialise the LED.”

Given this, Seren is developing green structures on its semi-polar templates. “Overnight we saw immediate interest for ‘plug and play’ sample structures, when we started talking about green epi wafers,” says Humphreys. “So now we have evolved one step down the supply chain from templates to device epi-structures, although its unlikely that we’ll go any further than that.”

But while demand for semi-polar templates and epi-structures is clearly growing, what about Seren’s non-polar technology? Indeed, from word go, the company has been working on nonpolar GaN on r-plane sapphire as well as semi-polar GaN on m-plane sapphire.

Humphreys reckons customers from the LED industry have historically favoured the semi-polar template as epitaxy structures can be more easily grown on this material. But change is afoot.

“We’re now getting more enquiries for non-polar a-plane GaN for HEMT applications, such as sensors and electronics,” he says. “Non-polar GaN development is on our roadmap but we are focusing on semi-polar templates for optoelectronics right now.”

And without a doubt, optoelectronics opportunities are set to soar. France-based industry analyst, Yole Développement, forecasts more than 300 million microLED displays will be shipped by 2025, dwarfing today’s relatively negligible sales. Meanwhile, Research and Markets, Republic of Ireland, puts annual growth at 53.2 percent, with the global market reaching $19.89 billion by 2025.

Seren Photonics is hardly alone in its wish to grab market share. UK-based Plessey, for one, has revealed its intention to deliver the industry’s first monolithic microLED displays by 2018, while the likes of Aledia, France, and Glo, Sweden, are delivering 3D nanowires for microLED displays. Indeed, Aledia recently won €30 million to drive commercialisation of its 3D nanowire-on-silicon technology forward.

Humphreys describes these monolithic approaches as ‘elegant’ but asserts fabricating micron- to nano-sized red, green and blue LEDs on one chip isn’t easy and better suits smaller screen sizes, such as wearable displays. In contrast, he believes larger displays, including tablets, will benefit from having individual red, green and blue LEDs in the relatively big pixel spaces, making Seren’s technologies for efficient and wavelength-stable green LEDs a real draw.

“Today’s green LEDs have a wall-plug efficiency of less than 20 percent, so in some applications you have to have two green LEDs for every red and blue, raising power consumption,” he says. “Also, c-plane green LEDs have significant wavelength shift at different current densities, something that can cause problems in display applications.”

Given this, Humphreys is confident Seren’s approach provides the answer. “The ability to have LEDs that are wavelength-stable across a range of current densities and operating powers is so very important for these display applications,” he says, “So our focus is about getting green LED wafers out there right now; we’re quickly putting the pieces together and are targeting initial products within six months.”

What does Cree’s acquisition of Infineon’s RF Power arm mean for industry? Rebecca Pool talks to Wolfspeed Vice President, Jim Milligan, to find out more.

In March this year, Cree bought Infineon’s RF power business for €345 million. Shares of the lighting manufacturer shifted 9 percent upwards following the buyout news, and the move will help the company to bolster Wolfspeed’s business position.

The acquisition also comes one year after Infineon’s $850 million deal to buy Wolfspeed fell apart following US regulatory disapproval. At the time, the proposed acquisition fitted in with chief executive, Reinhard Ploss’ desire to grow Infineon’s SiC offering and expand into electric vehicle and 5G telecoms market segments. Then Wolfspeed chief executive, Frank Plastina, also asserted that Infineon would extend his company’s market reach and accelerate SiC and GaN technology commercialisation.

This time around, roles are reversed. But as Jim Milligan, Vice President of RF and Microwave Products at Wolfspeed puts it: “We see this as an opportunity to strengthen the position Wolfspeed has in the RF GaN market, for the same reasons as a year ago.”

This time, the transaction covers Infineon’s Morgan Hill, California, facility, including packaging and test operations for silicon LDMOS and GaN-on-SiC, a plastic packaging services line in Melaka, Malaysia, as well as all-important contacts with wireless infrastructure equipment manufacturers.

At the same time, Wolfspeed will scoop up some 260 employees – including more than 70 RF and GaN engineers – from the Morgan Hill facility as well as Chandler, Arizona, and Finland, Sweden, China and South Korea.

Company figures already indicate that the Infineon RF power business will raise Wolfspeed’s annual revenues by around $115 million in the first twelve months, post acquisition. And in addition to now being able to provide both bare die and packaged devices, Wolfspeed is vertically integrated from SiC wafers to devices, an advantage that the company describes as ‘unique positioning’.

“Infineon’s RF power business is an established leader in silicon LDMOS technology and the acquisition also brings access to more customers, additional markets, high volume packaging and test expertise,” highlights Milligan. “All of this really strengthens our position going forward particularly in existing 4G and emerging 5G markets.”

Indeed, the greater bandwidth and reduced latency that 5G telecoms will deliver, demands more spectrum in ever-higher frequency ranges. And as industry moves from traditional cellular bands, 1.8 GHz to 2.7 GHz, towards 3.5 GHz to 6 GHz bands, Wolfspeed intends to be ready.

“We’ve been playing on the 4G telecoms market with Ga-Non-SiC for a number of years and as we see 5G emerging in higher frequencies, we will really be able to access those opportunities,” says Milligan.

What now?

Going forward and as part of the deal, Infineon will support the transaction with a long-term supply of 8-inch LDMOS wafers and related components from its Regensburg fab, Germany. The company will also supply advanced packaging and test services from its Melaka and Morgan Hill facilities.

“Wolfspeed can now go to customers and offer state-of-the-art LDMOS but also GaN-on-SiC,” points out Milligan. “We are now in the position to provide the optimum technology depending on what the specific needs are.”

The company’s new employees are sprinkled across ex-Infineon operations, worldwide. And as Milligan points out, gaining some 70 RF and GaN engineers is a massive bonus.

“Infineon has a large entrenched base with its RF engineers that provides specific capabilities, particularly in telecoms wireless infrastructure,” he says. “This gives a lot of additional ability o go ahead and address these market very aggressively. The requirements associated with existing 4G infrastructure and the migration to 5G infrastructure is so specialised but [these new employees] bring very good device and systems level knowledge.”

So right now, Wolfspeed plans to double its entire capacity this year, and then, quadruple business by 2022. Indeed, postacquisition announcement, Cree chief executive, Gregg Lowe, told investors he has identified Wolfspeed as a primary growth engine for Cree, given the ‘multi-decade growth opportunity offered with the adoption of SiC and GaN technology in electric vehicles, solar energy, industrial, military aerospace and telecommunications’.

And Milligan can’t wait. “We have these markets as well as land mobile radio, commercial test equipment applications, homeland defense and radar markets,” he says. “We’re really excited about this acquisition and the growth it will provide going forward.”

Intengent, GCS and VLC Photonics have joined forces to deliver an InP PIC platform for wafer fabrication. Rebecca Pool finds out more.

Earlier this year, Canada-based III-V photonics consultancy, Intengent, joined forces with US compound semiconductor wafer fabrication foundry, Global Communication Semiconductors, and photonics IC design house, VLC Photonics, from Spain, to take InP photonic IC development to commercial production.

Together the partners will offer fabless development for the production of customised InP PICs, and Intengent chief executive, Valery Tolstikhin, is certain that the new team has what it takes to deliver a generic InP PIC platform for industrial-grade wafer fabrication.

As he points out, GCS is one of the world’s biggest III-V commercial foundries, churning out InP, as well as GaAs and GaN wafers, for RF electronics and optoelectronics markets in large volumes. Meanwhile, Tolstikhin himself, has pioneered a regrowth-free photonic integration platform – Taper

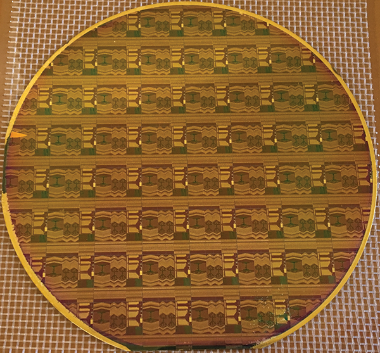

4-inch InP wafer of customised PICs. [GCS-Intengent-VLC Consortium]

Assisted Vertical Integration – based on the GCS’s well established optoelectronics process, for designing and developing InP PICs.

Factor in the VLC Photonics’ design library and process design kit expertise, which is already applied to other commercial PIC platforms and can slash PIC design effort and risk, and Tolstikhin’s confidence becomes understandable.

“Typically, people in the industry have an idea of the application they want to serve but often don’t know what device they want,” highlights Tolstikhin. “So we can conceptualize the PIC that matches that application and develop it through regular designmanufacturing-verification cycles – that’s what we do as a consortium.”

“Intengent provides the integration platform and underlying epitaxy design, VLC brings a wealth of experience in PIC design and characterisation, and GCS is probably the biggest commercial foundry in the III-V photonics domain,” he adds. “I have seen optics increase from 5 percent of GCS’s overall volume to more than 50 percent; this is a huge change and this [one-stop shop for InP PICs] is something I have wanted to be part of for a long time.”

Early days

In the last two decades, Tolstikhin has launched several PIC-based businesses, pioneering various photonic integration platforms based on different versions of vertical integration.

He first became involved with PICs in 2000, when he joined MetroPhotonics, a spin-off from the National Research Council of Canada, set up to commercialise wavelength-division multiplexing technology for InP. Here, he led PIC design until the company folded in 2005, and during this time developed and patented a robust, regrowth-free active-photonic device integration technique called ‘single-mode vertical integration’.

Having developed a number of InP-based WDM components at MetroPhotonics, he went on to launch OneChip Photonics, with a view to developing cost-efficient InP PICs using his regrowth-free PIC technology.

The OneChip business model was based on fabless manufacturing, which Tolstikhin has always touted as being appropriate for low volume markets. And during his leadership at OneChip, he honed his vertical integration process, pioneering ‘Multi-Guide Vertical Integration’.

Here, by vertically stacking the necessary materials for, say, lasers and detectors, the technology allowed the company to monolithically integrate active, as well as passive, devices onto the same substrate in a single epitaxial growth step.

As the chief executive highlights: “I individually designed every single epitaxial structure for every PIC product developed or tried by OneChip, which was an absolutely crucial step in regrowth-free PIC production.”

OneChip went on to develop PIC-based optical interconnects for 100G datacentre market applications, partnered with GCS and IQE on wafer processing and epitaxial growth, but closed in 2014, by which time Tolstikhin had co-founded ArtIC Photonics, a fabless developer of InP-based PICs for telecoms and datacoms markets.

ArtIC remains today, designing PIC chips for optical component products, but in 2015 Tolstikhin founded Intengent to design and develop InP PICs, this time based on Taper Assisted Vertical Integration (TAVI).

Tolstikhin hopes to see ‘real commercial infrastructure’ for the fabless development of III-V photonics, in place within five years. [Intengent]

Building blocks

The TAVI library comprises many building blocks, from lasers to amplifiers to detectors on the active device side and splitters/combiners, filters, and various elements of waveguide circuitry, on the passive device side. What is common to all of them is a lateral taper assisted adiabatic transition between vertically stacked and functionally different guiding layers.

Perhaps, the most generic building block, which showcases the TAVI platform from this prospective, is the spot-size converter that permits the transition of guided light from a PIC waveguide to an optical fibre. This is defined by building lateral tapers in a specially designed multilayer epitaxial structure. Indeed, as Tolstikhin points out: “Intengent has now been working with a commercial foundry on the epitaxy growth of specialised wafer designs that comprise up to 90 layers.”

“It is so important to allow the optical signal to move from one vertical layer to another.... and lateral tapering allows you to vertically connect all of your waveguides,” he adds. “This method is very flexible, it is a big deal and we are seeing big gains in reliability.”

Right now, Intengent is predominantly working on 4-inch wafer sizes with GCS, but intends to transition to 6-inch wafers as soon as possible.

“I would love to work with six inch, even eight inch wafer sizes but these are not readily available right now,” says Tolstikhin. “In terms of cost, size of wafers really does matter here as the number of devices you can harvest is so different from wafer to wafer; this is not like laser development, these really are big chips.”

“I cannot name the date, but six-inch wafer fabrication is coming,” he adds.

Crucially, so is demand. According to Tolstikhin, he is thinking of expanding the company to cope with growing demand for InP-based PICs from various segments of the market, from tele- and Datacom to microwave photonics and quantum inscription.

And at the moment, the chief executive is also seeing interest from silicon photonics businesses demanding III-V integration. “[Designs] now need sophisticated light sources that cannot be provided by off-the-shelf by bulk assembly,” he says. “This is one avenue that wasn’t really evident a few years ago.”

With demand rising, Tolstikhin is now looking forward to seeing what he describes as ‘real commercial infrastructure’ for the fabless development of III-V photonics. He hopes such infrastructure will be in place within the next five years, and importantly, he expects this to be able to provide a full level of customisation, within a reasonable budget.

“Following the development of silicon photonics, many in our industry now understand the need for fabless development and the pointlessness of building an entire infrastructure for just one device,” he asserts. “We are trying to capitalise on this and provide the services that those people want.”

Etching deep, lateral gratings in GaN lasers equips these sources with the credentials to target atomic clocks by Nick Bowden and Thomas Slight from CST Global

What will be the legacy of the Blu-ray player? With the rise Netflix and other video-streaming services, sales of this player could rapidly decline. But the Bluray will still be cherished, in this industry at least, as the product that drove the commercialisation of the GaN-based laser.

The good news is that a second killer application is now emerging for this class of laser: illumination. GaN lasers are already being used in the headlights of high-end cars, and they are a very promising source for all forms of colour projector.

Other markets are also on the horizon. They demand GaN lasers with greater spectral purity and wavelength selectivity, characteristics that may be introduced by replacing the Fabry-Pérot cavity with a distributed feedback design. Making the switch allows the lasers to win deployment in plastic optical fibre networks and to provide communication through water, and last but by no means least, to serve in atomic clocks, where their blue emission is used to cool atoms.

At present, there are two common options for the optical source that is used in atomic clocks: bulky, solid-state lasers, which use frequency doubling to produce appropriate wavelengths; and blue laser diodes with external cavities, a combination that requires complex, vibration-sensitive mechanical assemblies. Replacing either of these sources with a GaN-based laser that features distributed feedback would deliver multiple benefits. It could simplify the design of the clock, slash its size, make it more robust, and ultimately underpin its transition from the lab to mainstream, commercial applications.

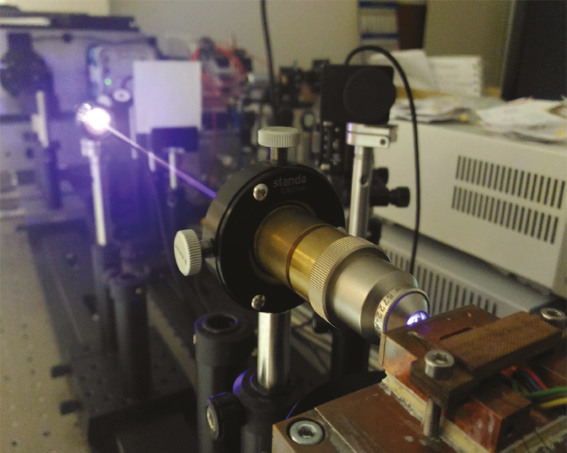

To try and turn this dream into a reality, our team at CST, the University of Glasgow, TopGaN Lasers and Aston University has been developing GaN lasers with the required attributes through a project known as CoolBlue. This effort, which is has the official title, Quantum Cooling using Mode Controlled Blue Lasers, has revealed that it is possible to produce a commercially viable, single wavelength, GaN laser diode for atomic-cooled, quantum sensors.

Figure 1. A distributed feedback laser under test.

Credit: S. Stanczyk, TopGaN Ltd.

While the market for this device may never be as big as that for the Blu-Ray player, it can still be significant. According to a 2015 report entitled A roadmap for quantum technologies in the UK (co-authored by Innovate UK, a leading UK Government research funding agency, and the Engineering and Physical Sciences Research Council) the global market for quantum technology is worth about $1 billion. If a third of this is quantum sensing, 10 percent of that is associated with sensing hardware, and one-tenth of that is the laser source, the market for this class of GaN laser diode is £3 million. Project a conservative annual growth of 10 percent, and that is a market of £5.3 million in five years.

Tapping into this market will require volume production of laser diodes that combine many of their well-known attributes – such as a small size and a robust packaging – with a high degree of spectral purity, ideally realised with a relatively simple approach. We are able to do this with our novel form of grating.

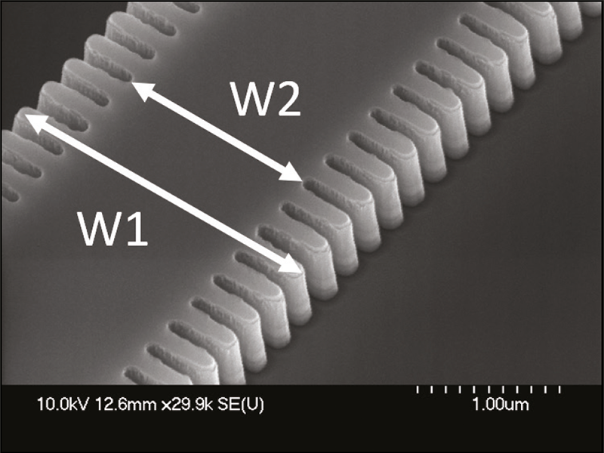

Figure 2. A scanning electron microscopy image of the ‘as etched’ third-order grating, with waveguide widths W1 and W2 of 1.5 μm and 2.5 μm, respectively.

Grating design

Our approach differs from the two conventional ones that have been adopted for the production of distributed feedback laser diodes. One option is buried gratings, which are hampered by complex overgrowth steps that risk epi-defects. With the common alternative – surface gratings etched directly into the ridge top – the danger is a reduction of p-type contact quality, due to damage caused by reactive ion etching. Another impediment associated with surface gratings is a significant optical loss in the electrically un-pumped grating regions, an issue that may be mitigated with shallow-etched, lateral grating designs.

We avoid all of these pitfalls by pioneering deeply etched, lateral gratings. One of the merits of this approach is its reduced number of steps: most of the structure, including the waveguide and the grating, is formed in a single step. Additional advantages are a higher yield and a larger grating coupling coefficient, strengths that we particularly value for producing sources for atomic-cooled, quantum sensing systems, such as atomic clocks.

Fabrication of our lasers begins by taking commercially-available, MOCVD-grown GaN lasergrade wafer material that contains an active region with InGaN quantum wells with GaN barriers, and using an electron beam lithography tool at the University of Glasgow to define grating and ridge patterns. Reactive-ion etching transfers the pattern into a 100 nm-thick, hard mask before inductively coupled plasma etching forms the grating and the ridge. The resultant structures have a nearly vertical and smooth etch profile, to ensure optimal grating performance.

Completion of our devices involves the addition of an electrical contact to the cap layer, before the reverse of the wafer is mechanically-thinned and polished, before a conductive metal layer deposited on it. Finally, the devices are cleaved to different cavity lengths, with both front and back facets left uncoated.

Fabricating of first-order sidewall gratings is challenging, as it requires high aspect ratios and feature sizes as small as around 40 nm. So we use third-order gratings, which have minimum feature size of around 120 nm.

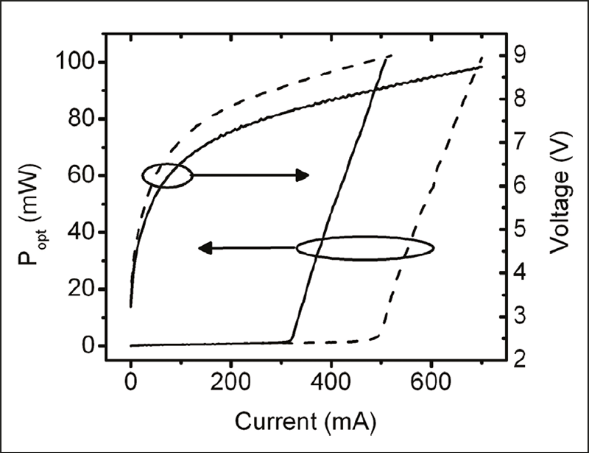

Figure 3. Optical power and voltage as a function of pulsed drive current for distributed feedback device (solid line) and the Fabry-Pérot device (dashed line).

We have undertaken simple modelling to improve our grating design, and gain greater insight into the influence of grating dimensions on device performance. Using the beam propagation method, we have calculated the effective modal index. Then, using this value we have determined that for lateral grating waveguide widths of 1.5 μm and 2.5 μm and an etch depth of 0.5 μm, there is a refractive index difference within the laser of 0.0015. Using this value, and turning to couple mode theory, we can estimate a value for the coupling coefficient of 22 cm-1. To ensure a single mode yield, the product of the coupling coefficient, k, and cavity length should be around 1.5, implying that the optimal cavity length is around 700 μm.

To evaluate the performance of our devices, we have undertaken light-current-voltage and spectral measurements on distributed feedback lasers with a third-order grating that features lateral grating dimensions of 1.5 μm and 2.5 μm, a cavity length of 1000 μm and an etch depth of 520 nm. So that we can benchmark the performance of these devices, we have also fabricated Fabry-Pérot lasers with similar dimensions from the same wafer.

Pulsed drive measurements at 20 °C reveal that the slope efficiencies of both types of laser are similar. However, the distributed feedback laser has a lower threshold current, suggesting that the feedback from the grating is stronger than that from the cleaved facets. Both classes of laser have relatively high threshold currents, which is thought to be primarily due to sub-optimal epi material.

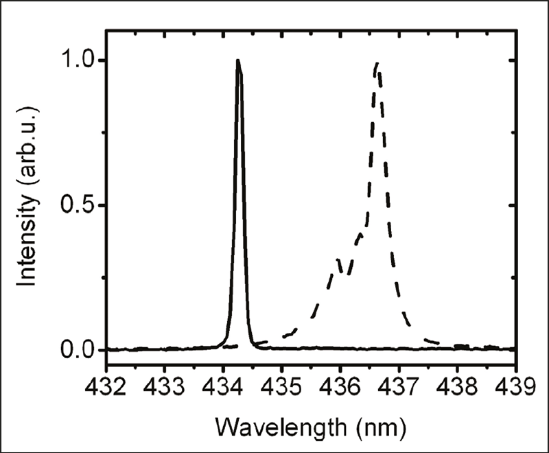

Figure 4. Single wavelength emission for distributed feedback device (solid line) and, for comparison, multimode spectra of the Fabry-Pérot device (dashed line).

Atomic aspirations

As expected, the emission from the distributed feedback laser is much narrower than that produced by the cousin with the Fabry-Pérot cavity. While the latter exhibits multi-mode emission, the distributed feedback laser produces a single wavelength emission spectrum (see Figure 4). At a drive current of 390 mA, which is 20 percent above threshold, this laser produces an output of 40 mW and has a spectral purity, judged in terms of the side-mode suppression ratio, of 22 dB. These values are sufficient for laser cooling within atomic clocks. However, meeting all the requirements for that application will require more work, including the realisation of continuous wave operation, and the shifting of the emission to 422 nm to target the Sr+ ion.

While reaching an emission wavelength of around 422 nm will get in the right ballpark for the Sr+ ion, temperature tuning is needed to hit the cooling line. To assess the capability for this, we have measured the performance of another distributed feedback laser, which has an emission wavelength of around 437 nm.

By varying the heat-sink temperature between 20 °C and 30 °C, we can tune the emission wavelength during pulsed operation. This device has a tuning coefficient of 0.013 nmK-1, which compares well with published values for lasers of this type.

Thanks to the successes that we have had, we have won funding for a follow-up project, CoolBlue2. It started in April 2018 and runs for a year. All the partners in the first project are retained, and are joined by the National Physical Laboratory (NPL) and Helia Photonics. The role of NPL includes performing laser cooling system tests to demonstrate the efficacy of the technology, while Helia is offering expertise in laser facet coating, enabling improvements in laser performance.

We hope that the GaN technology that we develop in CoolBlue 2 will form the critical elements in many quantum applications. This effort should result in a stringent set of performance requirements for wavelength, stability, output power and linewidth, and will offer a clear understanding of how lasers can be deployed in many different applications.

Looking even further ahead, after CoolBlue 2 has finished, those of us at CST will continue to invest in product development, assuming sufficient visibility of market opportunity and maturity of the supply chain. This investment is likely to be at the chip or packaged device level, although clearly opportunities may exist for subsystem-based products.

This work was supported by the Innovate UK project Coolblue (project number 132543) and by The National Centre for Research and Development within the Eurostars 2 Programme (E10509/29/NCBR/2017)

Further reading

T. J. Slight et al. IEEE Photon. Technol. Lett. 28 2886 (2016)

Employing the mass production techniques of the optoelectronic industry will increase the bang-per-puck of CPV by Richard Stevenson

It would be easy to think that the CPV industry has completely disappeared. Deployment of this technology has fallen through the roof, with many big names having filed for bankruptcy over the last few years.

However, there is still activity – and with that comes hope. Early last year STACE – Saint-Augustin Canada Electric Inc., a supplier of large electrical equipment in the power generation industry – acquired Soitec’s CPV technology; and in Europe, a collaboration between several companies is currently developing a lower-cost, highly efficient CPV system that borrows high-volume manufacturing techniques from the optoelectronics industry.

The latter project was detailed at Advances in Concentrator Photovoltaics for Space and Terrestrial Applications, held at Cardiff University on 8 March. Spokesman for the project, entitled A low Cost, High Efficiency, Optoelectronic HCPV Module for 1000 Sun Operation, was Andy Johnson, IQE’s Solar Business Unit Leader and CPV Technology Director.

According to Johnson, the focus of the €1.24 million project is to improve the performance of the FullSun CPV modules. The starting point is a design that has a concentration of 625 suns, and produces an efficiency of 30 percent by harnessing concentrated sunlight with cells that have a 36 percent efficiency. The targets are to increase efficiency to 1000 suns, and to realise a 37 percent module efficiency using triple-junction cells with a higher efficiency than before.

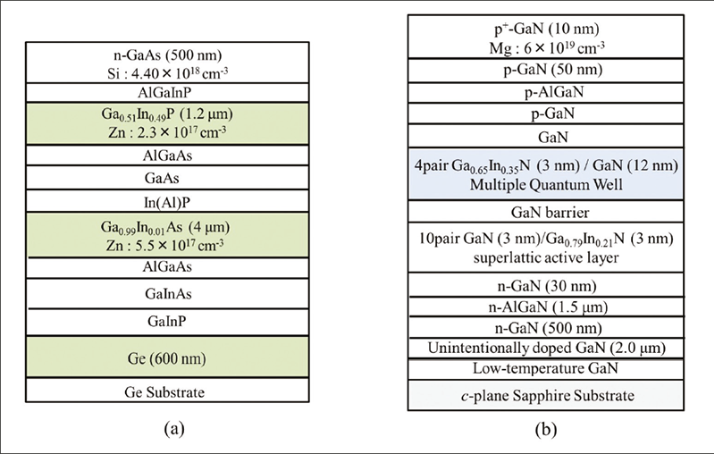

Three different triple-junction cells are being evaluated in the project: a generic, lattice-matched design from IQE that has an efficiency of 39 percent or more at 1000 suns; an Azur Space 3C44 cell, which has an inverted metamorphic architecture with an efficiency in excess of 42 percent at 1000 suns; and a latticematched device made by Solar Junction, which features a dilute nitride for the low-energy junction. “Solar Junction’s materials was grown by MBE,” said Johnson.

The philosophy behind the module, made by FullSun, is to adopt best practice from the optoelectronics industry, including the use of surface mount technology. This approach, which drives down capital costs, involves the use of cells that are just 1.3 mm square. These cells, which are covered by a silicone lens and packaged on lead frames, are sparsely arranged on an aluminium back plane. “There is no need for additional heat sinking,” explained Johnson.

Benefits of this design of module include reduced maintenance and purchase costs. What’s more, the units have a low mass – they are less than 4 kg – and a thickness of just 48 mm, making them easier to transport; and installation is straightforward, trimming labour costs.

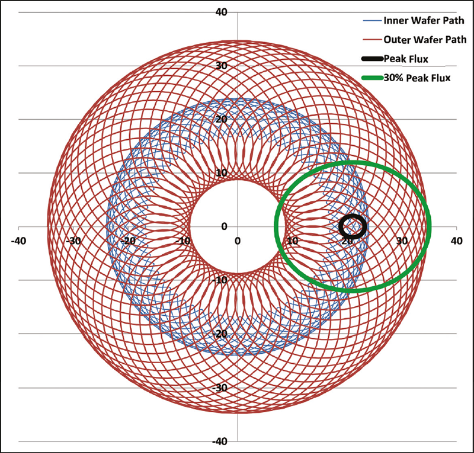

Johnson explained that a team at Fruanhofer ISE is behind the changes to the optical design of the module that is propelling the concentration from 625 suns to 1000 suns. Given a target area of 1 mm by 1 mm, the team retained the secondary optical element – that is, the silicone lens on top of the cell – and just adjusted the primary optical element, the Fresnel lens. Its focal length could be changed.

Another partner in the project is the III-V Semiconductors Group at the Solar Energy Institute of the Technical University of Madrid (IES-UPM). This team have worked on optimising the grid on the 1.3 mm by 1.3 mm cells, by evaluating the impact of varying grid line width and the number of fingers. They considered using between 12 and 25 fingers, and found a sweet spot of 14 to 18. The team’s next step is to compare the performance of different grid structures.

These researchers only have a few more months to work on this. Assembly of the 1000 sun modules is slated for the third quarter of this year, and testing is scheduled to follow in quarter four.

These field tests will take place at the University of Cypress, an ideal location for putting any photovoltaic system through its paces. It is hoped that this design, which will be mounted on a two-axis tracker, can get close to a cost of €0.35/W to €0.45/W.

Ensuring reliability