The progress of the silicon IC has been driven by scaling. Increasing the size of the wafers has brought down costs, and shrinking the size of the transistor to the nanoscale has propelled performance, while trimming power consumption.

For the optical equivalent, the photonic integrated circuit (PIC), one can follow in these footsteps. Whether the substrate is silicon or InP, wafer size can increase. And efforts can be directed at shrinking the size of all the components that form the PIC.

However, how much can be gained by making ever smaller features? The nanoscale is fine for electrons zipping through transistors, but is it a good idea for photons with wavelengths beyond a micron?

One company that thinks that it’s important to hit a sweet spot, rather than pursuing ever smaller dimensions with diminishing returns, is PIC manufacturer Rockley Photonics. It makes the case for the design in its feature The benefits of multi-micron waveguides.

According to Rockley, multi-micron waveguides offer several benefits: they deliver a ten-fold reduction in waveguide loss; they slash performance variability by a factor of 25; they provide polarization independence; and they enable the use of a monolithic ultra-broadband fibre-attach technology.

Another benefit of multi-micron waveguides – and this may come to you as a surprise – is that they can realise tight bends while ensuring strong confinement of the electromagnetic wave. That’s a major asset, because designers of PICs want to avoid large bends, so that they can reduce the footprint of these chips.

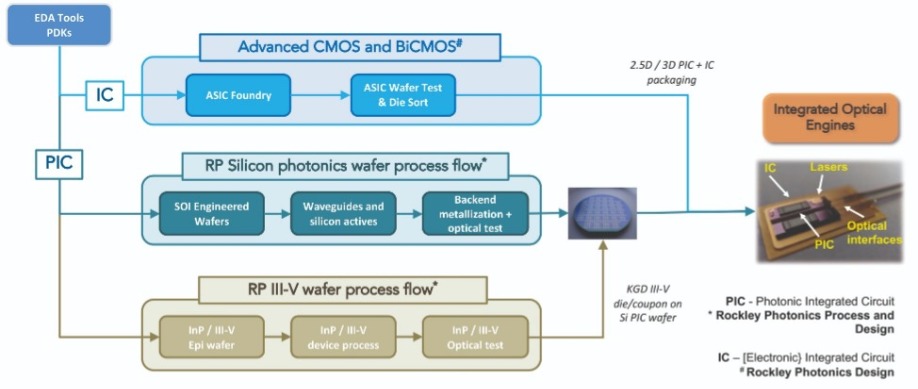

Rockley employs several foundries for the production of its integrated optical engines. Waveguides and active silicon devices are produced in a fab that processes silicon-on-insulator wafers, and lasers are made in a III-V fab, before being attached directly to a recess etched into a silicon waveguide. The resultant chip is then combined in a package with an IC, made at a foundry offering advanced CMOS and BiCMOS processes.

Rockley is targeting many applications with these packaged products. It is vying for success in the data communications sector, where it can meet requirements for high bandwidth and compactness; and it has a competitive offering for LiDAR, meeting the demand for high-power handling.

I hope Rockley’s PICs enjoy much success. But even if they don’t, they have helped me to stop falling into the trap of thinking that for ICs, smaller devices must be better.

Transphorm has confirmed that customer AES Aircraft Elektro/Elektronik System GmbH has released its first 650 V GaN-based power supplies. Serving the aviation industry, AES supports customers with various products and services ranging from electrical engineering to certification and testing.

The company’s newest switch mode power supplies are currently used by large CS-25 airplane manufacturers

(for example, Airbus A318-A321, A330, A340, A380 and Boeing B767, B787 VIP aircraft) and use Transphorm’s GaN FETs to increase overall system efficiency by more than 10 percent compared to competitive silicon-based power supply units (PSUs).

The two GaN-based switch mode power supplies are the PS250X 500 W system and the PS6120 1200 W system. Both products support a 96-130 VAC/360 Hz - 800 Hz input voltage with a 28 V, DC continuous power output at 15 amps for the 500 W system and 42 amps for the 1200 W system.

Further, AES certified the PS250X and PS6120 as DO-160 compliant – meeting the more than 25-point stringent Standard of the Radio Technical Commission for Aeronautics (RTCA). This Standard assesses system impact and performance under various external and internal conditions on aircraft – ranging from pressure and temperature to voltage spikes and RF emissions.

The flagship 500 W PS250X is the industry’s first passively cooled power supply at 420 W and deploys Transphorm’s GaN in a single-phase CCM boost power factor correction (PFC) topology. It offers more than 92 percent overall system efficiency at full load, which is more than 10 percent greater than its competition. The system also yields a more than 0.98 power factor and 200 mVpp nominal at 115 VAC/400 Hz input at full load. All within an end product that is 1.4 kg.

The 1200 W PS6120 deploys Transphorm’s GaN in a fan-cooled, three-phase CCM boost PFC topology. It offers more than 91.5 percent overall system efficiency at full load, which is 11.5 percent greater than its competition. The PS6120 also yields the same power factor and nominal ripple voltage at 115 VAC/400 Hz input at full load as the PS250X 500 W PSU. All within an end product that is 4.0 kg.

“The aviation industry is working toward reducing climate impact through any means possible,” said Andreas Hammer, Head of Competence Center Power, AES.

“Considering, we sought out Transphorm’s GaN to replace previously used silicon MOSFETs so that we could provide a more efficient, lighter weight power supply. These supplies have the potential to make a notable impact when considering each aircraft deploys several such PSUs. After only a year of redesign, we were able to offer our customers a better power solution, while also raising the performance bar within our own industry.”

Interested in the technology’s inherent higher switching frequency, AES reviewed GaN power switch converters from several GaN device semiconductor manufacturers. The company ultimately selected Transphorm’s 650 V GaN technology due primarily to its ease of drivability and designability – specifically because Transphorm’s GaN FETs do not require custom drivers.

As a result, system design is simplified while engineers can drive the switches using technology they are already familiar with. Other factors affecting AES’ selection included Transphorm’s proven reliability, which is underscored by its GaN platform earning both a JEDEC qualification and AEC-Q101 qualification at 175°C.

“Transphorm designed its GaN devices to enable designers, not challenge them,” said Philip Zuk, VP of Worldwide Technical Marketing and NA Sales, Transphorm.

“Our two-switch normally-off GaN devices come in standard packages and require minimal supporting circuitry to drive them, which reduces the overall system size, increases reliability, and simplifies design. It’s crucial to us that our customers can come to market quickly with a product they have confidence in. We’re honoured to be AES’ GaN supplier of record and are proud that they appreciate the work we’ve done to bring the benefits of GaN technology to the masses.”

Micledi Microdisplays, the latest spin-off of from Imec, has raised €4.5 million in seed capital. The funding will be used to develop microLED displays for next generation Augmented Reality (AR) glasses.

Micledi’s vision is to enable AR for everyday personal use – smart glasses that are small, lightweight, with long battery life, and at reasonable cost. To make this happen, Micledi is developing the world smallest and brightest displays. The key innovation behind Micledi is the new integration technology for microLEDs on 300 mm wafers developed in collaboration with Imec.

Micledi Microdisplays was founded by Soeren Steudel and Alexander Mityashin, both researchers from Imec with a deep know-how in the R&D field and display development. They are joined by Sean Lord, an experienced executive in the semiconductor industry, as CEO. “AR glasses may replace our smartphones in the future and display technology is a key enabler for such a transition.

Today’s display technologies cannot fulfil the specifications needed for next generation AR glasses. At Micledi we are tackling this challenge and have developed displays that are a hundred times brighter than commercial alternatives”, explained Soeren Steudel. In order to implement the vision that future consumer AR devices will be powered by a tiny display developed in Leuven, the company has raised €4.5 million seed investment from Imec.xpand, PMV, and FIDIMEC.

“We are pleased to back a unique team. We look forward to working with them and to enable technology that will be at the core of future AR devices and will change how digital information is presented to consumers,” said Cyril Vancura, Partner at Imec.xpand. Micledi’s will develop its microLED technology and first prototypes on Imec’s 300 mm pilot-line infrastructure. “Hardware development takes courage, capital and time. We are proud of the entrepreneurship of our engineers to bring promising technology developments originating from our R&D, to the market,” said Luc Van den hove, president and CEO at Imec.

“Based on an original concept launched, now more than two years ago, by the Micledi team, Imec together with Imec.xpand incubated this into a promising technology base and exciting business case. It leverages Imec’s extensive R&D in organic displays, 300 mm integration and wafer-scale optics technologies.”

“Micledi’s new generation displays for AR glasses fits in PMV’s strategy of supporting early stage technology with a largescale international potential, hence strengthening Flander’s position as a top region,” said Roald Borré, head of equity investments at PMV.

As projectors grow more and more popular in home entertainment systems, so have the expectations of users. In addition to ever-higher resolutions, the focus is also on richer colours, contrasts and, of course, higher brightness.

With the Ostar Projection Power family, Osram says that it has succeeded for the first time in achieving projector brightness levels beyond the 3,000 ANSI lumen barrier using LEDs instead of conventional lamps, making them accessible to a broad market.

Depending on the ambient light conditions and the distance to the projection surface, requirements differ for the light source. With 12 new products, Osram is now able to offer three different power classes for RGB solutions in deep blue (440 nm), blue (456 nm), converted green (520 nm) and amber (614 nm).

In the lowest power class, two chips of the same colour per component provide projector brightness of up to 1,500 ANSI lm. In the mid-power class, four chips of the same colour per component can achieve 2,500 ANSI lm. While in the highest power class, six chips of the same colour per LED can achieve more than 3,000 ANSI lm. As a result, products from the Osram Ostar Projection Power family emerge as a clear alternative to the high-pressure discharge lamps previously used in projectors above 2,000 ANSI lm.

This leap in performance was achieved, among other things, by improved chip and package technology. The developers at Osram have fundamentally modified the individual LED chips allowing them to be electrically connected in series on the copper board. The system designer benefits not only from a significantly lower operating current (with the same power consumption) and reduced complexity of the LED driver, but also from the much simpler contacting of the component. In addition, direct coupling of the LEDs to a heat sink is possible – without additional isolation costs.The mechanical design remains largely unchanged compared with previous products enabling a fast and uncomplicated exchange of the products in existing projector systems.

“With products from the Osram Ostar Projection Power family, we have successfully crossed the 3,000 ANSI lumens barrier using LED technology,” explains Wolfgang Schnabel, product manager in the Visualisation & Laser division at Osram Opto Semiconductors. “Our customers can easily integrate the new components in their desired power class into their system design and replace conventional lamps with state-of-the-art LED systems.”

Lumentum, ON Semiconductor, and the AI company Ambarella have announced a joint 3D sensing platform for the development of intelligent access control systems and smart video security products such as smart video doorbells and door locks.

The platform is based on Ambarella’s CV25 CVflow AI vision system on chip (SoC), structured-light powered by Lumentum’s VCSEL technology, and ON Semiconductor’s AR0237IR image sensor. Ambarella, Lumentum, and ON Semiconductor demonstrated the platform during CES 2020.

Traditional structured-light solutions need to use both an infrared (IR) camera and a separate RGB camera and typically, a dedicated ASIC for depth processing. This new platform leverages a single

ON Semiconductor AR0237 RGB-IR CMOS image sensor to obtain both a visible image for viewing and an infrared image for depth sensing. The Ambarella CV25 AI vision SoC powers depth processing, anti-spoofing algorithms, 3D facial recognition algorithms, and video encoding on a single chip, significantly reducing system complexity while improving performance.

“Lumentum has worked to enable diverse applications of our VCSEL technology into next-generation 3D sensing products,” said Andre Wong, vice president, product line management, 3D Sensing at Lumentum. “We are excited to partner with Ambarella to help expand the use of 3D sensing in new applications including video security and more broadly AI vision.”

“ON Semiconductor’s RGB-IR sensor technology enables single sensor solutions to provide both visible and infra-red images in security and vision IoT applications,” said Gianluca Colli, vice president and general manager of the Commercial Sensing Division at ON Semiconductor.

“Ambarella’s CV25 computer vision SoC, with its next-generation image signal processor (ISP), brings out the best image quality of our RGB-IR sensor, while providing powerful AI processing capability for innovative use cases in security applications.”

“We are delighted to partner with Lumentum and ON Semiconductor to deliver a hardware platform for the next generation of intelligent access control systems and video security devices,” said Fermi Wang, president and CEO of Ambarella. “Powered by Lumentum’s VCSEL solution, ON Semiconductor’s RGB-IR technology, and our CV25 SoC, it delivers 3D sensing with reduced system complexity as well as improved reliability and security. We look forward to seeing the innovative products our customers will build with this hardware platform.”

Ambarella’s CV25 chip includes a powerful ISP, native support for RGB-IR colour filter arrays, and advanced high dynamic range (HDR) processing, which results in exceptional image quality in low-light and high-contrast environments.

CV25’s CVflow architecture delivers the computational power required for liveness detection and 3D face recognition, while running multiple AI algorithms for advanced features such as people counting and anti-tailgating. CV25 includes a suite of advanced security features to protect against hacking including secure boot, TrustZone, and I/O virtualisation.

The partnership between Trumpf and STMicroelectronics reached a new high in autumn 2019 when Trumpf delivered the one billionth VCSEL to its European partner. Trumpf develops and produces its VCSELs at Photonic Components, a business located at the company’s Ulm site in Germany.

VCSELs are used in smartphones to improve the camera autofocus, enable face recognition to unlock the device’s display, and switch off the display when the user raises the smartphone to their ear when taking a call. Trumpf’s VCSEL technology is now installed in more than 150 models of smartphones from a wide range of leading OEMs.

“We have been working successfully with STMicroelectronics since 2012 and intend to deepen this relationship to unlock the great potential for growth in many consumer electronics segments,” says Joseph Pankert, the managing director in charge of the VCSEL line of business.

“We also see strong growth potential for our VCSELs in other markets including higher resolution time-of-flight cameras. These cameras flood an object or a room with infrared light, measure the round-trip travel time or the phase shift of the emitted light, and calculate three-dimensional models based on this data,” says Pankert.

“Our long-standing technology partnership with Trumpf has reached a hugely significant milestone – the shipment of 1 billion VCSELs for use in our time-of-flight product families,” says Eric Aussedat, STMicroelectronics executive VP and general manager of the Imaging sub-group. “Building on this success, we look forward to further co-work with Trumpf to address the exciting and rapidly growing 3D and depth sensing markets.”

Speciality foundry TowerJazz and Aledia, a developer of 3D LEDs for displays based on its GaN-nanowires-on-silicon platform, have announced their process development partnership to bring Aledia’s novel nanowire-LED technology into volume production.This development is based on Aledia’s IP and uses TowerJazz’s Transfer Optimisation and Development Process Services (TOPS). TowerJazz has both 200 mm and 300 mm wafer options.

“We are very excited to take our technology into its industrialisation phase. We chose TowerJazz due to its vast expertise in the field of process development, its high quality and extensive production capabilities, well serving our long-term production roadmap”, said Giorgio Anania, Aledia’s CEO. “We are looking forward to proceed toward successful collaboration”.

Aledia’s 3D LED novel technology is designed for high brightness, high resolution, low power, and cost-effective displays for laptops, tablets, mobile phones, augmented / virtual reality (AR/VR), and smart watches among others.

“We are very proud to have partnered with Aledia’s team of experts to bring their innovative technology into production phase. This technology provides significant differentiators addressing all the main feature requirements of the microLED displays market and holds profound potential growth for both companies”, said Dani Ashkenazi, VP and general manager of TOPS. “Bringing Aledia’s solutions into volume production is a major step in establishing its role as a leading provider of next-generation display panel technology and we have great confidence in their success”.

Aledia’s nanowire-LED display technology is financed by Intel Capital among others.

IVWorks of South Korea, a manufactures of GaN epitaxial wafers using deep learning-based AI epitaxy technology has raised $6.7 million in Series B funding. As a result, total investment raised by IVWorks now amounts to $10 million.

Participants in this investment included Samsung Venture Investment, a specialised investment company of Samsung, which participated with a follow-on investment subsequent to a seed round, and other new investors such as KB Investment, KDB Bank and Dt&Investment.

IVWorks, the first Korean GaN epiwafer foundry to produce 8-inch GaN-on-silicon epiwafers and 4-inch GaN-on-SiC epiwafers, has recently entered into a contract with US and Korean semiconductor companies and commenced mass production. The investment proceeds are expected to be used for production and a planned capacity expansion, as well as to upgrade the AI-based production system.

A Samsung Venture Investment official revealed the reason behind its investment in IVWorks: “We highly value its technological advantages including the cost competitiveness it has secured through the advanced equipment technology and the defect reduction technology, as well as the revolutionary AI epitaxy technology.

IVWorks’ CEO Young-kyun Noh commented: “GaN power devices, which are more efficient than existing silicon power devices, and which can be miniaturised, are being applied to high-speed chargers, data server power supplies, lidar sensors, etc., thereby rapidly replacing silicon power devices.”

“Additionally, as GaN RF devices are being used as an essential component in 5G communication base stations, the demand for GaN epiwafers, which is a core material in GaN RF devices, is also rapidly rising.”

Thin-film photovoltaic CIGS technology has seen considerable growth of manufacturing capacity in recent years. The environmental impact, especially the CO2 footprint of CIGS thin-film panels, shows many advantages compared to other solar technologies. CIGS panels perform well in diffuse light conditions and at high temperatures.

Additionally, CIGS panels look attractive (and can be produced in custom colours) when used for solar façades on buildings.

Smit Thermal Solutions and solar company Avancis have started a European collaboration with research institutes Helmholtz-Zentrum Berlin (HZB), CNRS (Institut des Matériaux Jean Rouxel, Nantes) and TNO/Solliance to cut the cost of CIGS processing and improve efficiencies.

Called SUCCESS (Sequential, high Uniformity, Cost Competitive Elemental Selenisation and Sulphurisation for CIGSSe2), the project will use heavy alkali post-deposition treatment (PDT) as a way to achieve efficiency of more than 20 percent for 30 x 30 cm2 Avancis’ modules.

“Reaching the efficiency goal of more than 20 percent for a 30 x 30 cm2 module, SUCCESS is set to pave the way for a further reduction of the total cost of electricity generated by the CIGS technology in any application from green field to building integrated PV”, says Jörg Palm, CTO of Avancis.

The non-vacuum Smit Thermal Solutions in-line selenisation equipment is said to provide a high degree of freedom in the CIGS semiconductor fabrication enabling further cost reduction at high efficiency levels.

TNO/Solliance and HZB have already reached high efficiencies at the cell level using Smit Thermal Solutions prototype pilot equipment.

The first steps in scaling-up the process will be to improve the homogeneity of the selenisation process in the Smit Thermal Solutions equipment and adapt it for the 30 x 30 cm2 Avancis R&D platform.

During the last three years, the conversion efficiency of CIGS record cells has been increased from 20.5 percent to 23.35 percent by using controlled PDT of the absorber layer with heavy alkali metals. Typically, these records are achieved with small cells measuring 1 x 1 cm2.

The consortium aims to systematically investigate the impact of the heavy alkali doping in the absorber formation process as well as by PDT of the absorber and to ultimately apply this technology to large-area module production processes with a Cd-free buffer process.

DenseLight is set to take InP lasers to datacoms and sensor markets in China and further, reports Rebecca Pool.

In November 2019, Canada-based optical engine developer, POET Technologies, divested DenseLight Semiconductors, Singapore, to a newly-formed consortium of investors and manufacturers from China, for $26 million.

The move comes three years after POET acquired the InP integrated photonics designer and manufacturer. And as DenseLight president and chief executive, Rajan Rajgopal, tells Compound Semiconductor, the timing was just right.

“When POET acquired DenseLight in May 2016, we were not in such a good financial position, but three years later we are transformed, have recorded healthy year-on-year revenue growth from 2017, 2018 and will continue that in 2019,” he says.

“POET had wanted a fab to develop components for transceiver modules, so in the last three years our primary aim has been to develop both POET’s and our own products,” he adds. “We’ve now been in a position to be sold off for good value and this fits in with POET’s strategy to become a fabless photonics business.”

Indeed, DenseLight’s shareholders, DL Shanghai, comprise China-based investors as well as Chinese industry players, including compound semiconductor device manufacturer Dynax Semiconductor, and an unnamed high-power GaAs laser manufacturer.

“Today, China is the second largest photonics market in the world with the US leading,” points out Rajgopal. “But I think China will surpass the US in the next two-to-three years, and that’s why we want to position ourselves to take advantage of this growth.”

Market focus

Since joining the company in January 2017, Rajgopal has increased DenseLight’s Singapore workforce from 40 to 100 employees, and enhanced operations. As Rajgopal puts it: “When I joined the company, I focused on getting the right people into the business, getting the supply chain in place and developing new products.”

At the same time, DenseLight’s market focus has shifted. While the company initially developed lasers, laser modules, super-luminescent LEDs and diodes for photonic sensing markets, Rajgopal has also been targeting datacoms markets in the last three years in a bid to quickly grow company revenues.

“The sensing market offers a slow and steady 10 to 15 percent compound annual growth in terms of revenue, but we also wanted the fast-paced growth of the datacoms space,” he says. “So we’ve developed lasers for datacoms markets as well, and these are either already in the market or being sampled by customers.”

So far, this strategy looks to be paying off. The company recorded year-on-year revenue growth of 29 percent and 39 percent in 2017 and 2018, and Rajgopal expects to stretch this figure to at least 41 percent in 2019. “We are also working with two of the largest networking players in the world,” he says. “When a small company like us engages with these players, I think that says a lot.”

Excitingly, the company also has ambitious expansion plans, starting with its Singapore facility. According to the DenseLight Chief Executive, the company recently bought a Aixtron G4 MOCVD reactor, adding to its existing Aixtron 200 instrument. “We can now run more than 400 wafers a month, whereas before the G4 that figure was more like 30 wafers,” says Rajgopal.

At the same time, the company has also been growing DFB laser manufacturing in Singapore, buying, for example, new coating tools as well as investing in its assembly and test facilities. The company will continue to invest in the assembly and test capacity in Singapore in 2020, and come 2021 will expand into China.

Here, DenseLight intends to construct an assembly and testing facility, followed by a high-volume wafer fab, to capture anticipated growth in both datacoms and sensing markets in this region.

According to Rajgopal high-volume DFB laser manufacturing – for both sensing and datacoms markets - will take place here. But as he also highlights: “We will put in back-end capacity here as well... we need to increase die output from 300,000 to 5 million to 15 million a year – that’s the kind of volumes we are expecting.”

So beyond 2021, what can we expect from DenseLight? As Rajgopal hints, a future GaAs revenue stream could be on the horizon.

When asked why an unnamed GaAs laser manufacturer is manufacturing in the company, he replies: “We have worked on a GaAs edge-emitting laser for a super-luminescent LED product and while we don’t have a product today, we have the capability for potential future development.”

But for now, all eyes are on developing the company’s InP presence in China, where Rajgopal anticipates continued growth across both datacoms and sensing markets. “Datacoms is big in the US and China as every fibre-optic cable needs an InP laser, but while sensing markets are stable in the US, I see this business picking up in China,” he says. “So many new industrial robots are being deployed in factories in China and these all need fibre-optic sensors with a super-luminescent LED as the light source.”

“So that’s why we are positioning ourselves with a fab and back-end facility in China,” he adds. “There are few indium phosphide-based companies that grow their own epi-wafers, manufacture and test the wafers – I think this places us in a unique position to gain market share all over the world.”

Beijing downtown district scenery at night

TRADE & INVEST WALES COMPOUND SEMICONDUCTORS

For more information on Trade & Invest Wales visit tradeandinvest.wales

The world’s first compound semiconductor cluster is taking shape in South Wales. It’s a unique partnership of universities, research centres and innovative companies, all driving forward the technology to power the next industrial revolution

When explaining the potential of compound semiconductors, Sam Evans of Newport Wafer Fab uses a simple analogy. “The first industrial revolution relied on steam,” he says. “That made the magic happen. Today, compound semiconductors are the steam – the enabling power – for what’s being called the fourth industrial revolution. And we have all the process knowledge to create that steam in Wales.”

Compound semiconductors are already becoming ubiquitous – in fibre optic communications, in digital media and sensing, including 3D face recognition, and in the circuitry of almost every smartphone. But as the latest technological revolution promises to turn both work and leisure upside down, their importance can scarcely be overstated.

“We’re talking about applications like 5G communications and artificial intelligence, or enabling truly autonomous vehicles,” says Kevin Crofton, president of SPTS and chairman of the Compound Semiconductor Applications Catapult. “These types of applications demand very high-speed transmission rates to allow instantaneous decision-making. When a driverless vehicle needs to decide how to avoid an impending accident or whether there’s a pedestrian in front of it, you can only afford nanoseconds of delay in decision making and action.”

The South Wales cluster, branded as CSconnected, brings together research and development competence and industry expertise with almost a complete supply chain in a very concentrated geographical area. Four companies at the heart of the Welsh cluster are: IQE, which makes the wafers; Newport Wafer Fab, which processes the chips; packaging specialists Microsemi, a wholly owned subsidiary of Microchip Technology; and SPTS Technologies, a KLA company, which makes wafer processing equipment used by manufacturers.

They work closely with the five development partners – organisations and institutions directly involved in R&D and innovation. Core research is carried out at the Institute for Compound Semiconductors at Cardiff University, which will be joined by Swansea University’s Centre for Integrative Semiconductor Materials. Product, services and skills development are the responsibility of the Compound Semiconductor Centre (CSC) – a collaboration between IQE and Cardiff University that offers cutting-edge facilities to help researchers and industry work together. The Compound Semiconductor Applications Catapult focuses on helping the industry sector to exploit the advances made by researchers in key areas such as healthcare, the digital economy, energy and space. Lastly, a Future Compound Semiconductor Manufacturing Hub will conduct research into large-scale manufacture of the devices.

It’s an impressive offering, and one that has attracted significant investment from research investment funds and government at regional, Welsh and UK level. “We see the power in clustering and having regional capabilities, just like Silicon Valley in the 1960s,” says IQE’s Chris Meadows. “Once you’ve reached a critical mass, you get what I like to call the Hay-on-Wye effect. You may think, ‘Why would you have so many bookshops competing with each other?’ but the point is that people know there are lots of bookshops, so they all go there.

“It’s the same with Silicon Valley. It attracted people into the region because they knew they could build a career – they could move from one company to another. And it provides opportunities to grow the cluster. Not only do you attract people in, you attract further elements of the supply chain.”

Jim Ryan, director of worldwide module operations at Microsemi, a subsidiary of Microchip Technology, agrees. “It’s why we wanted to be part of the cluster,” he says. “We could see a real opportunity for Wales if it offered fully integrated semiconductor solutions for customers in a one-stop shop. It means we can grow Wales’ economy by many times what would be possible if all we did was produce the chips themselves.”

And for the foreseeable future, the South Wales cluster is likely to remain the only one of its kind. Kevin Crofton says: “There isn’t a region in the world right now that has the breadth of compound semiconductor capability that exists here. If we can attract and retain talent, and get the educational systems aligned with our vision, we’ll be a centre of excellence for the world – not just for the UK or Wales.

“It could be a worldwide phenomenon. We have the potential. We could evolve into a Silicon Valley for the compound semi-conductor arena.”

Combining AlN or InAlN barriers with SiN passivation layers leads to exceptional performance for GaN RF devices, regardless of the choice of substrate.

By Markus Behet, Joff Derluyn, Stefan Degroote and Marianne Germain from EpiGaN/SoiteC

The roll-out of 5G is great news for GaN. It is predicted to propel the market for RF devices made from this wide bandgap semiconductor to more than $2 billion by 2024, according to the French market analyst Yole Développement.

The move from 4G to 5G should be seen as part evolution, part revolution. Grabbing the most attention is the availability of enhanced mobile services, resulting from faster speeds, ultra-low latency, and a reduction in power consumption. However, 5G will also bring further investment in traditional machine-to-machine and internet-of-things applications, and open up new market opportunities in mission critical services, such as autonomous vehicles, drones and ‘telehealth’. It is even expected that 5G will act as a catalyst for transformative changes of work processes, and will establish a new set of rules for competitive economic advantages. So great are these changes that IHS Markit forecasts 5G to enable $13.2 trillion of global economic output in 2035.

As 5G networks are rolled out, there will be far greater densification at the macro scale. More base stations will appear, featuring devices operating at far higher power densities. But that’s not the only change. To alleviate the load on macro cells, there will also be an emergence of smaller network cells – known as pico and femto cells – to increase network capacity and provide extended coverage.

5G deployment is also changing the frequencies of the RF signals, and the way they are transmitted and received. It is designed not only for spectral bands below 3 GHz, where most mobile communications happen today. It also utilises mid bands between 3 GHz to 6 GHz – a spectral domain known as sub-6 GHz – and new frequency bands previously thought unsuitable for mobile communications, such as high bands in the millimetre-wave region, above 24 GHz. In both these domains, bandwidths exceed 100 MHz. A further increase in throughput and data rates comes from a switch from a standard antenna architecture to one that is based on the multiple input and the multiple output of many signals – this is referred to as massive MIMO. And yet another advancement is active antenna beam steering at the base station, to maximise spectral efficiency.

Increased deployment of small cell antennas during the roll-out of 5G will drive demand for compact, highly efficient RF devices. Designers of massive MIMO systems may find it even more challenging to manage power consumption and heat dissipation than the complexity of antenna arrays. In 4G systems, there has been a priority on the power consumption of the power amplifier when designing base station heat sinks and power supplies. But now concerns are shifting, because power consumption of the signal processing electronics in 5G massive MIMO systems is approaching that of the power amplifiers. This means that semiconductor efficiency will become key.

For both 5G infrastructure and handset architectures, mandatory attributes for RF semiconductor devices are efficiency, compactness, low cost, high power density and linearity. Judged in terms of wideband performance, power density and efficiency, legacy technologies – essentially silicon LDMOS or GaAs – are no match for GaN HEMTs, regardless of whether they are grown on silicon or SiC. It is this technology that is meeting stringent thermal specifications for 5G, while preserving valuable PCB space for the tightly clustered mMIMO antenna arrays. In base stations, discrete designs are already being replaced by space-saving multi-function GaN MMICs and multi-chip modules.

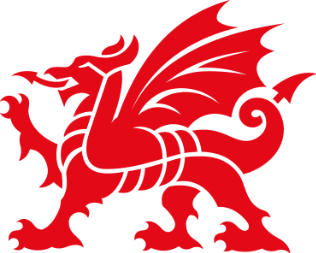

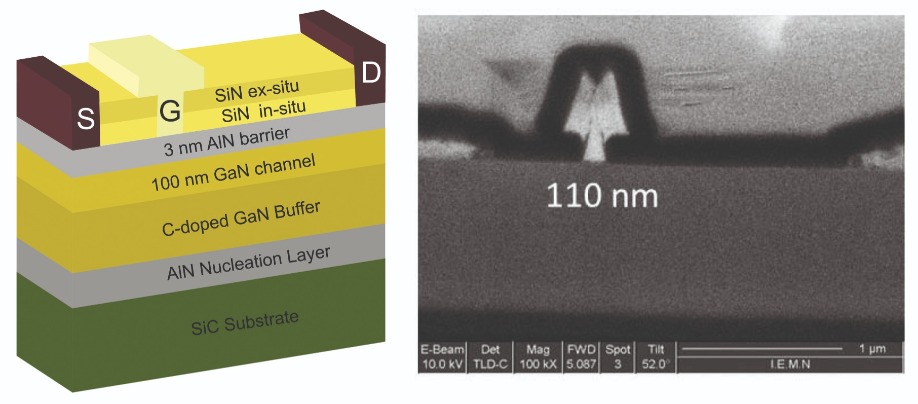

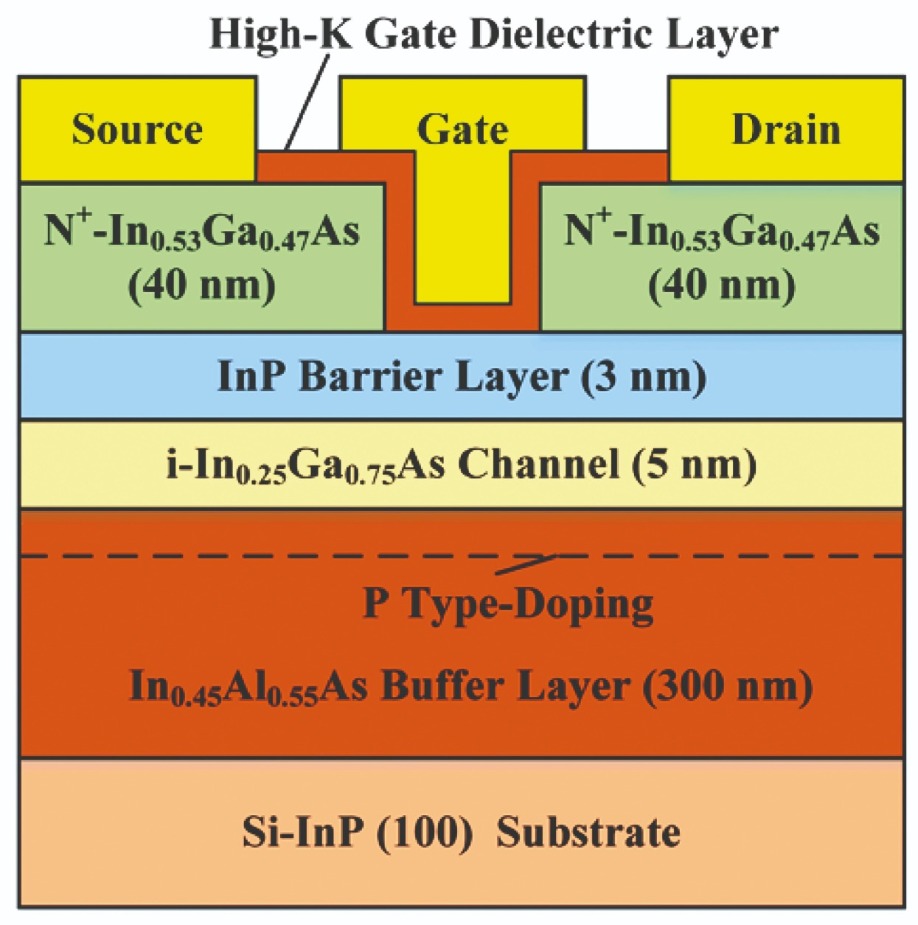

Figure 1. A typical GaN HEMT heterostructure.

When producing GaN HEMTs, an important decision is the choice of substrate. Semi-insulating SiC is selected to meet the need for ultimate power levels in the most demanding applications, while silicon’s strengths are related to low-costs, large diameters and high-volumes.

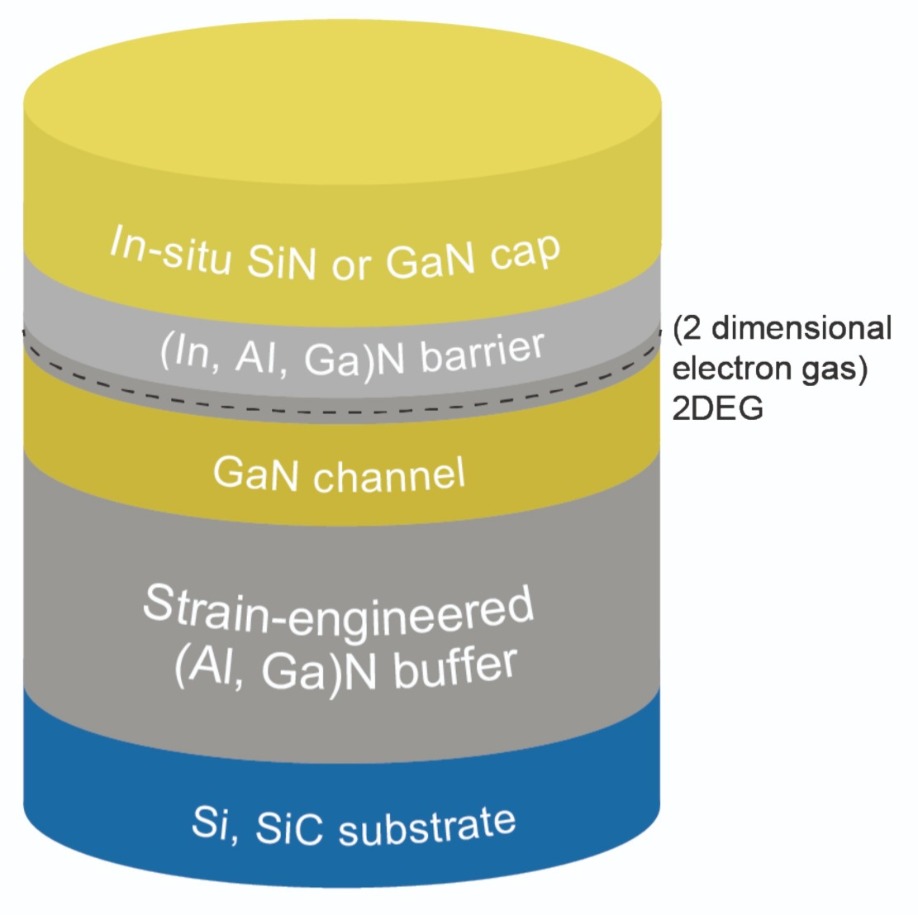

Figure 2. Transmission electron microscopy of an in-situ SiN-capped AlGaN/GaN HEMT structure showing the nature of the SiN. This material is crystalline close to the interface to the barrier, and amorphous when further from it.

At epiwafer supplier EpiGaN, now part of Soitec, we leave it to our customers to decide whether a SiC substrate, or one made from silicon, is the best choice for their RF application. Our focus is to produce the best GaN HEMT heterostructure for a specific application on each of these foundations, through judicious choice of the barrier and the cap layer.

In order for GaN-on-silicon to compete directly with GaN-on-SiC in high-end RF applications, a few technical hurdles have to be overcome. Some of these are intrinsic, including the lower thermal conductivity of silicon compared with SiC – in this case, the solution is an aggressive reduction of the substrate thickness to 50 µm. But there are also other issues, such as the conductive interface that is formed between the silicon substrate and the III-nitride buffer layer during epitaxial deposition. This parasitic conduction path is highly detrimental, as it capacitatively couples to the HEMT channel. It is to blame for the undesired dissipation of RF signals, which increase with frequency. When transistors are manufactured on such lossy substrate/buffer combinations, they fail to deliver good performance at high frequencies, in terms of gain, power and efficiency.

To suppress this undesirable conductive path, we have developed and optimised a robust interface technology. This trims RF signal loss on GaN-on-silicon material to well below 0.4 dB/mm for frequencies up to Ka-band. Such a low loss enables the RF performance of GaN-on-silicon HEMTs to get very close to that of their GaN-on-SiC cousins. Using this process, which can be used on high-resistive silicon substrates up to 200 mm diameter, we have produced epiwafers that are ideal for making devices for the 5G sub-6 GHz and millimetre-wave frequency bands.

Figure 3. 110 nm gate length GaN-on-SiC HEMT structure using a 3 nm AlN barrier capped with 10 nm in-situ SiN; courtesy of F. Medjdoub, IEMN, Lille.

Today, the workhorse for RF power amplifiers operating in sub-6 GHz bands is a GaN-on-SiC HEMT with a 20 nm-thick AlGaN barrier that has an aluminium content of around 25 percent. This ternary barrier is capped and protected by an ultra-thin GaN layer, typically 2-3 nm thick (see Figure 1).

Our view is that there are times when this mainstream barrier may not be the best choice in more demanding millimetre-wave band and low-voltage applications. For these cases, we have developed heterostructures that combine an in-situ SiN protecting layer with either a binary AlN layer or a lattice-matched InAlN barrier. We will now outline the merits of both these options for the barrier.

One of the strengths of the binary AlN barrier it that it allows a reduction in the thickness of this layer from typical values of around 20 nm to between just 3 nm and 6 nm. This opens the door to bringing the transistor gate very close to the densely populated channel, and in turn maximising the electrostatic coupling between the two – this leads to improved gate control, and ultimately superior RF transistor characteristics.

For example, the transistor’s transconductance increases when the gate is brought closer to the channel. In addition, there is a suppression of short channel parasitic effects, which can impair transconductance when scaling transistor gates below 0.15 µm. Another benefit of the AlN barrier is that it has a very high inherent piezoelectric effect, resulting in carrier densities in excess of 2 x 1013 cm-2 in the transistor’s two-dimensional electron gas. This leads to a hike in power density, and also a significant reduction in chip size, so long as an appropriate thermal chip layout is used.

By turning to InAlN, rather than AlN, it is possible to produce a lattice-matched barrier by using the alloy In0.17Al0.83N. Pairing this ternary with GaN is attracting much attention, because this combination has a large spontaneous polarization, but is not impaired by a high degree of strain, which is found in AlGaN/GaN. These merits enable heterostructures of InAlN/GaN to have significantly higher sheet carrier densities than those of AlGaN/GaN, while maintaining good electron mobility. At the device level, this means that HEMTs have higher maximum current capabilities, a valuable asset for high-power devices operating up to millimetre-wave frequencies.

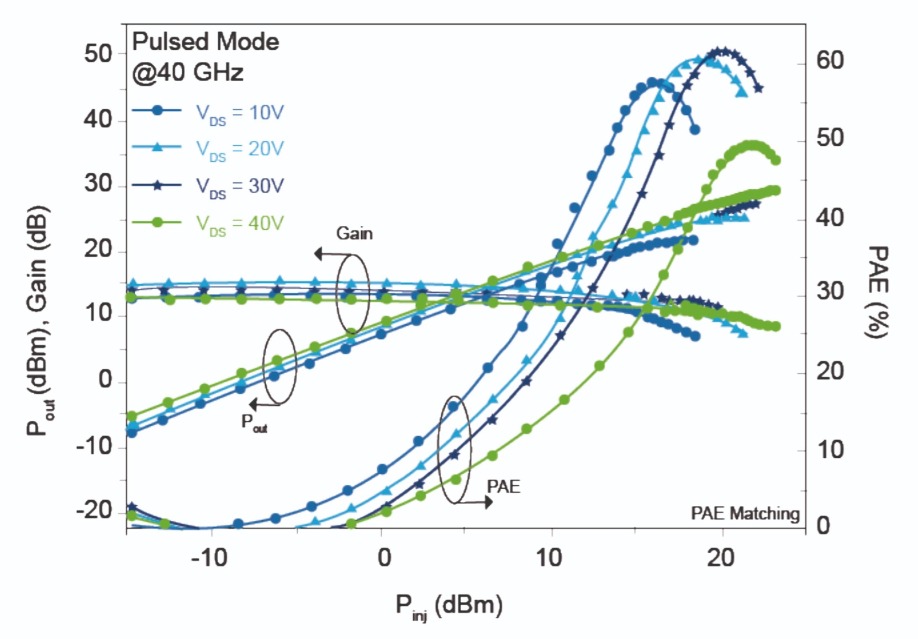

Figure 4. Pulsed power performance at 40 GHz of a 2 x 50 µm AlN/SiN HEMT (gate length 110 nm, gate-to-drain spacing of 1.5 µm) at Vds of 10 V, 20 V, 30 V and 40 V*, *power matching only; courtesy of F. Medjdoub, IEMN, Lille.

On the top of our epiwafers we add a high-quality SiN layer, grown in-situ by MOCVD. As the first few monolayers of the SiN are crystalline, the interface trap density is very low (see Figure 2).

This SiN layer can serve many purposes. It can provide surface passivation, sealing the top of the GaN wafers directly after growth; it can be used as a gate dielectric; it can stop relaxation of the strained barrier layers; and it can prevent exposure of III-N layers to the fab environment, enabling the processing of GaN-on-silicon wafers in silicon CMOS fabs.

Yet another benefit of the in-situ SiN capping layer is that it controls the filling of the surface states during device operation. This can combat current collapse, which is associated with the depletion of the two-dimensional electron gas. Current collapse is avoided because the addition of SiN provides enough charge to neutralize the surface charge of the AlGaN barrier layer, so that its surface potential no longer contributes to the two-dimensional electron gas depletion. Finally, when SiN layers are added to HEMTs, these devices have a superior stability at high temperatures.

Millimetre-wave merits

For devices operating in the 5G millimetre-wave bands, a premium is placed on performance at high frequencies. HEMTs are scrutinised for their gain, power density and power-added efficiency, and this reveals that those that are made from standard AlGaN/GaN heterostructures are not the best choice for Ka-band 5G massive MIMO antenna systems. A better option for these challenging specifications are designs that feature ultra-thin AlN or lattice-matched InAlN barriers in combination with in-situ SiN cap layers. HEMTs with these hallmarks deliver excellent performance, by suppressing short-channel effects while simultaneously realising the highest current densities.

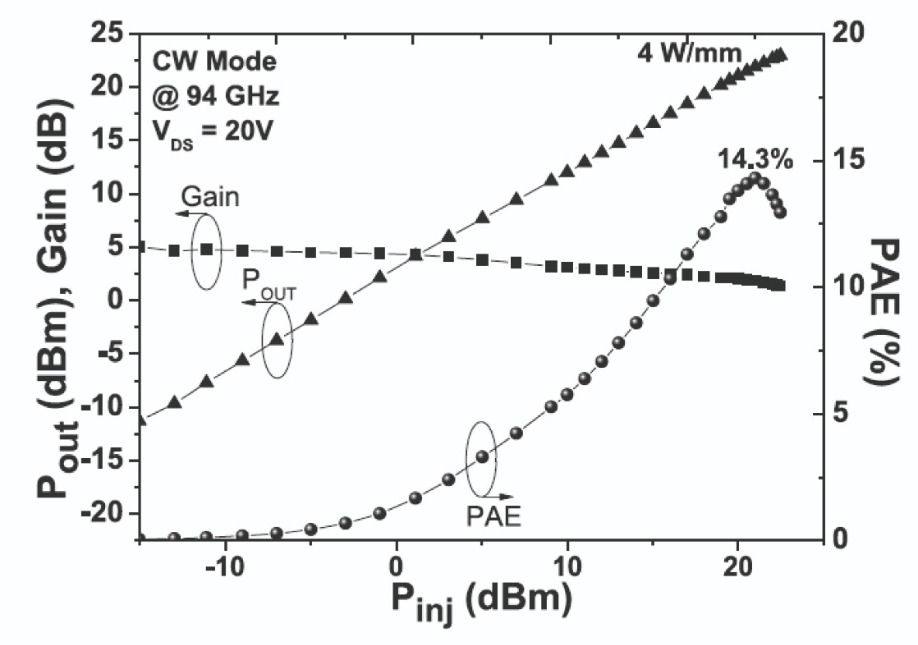

Figure 5. Continuous-wave power performance at 94 GHz of a 2 x 25 µm AlN/SiN HEMT (gate length 110 nm, gate-to-drain spacing of 0.5 µm) at Vds=20V; courtesy of F. Medjdoub, IEMN, Lille.

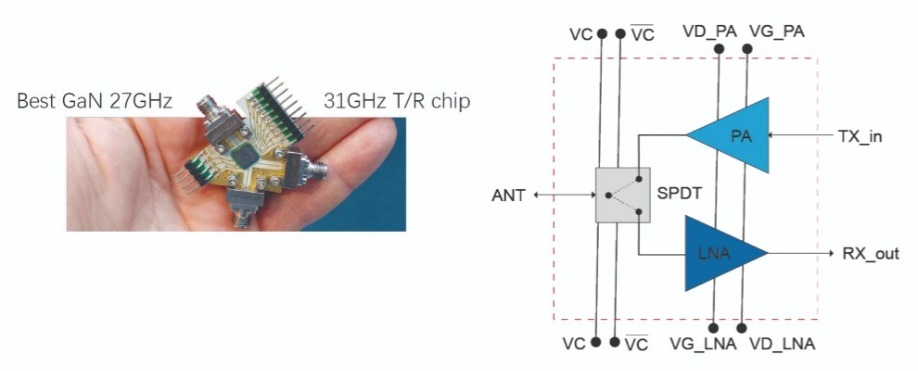

We have also collaborated with Ommic, a leading 150 mm European GaN foundry, to provide further proof of the performance of devices produced with our material. Ommic has developed a 100 nm gate-length, open foundry MMIC process with a complete design kit on our SiN/AlN/GaN-on-silicon HEMT technology.

The devices produced in the Ommic line provide further verification of the superiority of GaN HEMTs made with our material over standard GaAs pHEMT processes. The breakdown voltage is much higher, hitting 40 V, and this leads to a much higher Ka-band output power density – it is 3.5 W/mm at 30 GHz – alongside a higher robustness to input mismatch conditions.

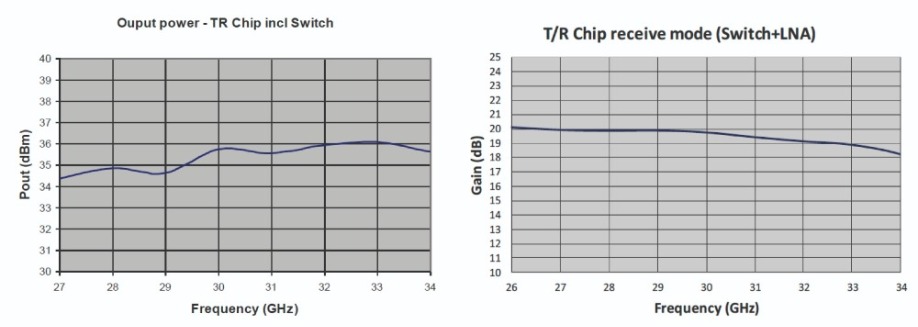

Figure 6. Fully integrated millimetre-wave 5G 26-34 GHz transmitter/receiver product utilising EpiGaN’s GaN-on-silicon RF HEMT epiwafer technology; courtesy of Ommic, Limeil Brévannes, France.

Figure 7. Transmitter power amplifier output power and receiver small-signal gain of a millimetre-wave 5G GaN-on-silicon transceiver MMIC shown in Figure 6; courtesy of Ommic, Limeil Brévannes, France.

At the same time, GaN-on-silicon is quickly closing the performance gap, while offering an attractive opportunity to drive down costs through economies of scale. This is helping RF GaN technology to start to enable innovations in many existing applications.

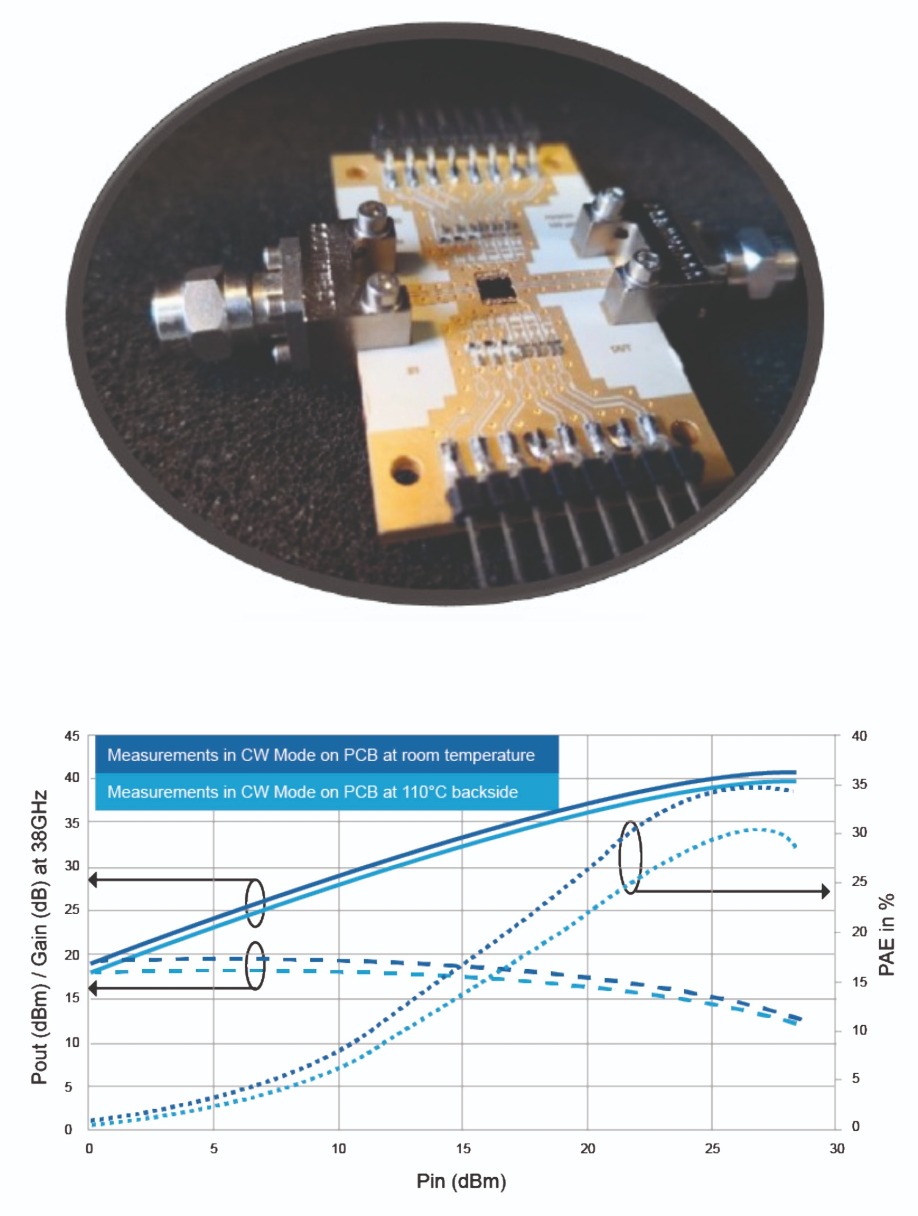

Figure 8: Output power, gain and power-added efficiency of a 5G 40 GHz GaN-on-silicon power amplifier; courtesy of Ommic, Limeil Brévannes, France.

What about the smartphone, now the holy grail for every semiconductor technology? At first glance GaN is not ideal, as the higher supply voltages – typically 10 V or more – are not well suited to handsets, which typically use between 3 V and 5 V. But that’s not a show-stopper as this gap can be bridged with device process adaptations. Some of the biggest component suppliers in the handset business are already discussing GaN-on-silicon for 5G millimetre-wave enabled smartphones.

Standards will continue to evolve, due to the introduction of carrier aggregation and the ever increasing performance requirements for multi-mode, multi-band power amplifiers. This may play into the hands of RF GaN-on-silicon technology, which offers the inherent benefits of scaling, and could soon become a strong contender for 5G mobile devices.

Techniques for supressing degradation in SiC p-i-n diodes and IGBTs, enhancing channel mobility in SiC MOSFETs, and improving the blocking voltage and on-resistance of Ga2O3 transistors were all unveiled at the most recent IEDM meeting.

BY RICHARD STEVENSON

TURN ON THE NEWS and there’s a good chance you’ll hear a story related to climate change. Recently the focus has been on the devastating fires in Australia, but in the last few months you may also have read of accelerated ice-melting in Greenland, demolition of homes in Rwanda to protect citizens from flooding, and the breaking of global temperature records.

For those of us that see climate change as man-made, our challenge is to modify our lifestyle, so that we help to curb carbon emissions. Some of the changes that we could consider may not be to our liking, such as switching to a more plant-based diet and taking fewer flights to sunny climes. But there is one change that we will applaud: far greater deployment of more-efficient power electronics, based on devices made from alternatives to silicon.

Leading this charge is SiC. Sales of diodes and transistors made from this material are ramping fast, as the uptake of these devices branches out from their deployment in power supplies and inverters to electric vehicles, where they enable an extension to the driving range. Far behind, but with even greater promise, is gallium oxide, a material with an even wider bandgap. It will not be long before the first commercial Ga2O3 devices appear on the market, but significant sales are still some years away.

For both SiC and Ga2O3, long-term success hinges on making the devices better and better. Performance must improve, alongside reliability. To succeed, more research is needed to understand the behaviour of the diodes and transistors, and how modifications to designs impact device behaviour.

Presentations detailing progress of this nature were detailed at the latest International Electron Devices Meeting (IEDM). Held in San Francisco between 7 and 11 of December, researchers at IEDM 2019 described techniques to suppress bipolar degradation in SiC p-i-n diodes and IGBTs, improve the characteristics of the channel in SiC MOSFETs, and a Ga2O3 transistor architecture that sets a new benchmark for breakdown voltage.

Supressing bipolar degradation

Sales of SiC power devices are dominated by Schottky barrier diodes and MOSFETs. Within this commercial product portfolio there are devices designed to operate between 600 V and 3.3 kV. Higher voltages are possible, but for values of 10 kV and above, SiC p-i-n diodes and IGBTs appear to be better alternatives. However, if this pair of devices are to fulfil their potential, a condition known as bipolar degradation must be addressed. This degradation occurs when current passes through these devices and stacking faults arise, leading to an increase in forward voltage. Note that a solution to this impediment could have wider implications, as this type of affliction may also occur in body p-n diodes of SiC MOSFETs.

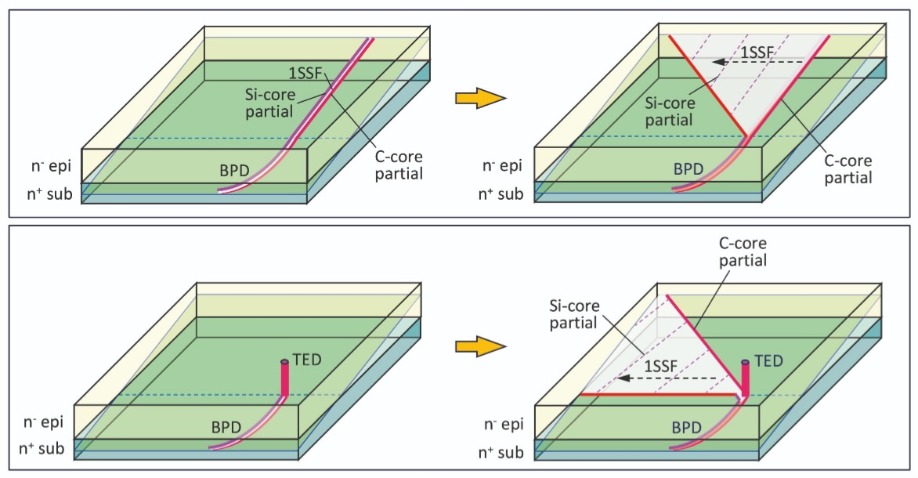

Figure 1. Basal plane dislocations (BPDs) in the substrate can propagate into the epilayer (top left), or be converted into threading edge dislocations (TEDs). Most of the BPDs in the epilayer contain a pair of partial dislocations – one with a silicon core, and the other with a carbon core – with a single Shockley stacking fault (1SSFs) between them. Once the carrier density exceeds a threshold, there is an expansion of 1SSFs from the BPDs in the epilayers to create a right-angled triangular 1SSF (top right). This expansion forms across the current pass of the device, leading to an increase in forward voltage. There can also be an expansion of 1SSFs, involving bar-shaped 1SSFs to expand from the BPD segment below the BPD-TED conversion point (bottom right). This can be caused by the injection of minority carriers into a region below the BPD-TED conversion points located near the epilayer and substrate interface, and also in substrates with a high density of BPDs.

When basal plane dislocations are in the epilayers, once the carrier density exceeds a threshold, there is an expansion of single Shockley stacking faults (see Figure 1). Eventually, right-angled triangular single Shockley stacking faults are formed across the current pass of the device, leading to an increase in forward voltage.

At IEDM several approaches to combat bipolar degradation were described by Hidekazu Tsuchida from Japan’s Central Research Institute of Electric Power Industry (CRIEPI).

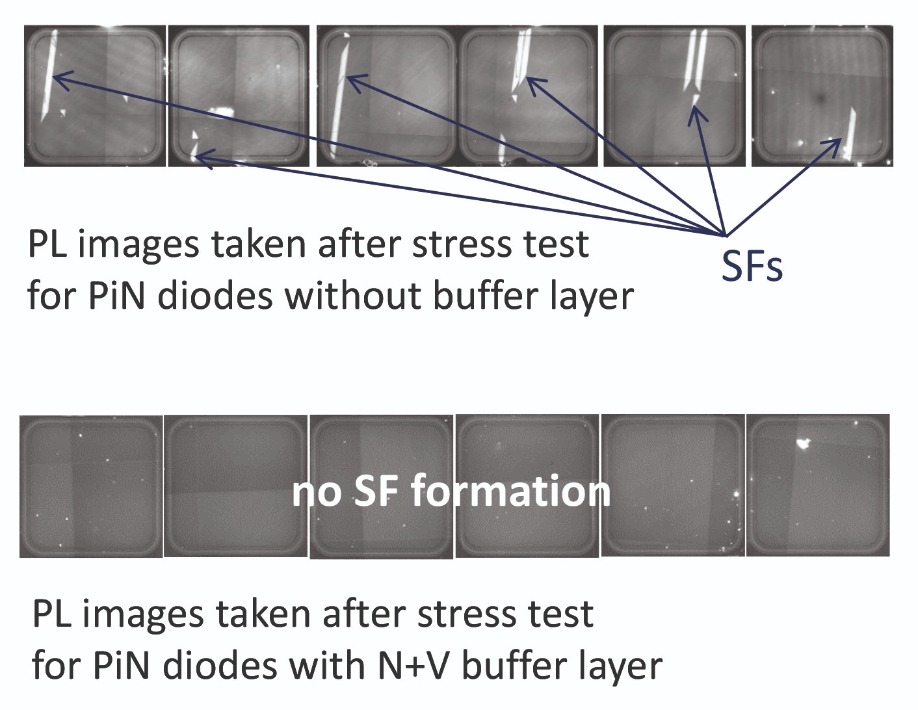

Figure 2. Photoluminescence measurements on p-i-n diodes that have been subjected to a stress test show that the addition of a buffer layer (bottom set of devices) eradicates the formation of single Shockley stacking faults.

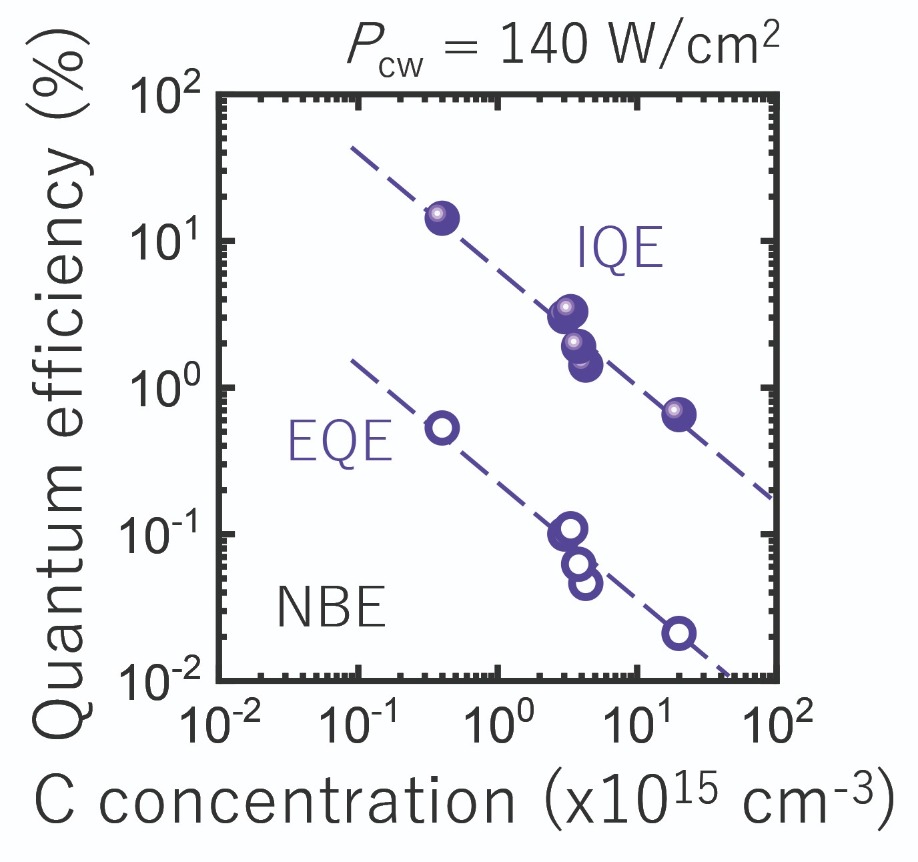

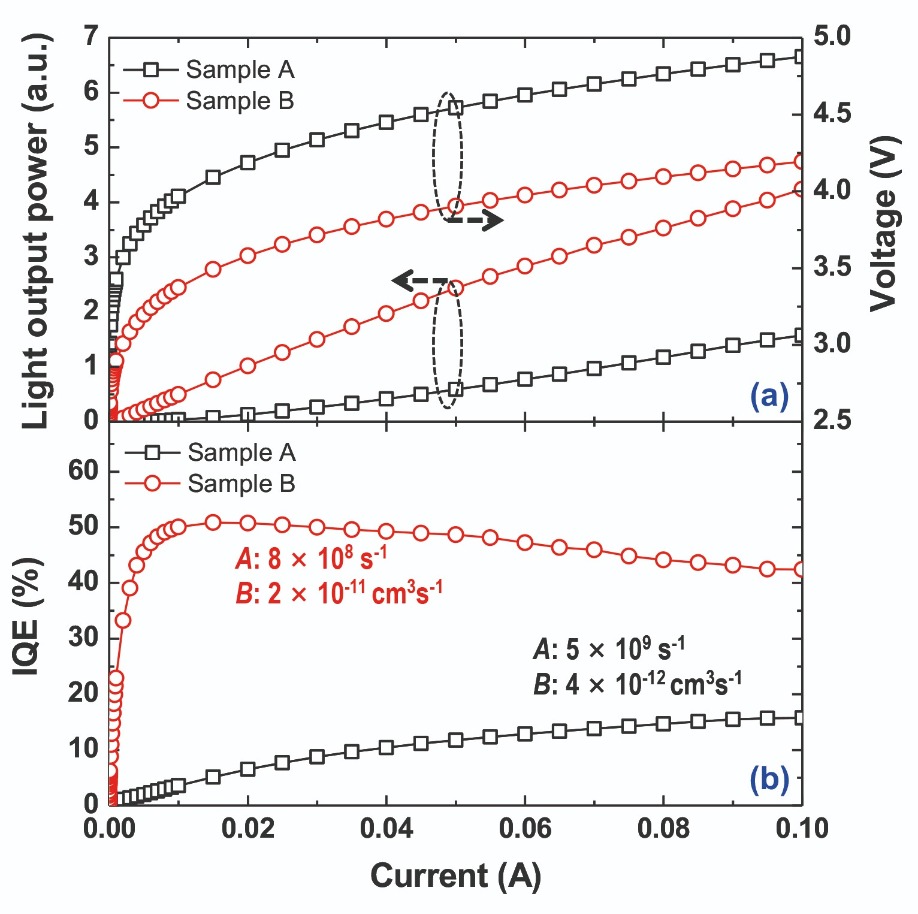

Back in 2018, Tsuchida and co-workers reported a study involving the fabrication of SiC p-i-n diodes. This effort involved using electroluminescence to determine the threshold current associated with the expansion of single Shockley stacking faults. By measuring the charge in the drift layer during turn off, the researchers converted the current density to a hole density. This revealed that the threshold for the hole density in an n-type layer is 1-2 x 1015 cm-3.

Based on this insight, Tsuchida and co-workers argue that two criteria must be met to ensure the suppression of bipolar degradation. They are the elimination of basal plane dislocations from the region where minority carriers are injected, and the reduction in the minority carrier density to a level below threshold in the region where basal plane dislocations exist.

According to Tsuchida, both these requirements are needed because even if basal plane dislocations in the substrate are perfectly converted to threading edge dislocations at the interface between the epilayer and the substrate, minority carriers are still injected into the substrate. Here, the danger is that the density of these carriers exceeds the local threshold, triggering conversion of the basal plane dislocations in the substrate into stacking faults.

Figure 3. Ga2O3 transistors with multiple fins have broken the record for the blocking voltage for this class of transistor. A portfolio of devices has been produced, with fin channel widths ranging from 0.15 µm to 0.45 µm, and pitch sizes from 1.2 µm to 2 µm.

Initially, the team turned to nitrogen doping to reduce the carrier lifetime in the buffer. However, when the nitrogen concentration exceeded 1-2 x 1019 cm-3, this introduced an imperfection known as a double Shockley stacking fault. Keeping the nitrogen concentration low enough to avoid this shortened the carrier lifetime to around 40 ns.

To further reduce this lifetime, Tsuchida and co-workers have recently switched to doping with vanadium, a deeper dopant. When present at a concentration of just 7 x 1014 cm-3, room-temperature carrier lifetime is shortened to just 13 ns.

The benefit of vanadium doping has been assessed by comparing two sets of SiC p-i-n diodes. Controls features a 10 µm-thick, nitrogen-doped drift layer grown on an n-type substrate, and modified variants have an additional buffer, doped with vanadium and nitrogen, inserted between the substrate and drift layer.

To evaluate the impact of the buffer, measurements were made on 16 controls and 16 variants. Initial forward voltages, recorded at a 18 A drive current, were compared with values after one stress test and then another. The first involved driving diodes at 300 A cm-2 for an hour, and for the second, devices were run at 600 A cm-2 for an hour. Analysis of the results showed that the buffer layer leads to a substantial reduction in variation of forward voltage after operation.

Further insight into the difference between standard devices and those with a doped buffer has come from photoluminescence measurements. This optical technique exposed single Shockley stacking faults in the conventional diode, and the absence of these faults in the modified design (see Figure 2).

Buffer layers may also benefit SiC IGBTs. This type of device would require a p-type buffer layer with a short carrier lifetime. Aluminium, which forms a shallow acceptor, is a candidate for doping, as increases in its concentration reduce carrier lifetime. Tsuchida and co-workers suggest that this might be combined with boron, which greatly shortens carrier lifetime.

One of the goals for the team is to map, with precision, the locations across a wafer where basal plane dislocations are converted into threading edge dislocations. Such a study promises to enable a more detailed, quantitative understanding of the expansion of single Shockley stacking faults, and could also aid the development of drift and buffer layers that improve the performance of bipolar devices.

Another target for the researchers is the development of a fast growth technique for making 4H SiC that will trim the density of basal plane dislocations and threading dislocations. The team have already made much progress, realising a growth rate of 3 µm/hour. “[That’s] about ten times higher than a typical PVT growth,” says Tsuchida.

Figure 4. A scanning electron microscopy image of the fins in the Ga2O3 transistors highlight the near-vertical sidewall profile produced by dry etching.

The introduction of a new dopant is also behind the improvements made to the performance of SiC MOSFETs. This success, realised by a team from Mitsubishi, involved the introduction of oxygen doping. It led to a significant reduction in channel resistance and an increase in the threshold voltage.

Both of these attributes are highly desired by the designers of power electric systems. Reducing resistance cuts energy losses, and a higher threshold voltage makes it easier to control the system.

Normally these improvements are realised by nitridation. However, if the threshold voltage exceeds 3 V, this comes at the expense of a hike in channel resistance.

The team from Mitsubishi have previously addressed this weakness by switching to sulphur. And at IEDM they revealed the results of using another alterative, oxygen, which is a far deeper donor. Spokesman for the team, Munetaka Noguchi, claims that there are no downsides to the use of deep donors. He arrived at this conclusion after considering the results of pulsed measurements that enable an estimate of threshold voltage stability.

Noguchi and co-workers have produced vertical and lateral SiC MOSFETs with oxygen doping. For commercial sales, vertical MOSFETs are preferred. “We used lateral MOSFETs as a test structure to evaluate channel performance,” explains Noguchi.

Ion implantation provided a relatively high concentration of oxygen near the channel. Note that such a high concentration is not possible with simple thermal oxidation. Following thermal activation of oxygen, the team formed the gate oxide with thermal oxidation and nitridation in dilute nitrogen oxide.

Measurements of the capacitance of the MOS capacitors in the lateral MOSFETs revealed that at elevated temperatures the introduction of oxygen increases capacitance in the depletion region. This work also revealed that oxygen acts as a donor, rather than an acceptor-like trap.

Additional benefits of the introduction of oxygen in lateral SiC MOSFETs include a 46 percent reduction in channel resistance, realised for a threshold voltage of 3.9 V.

Figure 5. Multi-fin Ga2O3 transistors produce by a partnership between researchers at Cornell University and Hosei University have broken the record for blocking voltage for this class of device. Note that the on-resistance is normalised using an effective conduction width of about 10 mm, as normalising this resistance to the source contact area would grossly over-estimate the figure of merit.

When using any deep level donor, there is an increase in the threshold voltage drift at elevated temperatures. “However, the magnitude is suppressed in the oxygen doped sample,” says Noguchi. Compared to sulphur, this shift is almost halved.

Another benefit of using oxygen rather than sulphur is that it produces a smaller shift in negative bias temperature instability. This indicates that the reliability of the gate is better – it is, in fact, comparable to that in a conventional device.

Noguchi and co-workers will continue to investigate the impact of deep level donors on the electrical characteristics of the MOSFET. In particular, they will consider its ruggedness as a power switching device.

Another option for decreasing the resistance of a SiC MOSFET is to use a trench architecture. This design also allows a smaller cell pitch, leading to an increase in channel width.

However, the trench MOSFETs that have been fabricated on commercial SiC (0001) substrates are failing to fulfil their promise. The field-effect channel mobility is lower than that expected for planar MOSFETs, for reason that are not clear.

To shed light on this matter, a team from Toyota Central R&D Labs has tried to determine the mobility in the channel. To extract an accurate channel resistance, they remove parasitic series resistance from their calculations.

According to the researchers, the key to calculating the field-effect channel mobility is to determine the threshold voltage. Due to the high density of charge traps at the interfaces of SiO2 and SiC, there are inaccuracies associated with calculations of threshold voltage that are based on linear extraction. To avoid this, the team determines the threshold voltage by drawing on values of the ideal threshold voltage and experimental measurements of the relationship between the drain current and the gate voltage.

The first step towards this involved growing n-type and p-type epilayers of SiC on a heavily doped n-type SiC substrate. After adding source and drain regions, the researchers fabricated a trench gate. Following trench etching, they used three different forms of high-temperature annealing to produce different surface morphologies in the trench walls. To complete the fabrication of the structure, they added a 75 nm-thick layer of SiO2, followed by nitridation of the device in diluted nitrogen oxide.

Plotting the drain current as a function of gate voltage at a range of temperatures enabled the team to calculate the density of fixed charges and the distribution of interface states. From these values, the researchers concluded that the interface states contribute to Coulomb scattering.

To relate the level of scattering to the quality of the channel, the team scrutinised the surface morphology of the trench sidewalls with atomic force microscopy. This revealed a significant difference in the roughness of the three samples. By combining this finding with the electrical measurements, they deduced that Coulomb scattering is suppressed when the trench sidewalls are flat enough to form atomic steps and terraces. In this case channel mobility is higher, due to a decrease in the distribution of interface states that arises from dangling bonds at the edge of the step region.

Record-breaking voltages

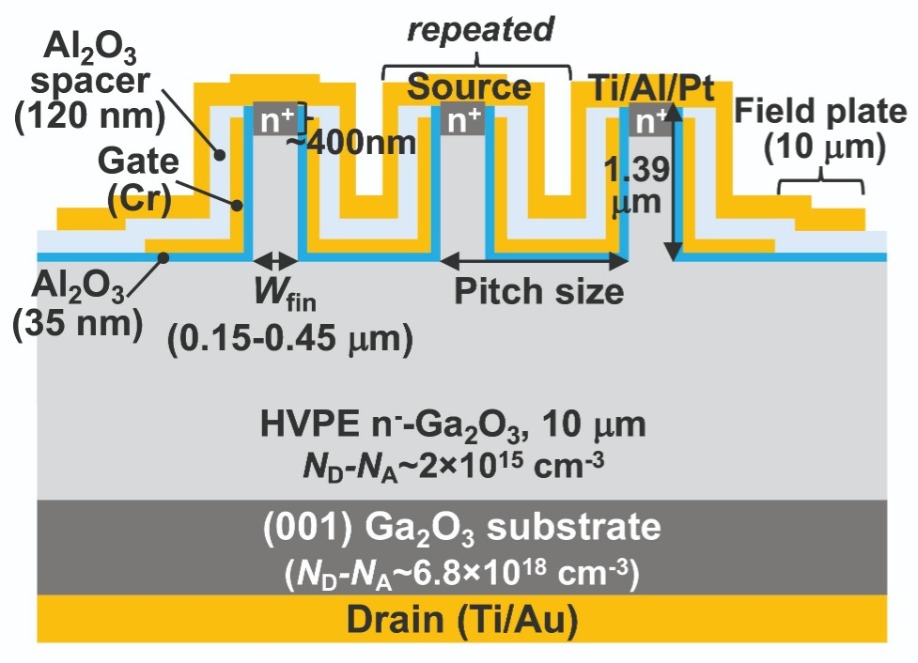

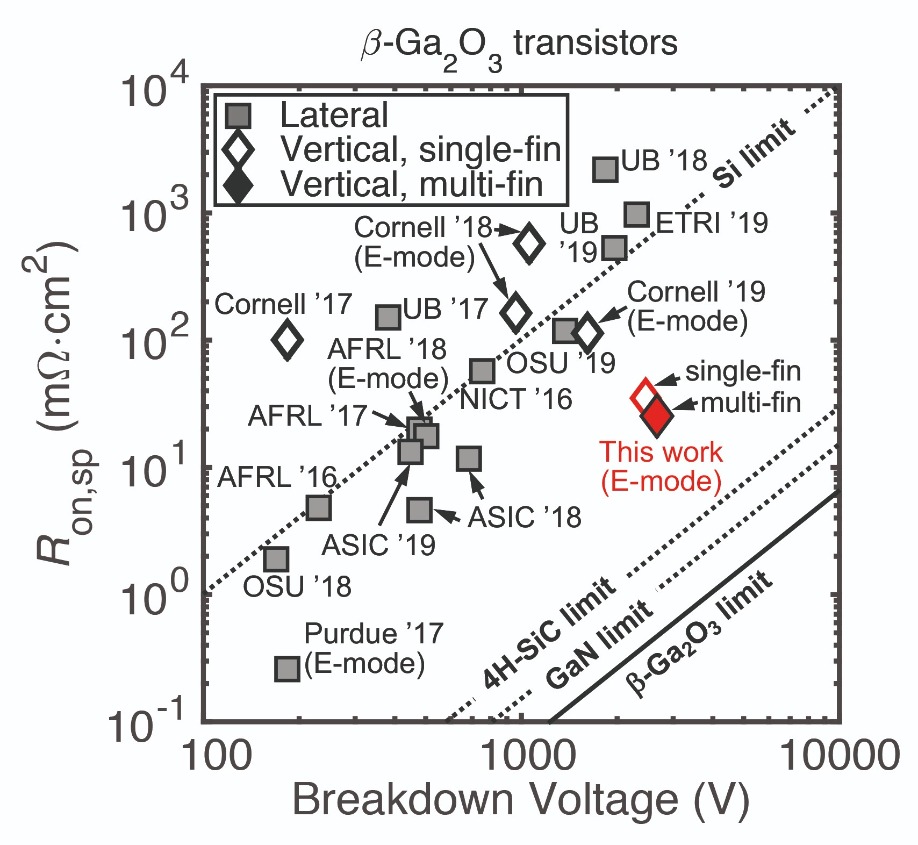

Helping to improve the performance of Ga2O3 transistors is a partnership between researchers at Cornell University and Hosei University. This team has broken the record for blocking voltage with a vertical transistor that can withstand 2.66 kV. This raises the bar from 2.32 kV, a figure obtained with a lateral variant.

Team spokesman Wenshen Li from Cornell University says that one of the merits of the vertical architecture, which leads to vertical current flow, is a more efficient use of the device footprint. “[Devices] typically have a smaller area, especially under high current ratings.”

By using a sub-micron fin-channel structure for the device architecture (see Figure 3), Li and co-workers avoid the need for p-doping. That’s a significant advantage as p-doping in Ga2O3 is impaired by: deep acceptor levels that hamper the thermal activation of these carriers; a very flat valence band, which leads to a high effective mass for holes and impairs conductivity; and self-trapping of holes.

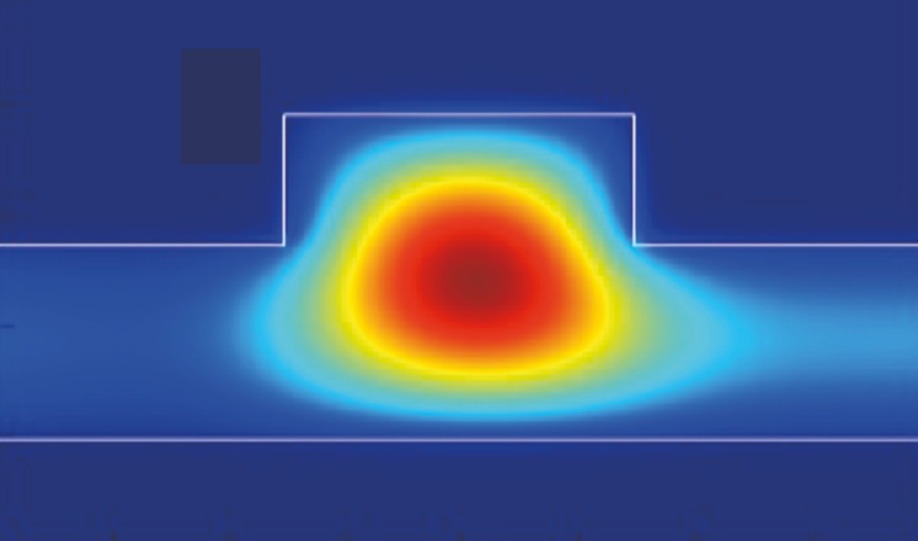

One of the reasons why Ga2O3 transistors are failing to fulfil their potential is that the channel mobility is far lower than it is in the bulk, due to etch damage and sidewall depletion. Effective channel mobility is typically just 30 cm2 V-1 s-1, compared to values of up to 200 cm2 V-1 s-1 for bulk material.

To address this, Li and co-workers use a post-deposition annealing step during the production of their transistors. Some of these devices contain several fins, enabling unambiguous evaluation of the specific on-resistance – it breaks new ground for Ga2O3 transistors.

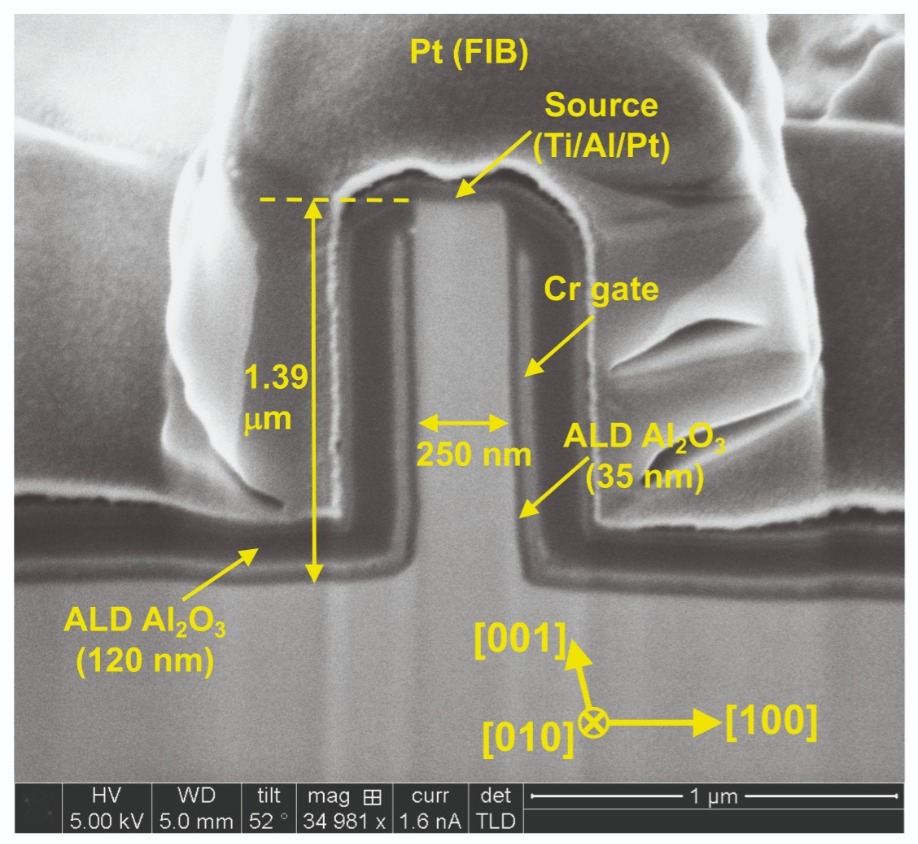

Fabrication of the team’s devices began by loading an n-type Ga2O3 substrate into a HVPE chamber and depositing a 10 µm-thick, lightly doped n-type drift layer. Silicon implantation and subsequent activation at 1000 °C created a heavily doped n-type top layer that provided an ohmic contact. Electron-beam lithography defined the fins (see Figure 4), which were formed by dry etching.

After treatment with HF to remove plasma damage, the team added a Ti/Au drain contact and a gate contact, comprising a 35 nm-thick Al2O3 gate dielectric created by atomic layer deposition and a 50 nm-thick layer of chromium, deposited by sputtering.

During the formation of the source electrode of Ti/Al/Pt by sputtering, Li and co-workers simultaneously created a source-connected field plate. This refinement to the design provided a significant improvement to edge termination, and is behind the increase in breakdown voltage.

“However, we found that the breakdown voltage is still limited by the edge termination, indicating that the source-connected field plate is not an optimal design,” admits Li.

The team have used electrical measurements to evaluate the benefit of post-deposition annealing. It leads to a significant increase in current density, an improved source contact resistance, and a reduction in interface trapped charges, leading to a lowering of the sidewall depletion in the fin channels.

Using simulations and fits to experimental data, channel mobility in single-fin devices is found to be around 130 cm2 V-1 s-1. This figure drops to just 40 cm2 V-1 s-1 in multi-fin devices, due to rougher sidewalls that result from plasma loading effects during the dry-etching step. “By tweaking the plasma condition during the dry etching for a more anisotropic etch, the roughness can be reduced,” say Li.

The multi-fin device outperforms its single-fin variant in blocking voltage, realising a value of 2.655 kV, compared with 2.46 kV. Additional measurements on the multi-fin transistor reveal an on-off ratio in excess of 108; a threshold voltage of 1.8 V at 0.1 mA cm-2; and a specific on-resistance of 23.2 mΩcm2, based on pulsed-measurements that are expected to reduce self-heating and charge trapping (see Figure 5 for benchmarking of the single-fin and multi-fin devices) .

Plans for further work include optimising the dry etching process, in order to improve channel mobility in multi-fin channel devices, and developing better edge termination designs for improved breakdown behaviour. Li says that additional goals are to undertake thermal characterisation of their devices, and the testing and analysis of dynamic behaviours.

The presentations at IEDM by Li on Ga2O3 transistors, and by other speakers on SiC devices, show that power electronic devices are getting better. That bodes well for the future, where greater deployment of more efficient power electronics is set to play its part in global efforts to tackle climate change.

Increasing the size of the waveguide on a photonic integrated circuit significantly reduces optical loss, boosts power handling and enables efficient coupling to the laser.

BY AARON ZILKIE AND GREG FINN FROM ROCKLEY PHOTONICS

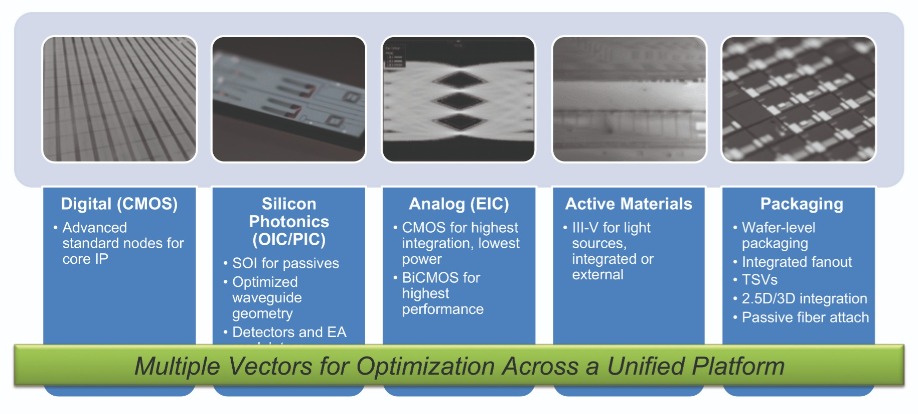

Silicon photonics holds the key to bringing photonic integrated circuits (PICs) to many more applications. PICs that sport silicon photonics promise to: increase the bandwidth and the power efficiency in data centres; provide low-cost, solid-state technologies for LiDAR operating at eye-safe wavelengths; deliver advanced computing solutions; and transform network communications, sensing and 3D imaging.

Today, the majority of silicon photonics players are focusing their efforts on developing monolithic products, which integrate photonics structures with CMOS on a single semiconductor chip. At first glance this is an attractive approach. However, if you delve more deeply drawbacks appear. One of the biggest of these is that due to physical and economic considerations, CMOS silicon photonics is not going to fulfil its full potential and scale. Why? While the scaling of CMOS technologies delivers benefits to the performance of electrical circuits, success is not replicated with photonics. Instead, multiple issues arise, because key photonics structures struggle at sub-micron dimensions. There is also another major issue – the materials available within a traditional CMOS semiconductor process cannot support the implementation of every electro-optic structure. Take, for example, the laser, which requires the processing of III-V materials.

The technology that we have developed at Rockley Photonics takes into account all these issues. Our approach is to begin with a clean sheet – a completely different process flow, unconstrained by the limitations of legacy CMOS processes that have been optimised for VLSI electronic devices.

From this starting point, we have been developing and optimising a proprietary photonics manufacturing technology since our foundation in 2013. We are able to draw on a depth of expertise that goes back some thirty years, and is aided by our close working relationship with our foundry partners. The platform that we are pioneering has great versatility, offers broad applicability across many product applications and markets, and enables high-volume production.

Simulation shows excellent confinement for single-mode light propagation in Rockley Photonics’ 3 µm-high waveguides. This single-mode propagation is maintained even if the waveguide is excited off-centre.

At the heart of our technology is the use of larger, multi-micron waveguides, which hold the key to optimising PIC performance, power efficiency, manufacturability and versatility. Compared to a conventional architecture, our platform has: up to ten times lower waveguide loss; a 25-fold reduction in performance variability, due to changes in waveguide dimensions; polarization independence; and a low-loss, monolithic, ultra-broadband fibre attach technology.

By reducing propagation loss, our multi-micron waveguides enable PICs to serve the widest possible range of applications. We tackle the leading contributor to propagation losses, electromagnetic field scattering, which is caused by roughness in the sidewalls of the waveguide. Reducing this roughness is far from easy – a simpler approach is to minimise the transmitted light’s modal overlap with the side walls. This is what we do with our multi-micron waveguides, to make them outperform their conventional sub-micron equivalents. Our waveguides combine improved confinement with a reduction in modal overlap with waveguide side walls – factors that also enable high integration capabilities.

In many applications, it is important for a PIC to have a high power-handling capacity. For example, with LiDAR, high output powers enable the generation of images at extended ranges and high frame rates – leading to the delivery of more photons on target down range. With silicon photonic chips, power-handling capacity is limited by a saturation effect associated with the simultaneous absorption of two photons. This absorption loss is governed by the spatial intensity of the light in the waveguide, so is substantially different in sub-micron and multi-micron waveguides. In 3 µm waveguides, power can be 30 times higher than it is in 220 nm waveguides before there is a 1 dB power loss due to two-photon absorption.

Another valuable attribute for 3 µm waveguides is that they support single-mode operation, which minimises dispersion and signal degradation. It may come as a surprise to some that our multi-micron waveguides are capable of this – and they do so while offering several advantages over a conventional sub-micron variant, including simultaneous realisation of low-loss coupling to standard single-mode fibre and III-V active devices, very low propagation losses, high tolerance to fabrication variations and polarization independence. The latter is realised by setting the waveguide rib width-to-height ratio close to unity, and ensuring that the transverse electric and transverse magnetic modes have similar values for the effective index. We produce PICs that have all these attributes and a range of waveguide sizes with cross-sectional dimensions from 1 µm to 13 µm.

An additional merit of multi-micron waveguides is that they can realise tight bends. This is highly valued – designers want to produce high-density photonic circuits, so they are keen to avoid large bends that hinder compact PIC designs, waste valuable silicon space and result in larger chip and package sizes. Our multi-micron waveguides are ideal, as they can have tight bends while avoiding losses and mode leakage, because they provide strong confinement of the electromagnetic wave. To do this, we convert the rib waveguides into strip or wire waveguides in the parts of the circuit where tight bends are needed, and employ a special design known as an Euler bend in the high-confining strip waveguide.

Bends in Rockley’s 3 µm waveguides.

We have shown through simulation and measurement that our multi-micron waveguides produce a far lower phase error and wavelength variation than sub-micron counterparts. For a 3 µm waveguide, the variation in effective refractive index is 20 to 40 times lower than it is in 220 nm waveguides.

Rockley Photonics manufacturing flow.

In addition to developing multi-micron waveguides, we have created a portfolio of key building blocks. They include lasers, modulators, photodetectors and filters, all of which utilise the attributes of the platform.

To add a laser to our PIC, we have to integrate a III-V semiconductor device, because silicon is a poor light emitter. This addition is relatively easy for us, because laser diodes naturally also have a multi-micron mode size.

We attach the fully processed lasers directly, in a recess that we etch into the silicon waveguide. This facilitates edge coupling, which enables low-loss and dense laser integration to produce PICs with a compact form factor, while still realising high manufacturing tolerances. This approach is also highly versatile, enabling us to integrate a wide range of lasers – different materials and designs – using a flip-chip die bonding approach.

The lasers that we add have excellent characteristics. They have very narrow linewidths and output powers that can exceed 50 mW at room temperature. Those with a hybrid distributed feedback design are tolerant to back-reflections, having up to -20 dB return loss at the laser facet. This is a very valuable attribute, as commercial lasers used in silicon photonics have to operate in the presence of multiple sources of scattering and back reflection.

Our platform is also ideal for ultra-broadband applications. It can produce many-channel laser PICs, built by harnessing multi-cavity and multi-material wafer-scale integration techniques.

We have also developed processes for adding electro-absorption modulators and photodetectors to our chips. These devices are critical components in products across multiple markets including optical fibre and datacentre communication transceivers.

A well-diversified toolbox enables platform versatility.

Germanium photodetectors, which convert light signals back to electric signals, are also made in this platform with excellent performance. These polarization-independent, broadband devices have electro-optic detection bandwidths of over 40 GHz, sufficient for detection of 50 Gbit/s NRZ and 100 Gbit/s PAM-4 signals.

Filters are an essential ingredient in PICs, performing functions that include wavelength-division multiplexing, a technology that enables high-bandwidth data transfer. The most common way to realise this is to use arrayed waveguide gratings. This form of filter is far better with multi-micron waveguides than sub-micron variants, because the larger dimensions lead to a lower birefringence, polarization independence, and a reduction in phase errors and propagation losses. Thanks to these attributes, arrayed waveguide gratings, produced in our platform, provide high performance and repeatability. By incorporating Euler bends into these arrayed waveguide gratings, they are far more compact, opening the door to their integration into high-density PICs.

One of the downsides of forming PICs with silicon is that this material has a high thermo-optic coefficient, which hampers heat management. To address this, we deploy heaters that deliver around a 1 mW/p phase change – they can be positioned within waveguides to manage thermal energy. In addition, with just a few additional processing steps, our arrayed waveguide gratings made with only silicon can be made temperature independent. These gratings produce almost no drift in wavelength due to temperature variation.

For many applications, optical signals need to be transferred from the chip to the fibre. This requires an interface between PIC waveguides and single-mode optical fibre. If the PICs are to be competitive in high-volume products, this attachment should be low-cost, low-loss and simple to align.

We tick all those boxes, thanks to the use of a mode size that is in the same ballpark as that of single-mode fibre. A single-stage spot size converter enables us to mode-match between 3 µm waveguides and 13 µm waveguides, and then directly couple to single-mode fibre. Etching V-grooves into the silicon allows us to accurately align the single-mode fibre to 13 µm waveguides and also hold the fibre in place, creating the most simple and elegant fibre attach solution for photonic integrated circuits.

Rockley’s platform serves multiple sectors from communications to sensing

The strengths of our platform are not limited to its performance, but extend to its suitability for broad applicability, high-volume manufacturing and large-scale deployment. These advantages are partly due to a production process that realises high yields, thanks to low device sensitivity to process variations. However, there are additional merits of our technology. It is capable of integrating a large number of components at a high density; it produces low optical loss interfaces; and III-V materials are integrated in an efficient manner. What’s more, data throughput densities can exceed 200 Gbit/s/mm, due to our high-speed, compact, low-power modulator and detector technologies and interface electronics; and fibre coupling losses can be less than 1 dB with our simple, high-yield, high-throughput fibre attach assembly.

Using a complex manufacturing flow that involves many partners, we have also developed and implemented analogue, digital and mixed-signal electronics design and integration. This has enabled us to ship complete photonic chips and chipsets to serve different market sectors.

Ideally, silicon photonic chips form part of a set of wider technologies, together with CMOS, BiCMOS and packaging. We are able to incorporate all of these in a complete chipset, making our multi-micron silicon PIC platform a strong candidate in many markets.

One of these markets is data communications, where there is a rising global appetite for data-centre bandwidth. This is driving demand for in-package optics which involves integrating fibre-optic links with ICs. To enable edge integration, these ICs require high-bandwidth, compact PICs operating at more than 200 Gb/s/mm, a specification we can satisfy.

In addition, there is a need to keep pace with increasing bandwidth capabilities of switch ASICs, by scaling PIC modulators and detectors to higher data rates, while increasing their integration density. Our modulators and detectors are ideal for this task. Using our platform, transceiver PICs are smaller than 30 mm2 – that is comparable to, or smaller than, those made using sub-micron photonic platforms.

With an optical power handling capability of over 2 W, our multi-micron platform is also well suited to sensing applications, such as 3D imaging and LiDAR. These applications can involve the transmission of large optical powers, and require fast, steerable, narrow beams for high resolutions at high frame rates. One strength of our platform is its demonstrated capability to implement coherent receivers, an essential ingredient for frequency-modulated continuous wave LiDAR. This advanced form of LiDAR collects 3D imaging and velocity measurements – data that is much sought after by those developing advanced driver-assistance systems and related autonomous technologies for the automotive and transport markets.