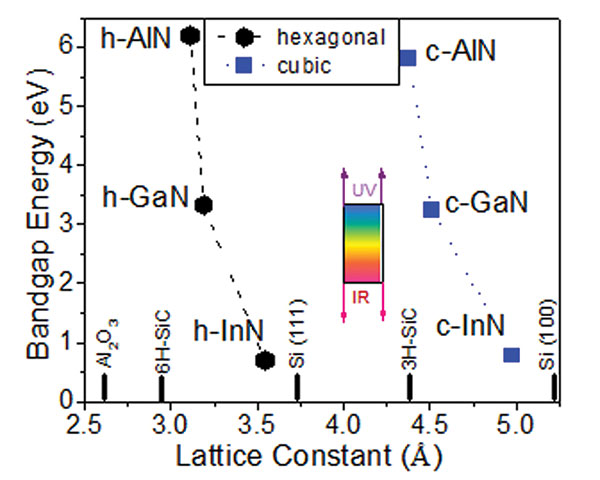

Today the LEDs emitting in the blue and green are made from the nitrides, while arsenides enable the construction of the orange, yellow and red emitting cousins.

Trimming the number of material systems from these two to just one would be better on multiple fronts. It would simplify packaging; it would allow driving systems to be optimised for specific electrical and material characteristics; and it would open the door to the production of full-colour LED displays and white-lighting systems based on a single chip.

When exploring this route, there is no question which material system should be used: it has to be the nitrides, because the arsenides can’t stretch to shorter wavelengths, due to a switch to an indirect bandgap. Ditching arsenide devices would also lead to other benefits, because their efficiency plummets at higher temperatures, and their wavelength shift with current exceeds that for nitrides.

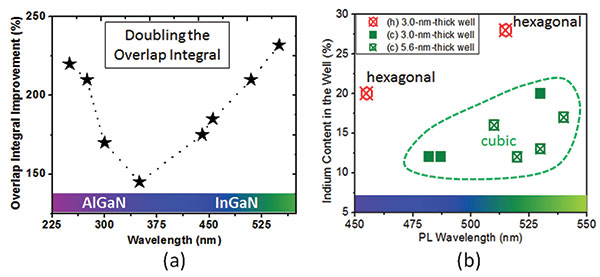

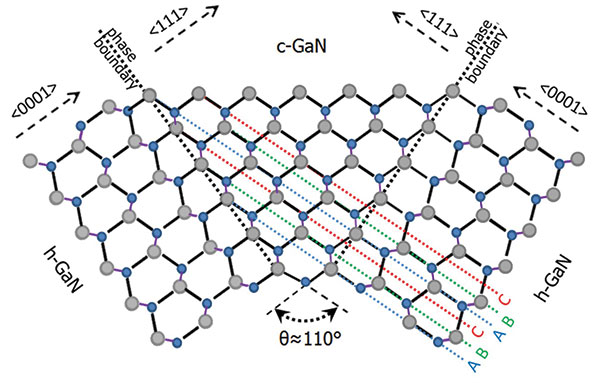

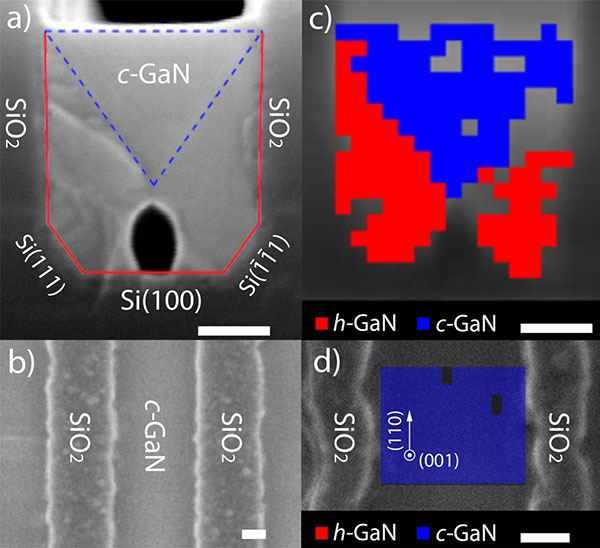

Efforts to extend nitride LEDs from the green to yellow, orange and red are already well underway. Success is not easy, however, as quantum wells must be rich in indium to reach these wavelengths – and that impairs material quality, and ultimately efficiency. Making matters worse, internal electric fields increase in strength at longer wavelengths, pulling electrons and holes further apart and hampering radiative recombination.

One way to improve performance is to reduce the strain in these devices. For example, when a team from Ostendo Technologies inserted a compliance layer beneath the active region, they produced the world’s first GaN LED delivering tuneable, full-colour emission. This chip features intermediate carrier-blocking layers to control electron and hole transport between the quantum wells emitting in the red, green and blue (see p. 44).

Ostendo is now developing its technology for the display market. The promise of replacing backlit screens with those based on LED pixels is very attractive, as it could lead to simpler, more robust displays with greater efficiency.

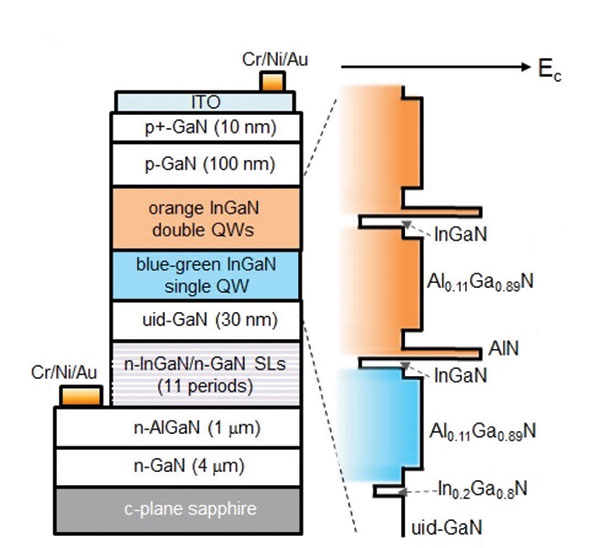

Researchers in Japan are also developing long-wavelength nitride LEDs. A partnership between scientists at Tokyo University of Science and Meijo University has developed a hybrid LED featuring an orange-emitting quantum well stacked on a blue one. The latter does not actually emit, instead serving as a strain releasing layer (see p. 58).

For both teams, emission efficiency must increase at longer wavelengths. That’s not surprising, given that this technology is in its infancy. But hopefully great advances will be made, leading to widespread commercial adoption of full-colour GaN LEDs.

Macom, a US company that makes RF, microwave and photonic semiconductors, has been granted a preliminary injunction in its lawsuit against Infineon Technologies Americas Corp over GaN-on-silicon technology rights.

The US District Court for the Central District of California in Los Angeles' decision confirmed Macom's continuing exclusive rights in certain GaN-on-silicon RF fields under a 2010 License Agreement entered into between Nitronex (acquired by Macom in 2014) and International Rectifier (acquired by Infineon in 2015); and it ruled that Macom is likely to succeed on its claim that Infineon's purported termination of that Agreement was improper and without effect.

It granted Macom's motion for a preliminary injunction prohibiting Infineon from engaging in activities inconsistent with the 2010 License Agreement pending the Court's final decision in the case.

"We were forced to file this lawsuit to stand up to Infineon's bullying and anticompetitive behaviour. We are gratified by the Court's preliminary decision confirming that the GaN-on-silicon rights granted to us under the 2010 License Agreement remain in full force and effect and that Infineon acted improperly in trying to operate in our exclusive field of use," said John Croteau, president and CEO of Macom.

"We are firmly committed to vigorously litigating this case to its rightful conclusion. We continue on the path to providing GaN-on-silicon technology that promises to improve network data service and cell coverage of 4G/LTE and 5G base stations that will benefit people worldwide."

The latest phase of Cardiff University's £300m Innovation Campus, which includes The Institute for Compound Semiconductors - a unique UK-based translational research centre in compound semiconductors - and Cardiff Catalysis Institute for chemical research - has been approved by city planners. Cardiff University hopes to start work on site early in 2017.

The fully-funded £135m project on the city's brownfield Maindy Park is the latest phase in Cardiff's mission to embed innovation into University life. Two new buildings will bring researchers, businesses, public sector backers and students together. Architecture practices Hawkins\Brown and HOK each designed a building for the project, working alongside site master planners BDP and town planning consultancy DPP. The campus vision, outlined two years ago by vice-chancellor Colin Riordan, establishes centres of excellence that push benefits back into the economy to create a self-sustaining cycle for growth. Riordan said: "A new campus helps us create opportunities for all. Cutting-edge research, technology transfer, business development and student enterprise will put ideas to work.

"Our innovation ambitions go beyond the sum of the physical buildings. We are hiring internationally-renowned academics who can build world-class teams of post-doctoral researchers. We are equipping students with the skills they'll need to set up future ventures. And we're continuing to attract major UK and international funding across private and public sectors to make Cardiff the home of innovation."

In addition to two new buildings, each covering 12,000 sq m, this latest third phase includes a bridge linking Cardiff Business School with the Innovation Campus.

Adrian Gainer, regional leader for HOK's Science + Technology group, added: "We look forward to creating cutting-edge facilities that will reinforce the university's international reputation as a leading catalysis research centre and build on its strengths in the development of semiconductor devices and materials. "Both the Institute for Compound Semiconductors and the Cardiff Catalysis Institute have been designed to enable multidisciplinary research to flourish, with inspiring spaces to attract and retain the most talented individuals."

Martin Jones, BDP, said: "The Campus fulfils a number of aspirations for Cardiff University and aims to facilitate world-leading scientific research, inter-disciplinary mixing and increase student opportunities in an environment that's better for business."

Gareth Hooper, DPP, added: "We worked very closely with the University and Cardiff Council to ensure that this exciting scheme could be delivered within an outline planning consent dating back to 2010. The result is the continuation of an exciting regeneration project, delivering physical change to the city through world-leading science."

Researchers at the Fraunhofer Institute for Solar Energy Systems ISE together with the Austrian company EV Group (EVG) have successfully manufactured a silicon-based multi-junction solar cell with two contacts and an efficiency of 30.2 percent, exceeding the theoretical limit of silicon solar cells.

For this achievement, the researchers used a 'direct wafer bonding' process to transfer a few micrometres of III-V semiconductor material to silicon, a well-known process in the microelectronics industry. After plasma activation, the subcell surfaces are bonded together in vacuum by applying pressure. The atoms on the surface of the III-V subcell form bonds with the silicon atoms, creating a monolithic device.

The efficiency achieved by the researchers presents a first-time result for this type of fully integrated silicon-based multi-junction solar cell. The complexity of its inner structure is not evident from its outer appearance: the cell has a simple front and rear contact just as a conventional silicon solar cell and therefore can be integrated into photovoltaic modules in the same manner.

"We are working on methods to surpass the theoretical limits of silicon solar cells," says Frank Dimroth, department head at Fraunhofer ISE. '"It is our long-standing experience with silicon and III-V technologies that has enabled us to reach this milestone today." A conversion efficiency of 30.2 percent for the III-V / Si multi-junction solar cell of 4 cm2 was measured at Fraunhofer ISE's calibration laboratory. In comparison, the highest efficiency measured to date for a pure silicon solar cell is 26.3 percent, and the theoretical efficiency limit is 29.4 percent.

The III-V / Si multi-junction solar cell consists of a sequence of subcells stacked on top of each other. So-called 'tunnel diodes' internally connect the three subcells made of GaInP, GaAs and silicon (Si), which span the absorption range of the sun's spectrum. The GaInP top cell absorbs radiation between 300 and 670 nm. The middle GaAs subcell absorbs radiation between 500 and 890 nm and the bottom Si subcell between 650 and 1180 nm, respectively. The III-V layers are first epitaxially deposited on a GaAs substrate and then bonded to a silicon solar cell structure. Subsequently the GaAs substrate is removed, and a front and rear contact as well as an antireflection coating are applied. "Key to the success was to find a manufacturing process for silicon solar cells that produces a smooth and highly doped surface which is suitable for wafer bonding as well as accounts for the different needs of silicon and the applied III-V semiconductors," explains Jan Benick, team leader at Fraunhofer ISE. "In developing the process, we relied on our decades of research experience in the development of highest efficiency silicon solar cells."

Institute director Eicke Weber said: "I am pleased that Fraunhofer ISE has so convincingly succeeded in breaking through the glass ceiling of 30 percent efficiency with its fully integrated silicon-based solar cell with two contacts. With this achievement, we have opened the door for further efficiency improvements for cells based on the long-proven silicon material."

"The III-V / Si multi-junction solar cell is an impressive demonstration of the possibilities of our ComBond cluster for resistance-free bonding of different semiconductors without the use of adhesives,' says Markus Wimplinger, corporate technology development and IP director at EV Group.

"Since 2012, we have been working closely with Fraunhofer ISE on this development and today are proud of our team's excellent achievements." The direct wafer-bonding process is already used in the microelectronics industry to manufacture computer chips.

On the way to the industrial manufacturing of III-V / Si multi-junction solar cells, the costs of the III-V epitaxy and the connecting technology with silicon must be reduced. There are still great challenges to overcome in this area, which the Fraunhofer ISE researchers intend to solve through future investigations. Fraunhofer ISE's new Centre for High Efficiency Solar Cells, presently being constructed in Freiburg, will provide them with the perfect setting for developing next-generation III-V and silicon solar cell technologies. The ultimate objective is to make high efficiency solar PV modules with efficiencies of over 30 percent possible in the future.

The young researcher Romain Cariou carried out research on this project at Fraunhofer ISE with the support of a Marie Curie Postdoctoral Fellowship. Funding was provided by the EU project HISTORIC. The work at EVG was supported by the Austrian Ministry for Technology.

The German Ministry of Economics has withdrawn its clearance certificate for the takeover the German semiconductor deposition firm Aixtron by Grand Chip Investment GmbH, a 100 percent indirect subsidiary of Fujian Grand Chip Investment Fund LP.

Fujian Grand Chip Investment Fund is a Chinese investment fund; 51 percent of which is held by the Chinese businessman Zhendong Liu and 49 percent by Xiamen Bohao Investment Ltd.

Back in May, the companies entered into a €670 million takeover agreement under which Aixtron shareholders would be offered €6.00 in cash per each ordinary share.

Aixtron has not given a reason for the reversal of the decision, but commentators in the press have highlighted growing concerns in Germany about the acquisition of cutting-edge technologies by Chinese firms and subsequent loss of knowhow and high-tech jobs.

Researchers at Dartmouth College, New Hampshire, working on a project called ‘DarkLight’ have developed and demonstrated for the first-time, how visible light from LED lighting can be used to transmit data even when the light appears dark or off.

The study, ‘The DarkLight Rises: Visible Light Communication in the Dark’ will be presented in New York at MobiCom 2016: The 22nd Annual International Conference on Mobile Computing and Networking on October 4th by Dartmouth co-author Zhao Tian, the lead PhD student for the project.

Through DarkLight, light-based communication is sustained even when LEDs emit extremely low luminance, by encoding data into ultra-short, imperceptible light pulses by using off-the-shelf, low-cost LEDs ($7 each) and photodiodes ($6-8 each).

The current DarkLight prototype supports 1.6kbps data rate at 1.8m distance.

"With DarkLight, we can potentially enable light sensing so that it is always on, 24/7, regardless of the light's illumination status," says the project's principal investigator Xia Zhou, assistant professor of computer science and co-director of the DartNets (Dartmouth Networking and Ubiquitous Systems Lab), which helped conduct the study. DartNets' research focuses on broad applications, systems, and networking perspectives of smartphones and smart device systems.

"DarkLight shows new possibilities on what visible light alone can do. We believe there are a lot more interesting applications yet to come," added Zhou.

US RF company Qorvo has announced financial results for Q2 2017, ended October 1, 2016. On a GAAP basis, Q2 2017 revenue increased 22.1 percent year-over-year and 23.8 percent sequentially to $864.7 million. Gross margin was 36.6 percent, operating income was $45.4 million, and net income was $11.8 million, or diluted EPS of $0.09.

On a non-GAAP basis, gross margin was 42.8 percent, operating expenses were $172.9 million, operating income was $196.8 million, or 22.8 percent of sales, and net income was $170.4 million, or diluted EPS of $1.29.

Gross margin decreased sequentially on both a GAAP and non-GAAP basis, due primarily to lower than expected manufacturing yields during a steep product ramp to a large customer.

Bob Bruggeworth, president and chief executive officer of Qorvo, said: "The Qorvo team did an excellent job delivering 22 percent year-over-year growth and achieving our goal of non-GAAP operating expenses at 20 percent of sales. At the same time, we made progress advancing core technologies and developing highly integrated Qorvo solutions for large customer opportunities in 2017 and 2018.

"It's clear we have work to do on gross margin, and we've taken steps to address it. We continue to drive toward our operating model, including above-market revenue growth and non-GAAP operating income above 30 percent. "Separately, we are pleased to announce that Qorvo's board of directors this week has authorized a $500 million share repurchase program."

Qorvo currently believes the demand environment in its end markets supports the following non-GAAP expectations for the December 2016 quarter: quarterly revenue in the range of $800 million to $840 million; sequential gross margin expansion of 100 to 200 bps; tax rate of approximately 8 percent; and diluted EPS in the range of $1.15 to $1.35.

Philips Photonics, a wholly owned business of Royal Philips, has announced that it is doubling capacity at its laser-diode facility in Ulm to provide the key components for some of the latest developments in data communication, consumer sensing and industrial thermal processing.

VCSEL diodes are key components in a growing number of consumer and industrial applications, including: sensing of 3D objects in autonomous vehicles; PC 'mice'; industrial sensors and control functions; driver assist systems; ultra-fast data transmission in data centres and servers; and providing distance and gesture recognition in mobile phones.

"Over the past few years, we have invested steadily in research, product development and efficient manufacturing processes. Today, our products are widely used in datacentres, smartphones and a number of industrial applications. The sharp rise in demand for VCSELs is a key factor in our capacity expansion at Ulm, and will enable us to respond to the needs of these rapidly growing markets," said Joseph Pankert, general manager, Philips Photonics. Semiconductor lasers have been developed and manufactured at the Philips Photonics facility in Ulm since 2000. The company has pioneered many innovations such as VCSEL arrays, now widely used for time-of-flight and 3D depth imaging. Since its establishment, the facility has grown significantly, with staff numbers increasing from 50 in 2012 to 200 in 2016.

In 2014, the company made significant step to highly automated manufacturing, within the framework of the 'VIDAP' project, jointly sponsored by the German Federal Ministry of Education and Research (BMBF) and the EU.

In its 'Power GaN 2016: Epitaxy and Devices, Applications, and Technology Trends' report, Market research firm Yole Développement predicts that the GaN power business will reach $280 million in 2021, growing at 86 percent CAGR between 2015 and 2021.

It says the market is being driven by emerging applications including power supplies for datacentre and telecom, AC fast chargers, Lidar, envelope tracking, and wireless power.

"Numerous powerful developments and key collaborations have been announced during this period and confirmed a promising and fast-growing industry", comments Hong Lin from Yole. Collaborations include Integrated Device Technology (IDT) and Efficient Power Conversion (EPC); Infineon Technologies and Panasonic; Exagan and XFab; TSMC and GaN Systems for volume production, which all took place within the last two years.

Up until late 2014, 600V/650V GaN HEMTs' commercial availability was still questionable, despite announcements from various players. Fast-forward to 2016 (see above) and end users can buy low-voltage GaN (<200V) devices from EPC and high-voltage (600V/650V) components from several players, including Transphorm, GaN Systems, and Panasonic.

The idea of bringing GaN from the power semiconductor market to the much bigger analogue IC market is also now gaining interest, says Yole. For example, EPC Power and GaN Systems are both working on more integrated solutions.

Australian green technology company BluGlass has received a significant order commitment from a new UK customer for its specialist epitaxy development. Worth around $600,000, the order is scheduled to be delivered over the next 12 months.

The UK based customer is developing GaN technology targeting LED and other applications. BluGlass recently fulfilled a small order for this customer. This new larger order commitment will be used for a new innovative project.

BluGlass' Remote Plasma Chemical Vapour Deposition (RPCVD) process is designed to grow semiconductor materials such as GaN and InGaN with advanced performance and low cost potential.

The RPCVD technology, because of its low temperature and highly flexible nature, offers many potential benefits over existing technologies including higher efficiency, lower cost, substrate flexibility including GaN on silicon and greater scalability.

BluGlass managing director Giles Bourne said: "This single order from a new customer is the largest foundry order that the company has received to date. The BluGlass foundry business continues to attract select customers and we are excited to be working with the innovators that will be leading the nitrides industry into the future".

Advertisement: Masimo Semiconductor

LED company Cree has filed a complaint against E. Mishan & Sons, Inc. (Emson) with the US District Court for the District of Massachusetts for infringement of Cree's patented LED technology in Emson's flashlights, such as the Bell + Howell Taclight.

"Cree will not tolerate and will aggressively defend against such blatant disregard of its intellectual property rights," said Dave Emerson, senior vice president and general manager for Cree LEDs.

"We have an obligation to our customers to ensure that the market offers products that include the high-quality LED components that customers have come to expect. We are committed to protecting Cree's investment in research and development on behalf of our customers, shareholders and our licensing partners."

As part of the complaint, Cree is seeking an award of enhanced damages, attorneys' fees and an injunction to prevent Emson from offering for sale and selling any products using knock-off LEDs.

LayTec has delivered its 2000th in-situ metrology system since its foundation in 1999. An EpiTT with 2000 in its serial number has been shipped to Compound Semiconductor Centre (CSC) - a joint venture between compound semiconductor specialists IQE and Cardiff University.

CSC works on providing a complete capability value chain from high-end R&D through product and process innovation to high value, large-scale manufacturing. According to Wyn Meredith, director of CSC: "This EpiTT and other LayTec systems already installed in our labs provide unrivalled precision and sophisticated analysis algorithms, which is crucial for process optimisation in semiconductor manufacturing environment."

EpiTT - LayTec's workhorse for MOCVD mass production - combines measurements of temperature and reflectance at three wavelengths in one tool. For True Temperature (TT), it usesEmissivity Corrected Pyrometry, which delivers the precise surface temperatures of opaque materials at 950 nm (Si, GaAs, InP). For materials that are transparent at 950 nm (GaN, Sapphire, SiC), EpiTT measures the temperature on the top side of the carrier. Measuring reflectance at three wavelengths monitors all essential properties of the growing layers, such as growth rate, film thickness, stoichiometry changes and morphology.

LayTec's founder and CEO Thomas Zettler commented: "It is significant that our 2000th in-situ tool is delivered to a research institution with a strong connection to industry. LayTec has always set a great value on cooperating with both industry and R&D."

He added: “Until now, we have equipped hundreds of customers worldwide with state-of-the-art metrology, mainly in the field of LED and laser production. In the last few years we also entered the PV, display and advanced silicon markets. Meanwhile, our product portfolio covers all areas of process monitoring: in-situ, in-line, lab-line and map-line metrology. Due to this market diversification, we believe to deliver the next thousand tools much faster than before."

Thermal management specialist Cambridge Nanotherm has announced it has built significant additional capability and capacity into its MCPCB manufacturing base to meet rising demand for its award-winning thermal management solutions. The company has established partnerships with a wide network of PCB and thin-film manufacturers to offer a broad range of options in terms of circuitisation, quality, volume and standards.

Cambridge Nanotherm’s manufacturing capabilities include everything from fast turnaround prototyping, high-definition thin-film circuitisation, speciality manufacturing, through to high-volume mass production. Key industry and regulatory standards such as automotive standard ISO/TS 16949:2009, as well as industry-specific SGS standards, can be applied.

From LED chip packaging to high-brightness modules, thermal management is becoming a limiting factor as customer’s demand ever brighter LED devices in ever smaller footprints. To meet these requirements LED manufactures are being pushed into using more thermally effective substrates to ensure that LEDs stay cool enough to meet their advertised lifespan. Historically that meant switching from cost effective MCPCBs to expensive and difficult-to-work-with ceramics such as alumina and aluminium nitride. Cambridge Nanotherm offers an alternative.

Sitting at the heart of high-power LED applications, Nanotherm LC and Nanotherm DM technologies are enabling a new generation of products that rely on effective thermal management to operate successfully. Cambridge Nanotherm’s proprietary LC and DM technologies are available exclusively via this manufacturing process.

Andy Matthews, COO at Cambridge Nanotherm, said: “Our MCPCBs offer designers a distinct thermal advantage. Demand for our solutions has therefore been strong, and we’re currently engaged with most of the top ten LED manufacturers. As a result, we’ve expanded our manufacturing routes to cater to a much broader variety of requirements. We’re working with some of the best PCB and thin-film circuitisation companies so we can offer an exceptional range of options to ensure we keep our customers satisfied. We will continue to develop our manufacturing capabilities to make sure we always offer the best available options to our customers.”

Nanotherm’s patented ECO process involves converting the surface of the aluminium core of the MCPCB, which acts as a heat spreader, into an electrically insulating but thermally conductive nanoceramic that offers outstanding thermal performance. Depending on the circuitisation route that is chosen, composite thermal performance of the resulting Nanotherm MCPCB ranges from 115 W/mK to 152 W/mK.

Standard LC products are covered by UL recognition, speeding up time to market for luminaires and modules. Nanotherm manages the entire process, from thermal design guidance and material choice to delivering the finished circuits. This makes the process seamless and simplifies the manufacturing route for customers.

Osram Opto Semiconductors is using converter technology for infrared emitters for the first time. The result is the SFH 4735 - an LED that emits broadband infrared light in a wavelength range from 650 to 1050nm. The main application is near-infrared spectroscopy, for example for analysing food.

Infrared spectroscopy uses the characteristic absorption behaviour of certain molecular compounds. If a defined spectrum is directed at a sample it is possible to determine the presence and quantity of certain ingredients from the wavelength distribution of the reflected light. This method is used in the food industry and in agriculture, among other sectors. It is possible, for example, to measure the water, fat, carbohydrate, sugar or protein content of foodstuffs. This data provides an indication of freshness, quality or calorie content.

Osram believes that this new infrared LED opens this measurement technique up to consumers. One option would be a compact sensor - like a USB stick - which would be used with an appropriate smartphone app to measure calories, freshness or nutritional content.

The basis of the SFH 4735 is a blue 1 mm2 chip in UX:3 technology. Its light is converted into infrared radiation with the aid of a phosphor converter developed specifically for this application.

A residual blue component in the light helps users target the area they want to investigate. The emission spectrum of the SFH 4735 has a homogeneous spectral distribution in the infrared range.

The chip is mounted in the Oslon Black Flat package which is characterised in particular by good thermal resistance.

Compact units for spectroscopic chemical analyses open up a completely new range of applications in consumer electronics. Experts expect that it will be possible in the near future to integrate spectrometers directly in mobile devices. The new technology is a natural extension of bio monitoring, in other words the trend for measuring various vital signs such as pulse rate and calorie consumption.

A smartphone spectrometer will enable users to monitor the food they eat in a similar manner. Medicines can also be checked in the same way.

"Future applications are also of particular interest", said Udo Jansen, product marketing manager for infrared at Osram Opto Semiconductors. "It is conceivable that the emission range can be extended to include wavelengths up to 2,000 nanometres, in other words into the middle infrared spectral range. This will allow more precise and detailed measurements and will open up new options for everyday analyses of certain environmental parameters such as air quality."

Rubicon Technology, a provider of optical and industrial sapphire products, has reported financial results for its Q3 ended September 30, 2016.

The company reported Q3 revenue of $7.1 million, $3.6 million higher than the prior quarter revenue. Revenue from wafer sales in the Q3 was $5.5 million as compared with $1.8 million in the prior quarter. The higher wafer revenue was the result of increased orders from a key patterned wafer customer along with that customer drawing down all wafers in consignment inventory.

The company's Q3 loss per share was $0.94 as compared with a loss per share of $0.31 in the prior quarter.

The company's Q3 results were impacted by the decision made in September this year to cease all production activities and shut down its Penang, Malaysia facility. The facility has been primarily engaged in producing polished and patterned substrates for the LED market and the decision was made in order for the company to focus on the optical and industrial sapphire market for the foreseeable future.

Production activities at the Penang facility are expected to cease by November 30, 2016, with the shutdown of the facility to be completed by the end of the year. Bill Weissman, the company's CEO, said: "While margin pressure in the LED and mobile device segments of the sapphire market continue to be severe, there remains good margin opportunity in the optical and industrial segments. We believe that the actions we are taking will improve our operating results, strengthen our cash position and allow us to grow in strategic markets that are better aligned with our strengths while offering stronger margin potential. Once the changes are fully implemented, our revenue will be smaller for a period of time, but the optical and industrial sapphire markets are growing with potential new applications for sapphire emerging.

“Once our Malaysia facility ceases production activities, our wafer revenue will significantly decrease beginning in the fourth quarter of 2016 and into future periods.”

One-time charges in the quarter related to the decision to exit the LED market and close the Malaysia facility included; a $10.2 million asset impairment for writing the Malaysia assets down to liquidation value, a write-down of $4.0 million in excess raw material inventory, and $900 thousand in accrued severance. In addition, the company recorded a write-down of $2.3 million of excess two-inch core inventory, which is sold primarily into the mobile device market, and severance of $180 thousand for reduction of staffing in the US.

Dialog’s delivery of GaN power ICs signals mainstream market adoption is close, reports Rebecca Pool.

LATE THIS SUMMER, UK-based Dialog Semiconductor revealed plans to sample GaN power ICs in a fast charging power adapter by the end of this financial year.

Following two years of collaboration with Taiwan Semiconductor Manufacturing Corporation, the power management IC supplier has developed a 650 V GaN power IC plus controller combination that is said to halve the size and power losses of silicon power management ICs.

“Until recently, GaN had been largely limited to small specialty fabs from vendors in Japan as well as research institutions,” says Mark Tyndall, Senior Vice President of Corporate Development and Strategy at Dialog. “In contrast, Dialog targets high volume consumer applications, so it’s never been our intention to prove GaN for, say, niche military applications.”

“But when TSMC started to offer GaN as a standard process on six inch wafers, we saw that as a signal that this was the right time to enter this market, as well as solve the emerging problems of size in the power adapter market,” he adds.

Dialog’s end-result is the so-called SmartGaN DA8801; a monolithic IC that integrates enhanced-mode GaN-on-silicon HEMTs with analogue drivers and logic blocks in a 650 V half-bridge design for 25 W to 65 W adapters. By combining this IC with its ‘Rapid Charge’ power conversion controllers, Dialog can produce efficient, small, high-power-density adapters that look set to topple traditional silicon FET-based designs from pole position in the world of power adapters.

“We’re not trying to replace a silicon FET with a pure GaN transistor; how could a six inch [GaN-on-silicon] wafer process compete with [CMOS] manufacturer producing millions and millions of wafers?” points out Tyndall. “But we have optimised our solution around this GaN, half-bridge architecture which allows us to provide a GaN-based system at the same cost, or even lower, that the traditional silicon FET system.”

“We’ve reduced the overall bill of materials in our systems and we’re getting a lot of excitement as we now have a small 45 W adapter in a 25 W adapter housing,” he adds.

Crucially, this reduction in size paves the way to the universal power adapter that the mobile communications industry craves for its smartphones, notebooks, iPads and more. And according to Tyndall, Dialog customers are more than ready for GaN.

While he reckons initial concerns centred on device reliability, times have changed and industry has moved on. “We’re really are beyond these issues now,” he asserts.

Indeed, as Richard Eden, senior analyst at IHS Markit, highlights, Dialog is one of many moving towards GaN. “It’s a safe bet that all silicon semiconductor suppliers are developing a strategy for GaN,” he points out.

“During the last five years, start-ups such as Efficient Power Conversion, Transphorm and GaN Systems have successfully developed GaN products for the commercial market,” he adds. “And more recently, larger silicon semiconductor companies, such as Infineon Technologies, Texas Instruments and Panasonic, have announced GaN developments.”

For example, in March last year, Texas Instruments launched a 80 V GaN FET power-stage comprising a high-frequency driver and two GaN FETs in a half-bridge configuration.

For Eden, these developments and Dialog’s latest announcement are clear signals that GaN is now joining mainstream markets and is no longer considered to be a ‘clever research lab experiment’. “And with foundry companies like TSMC now offering a GaN-on-silicon transistor process technology to clients, perhaps we will see more suppliers offering similar products using their own driver IC [technology],” he says.

Right now, Dialog is testing its GaN-based power IC with ‘beta’ customers and is set to sample during Q4, this financial year. The company’s next move will be to ramp up production to volume levels, which Tyndall believes will take place by the middle of next year.

“We’re strong in the fast-charging, mobile, power adapter market with around a 70 percent share and we’re also entrenched with the top ten vendors in the China smartphone market,” he says.

The Development and Strategy President doesn’t foresee any supply chain issues – manufacturing uses standard CMOS equipment – but highlights: “We do need to be careful with back-end packaging and have chosen experienced vendors here.”

“We also intend to use high volume, standard, device testers, which fits with our desire to manufacture hundreds of millions of units without using niche [processes],” he adds.

Then, with wireless device markets addressed, the company intends to turn to PC markets with a 100 W power adapter, and eventually target server markets.

Looking beyond high-volume consumer markets, Dialog isn’t chasing industrial applications such as PV inverters, turbines and electric vehicles, although according to Tyndall, the company would ‘never say never’.

However, the company has settled on GaN-on-silicon as its future technology of choice, over SiC, which Tyndall puts down to lower costs, better monolithic integration and higher volume production.“We are looking to drive production volumes now,” he concludes. “There is a chicken and egg element here as we need to drive volumes to drive the next level of fab investment that will bring us to a higher wafer size. But I would hope to move to eight inch wafers in the next two to three years.”

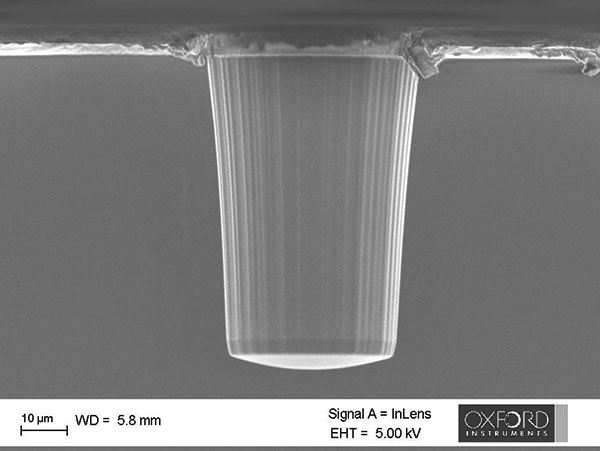

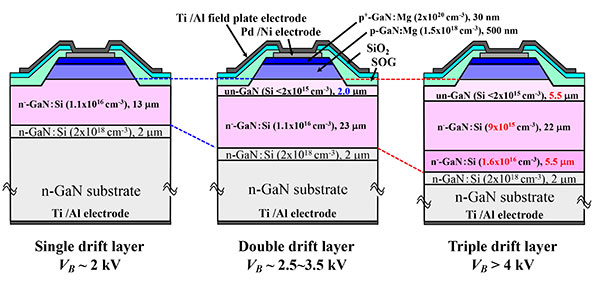

For the RF industry, smooth and fast SiC backside via etching is crucial to high performance devices.

As GaN-on-SiC RF devices reach market, Oxford Instruments has delivered a new via etch process to ease fabrication, reports Rebecca Pool.

Just last month, Oxford Instruments revealed its latest SiC via etch process to be added to the PlasmaPro100 Polaris etch system.

Already designed to deliver fast etch rates on GaN, sapphire, SiC wafers and more, the single-wafer etch system now promises a faster, smooth via etch through SiC at a time when the wide bandgap material is proving crucial to the development of GaN-on-SiC RF devices.

“The system was released a couple of years ago, but this SiC via process is new,” says Mark Dineen, Optoelectronics Product Manager at Oxford Instruments Plasma Technology.

“We saw a market need for this, developed it and believe now is the time to release it,” he adds. “GaN-on-SiC is definitely a growing market and we want to be part of that.”

But the road to the smooth SiC via hasn’t been straightforward. SiC backside via etching is crucial to form a contact with electrodes during the fabrication of GaN-on-SiC transistors. However, SiC is a tough material to etch and researchers worldwide have grappled with how best to handle a substrate with a hardness close to that of diamond. Oxford Instruments now believes it has the answer.

As part of the latest etch process, SiC is mounted onto a sapphire carrier using wax, ready to plasma-etch the via some 100 µm through the wafer. As Dineen highlights, this wafer thickness demands a fast, aggressive etch, and as such, process engineers at Oxford Instruments have opted for a 1.2 µm per minute etch rate. “We need smooth sidewalls in the via, and if we went faster, we would produce jagged features within the via which leads to localised heating and reduces device lifetime,” he says. “But any slower, then throughput is just too slow and the [system] cost of ownership is too high.”

A key issue that many researchers have encountered while optimising SiC substrate via etch processes is the formation of so-called pillars in the via hole, which impede metallisation. These unusual structures form on the end of micro-pipes – hollow tubes that are created during SiC growth – and are exposed after the relatively thick SiC wafer is chemically thinned to around 100 µm for the via etch.

Myriad researchers have experimented with pre-etch clean and etch processes to avoid pillar formation. But according to Dineen, Oxford Instruments has countered this problem by introducing a 30 second etch to the process. It smoothly removes the top layer and accompanying defects to produce a clean surface prior to the main SiC via etch.

So, with defects removed, the relatively fast, aggressive plasma-etch swiftly produces a smooth, slightly sloped via, ready for post-etch metallisation. However, this process also generates heat around the wafer and sapphire carrier, spelling bad news for the all-important wax attachments that have an upper temperature limit of 150°C.

To maintain wax integrity, the wafer is electrostatically clamped to a lower electrode, which contains liquid cooling channels to transfer heat away through the electrode. As Dineen highlights, electrostatic clamping is widely used in the silicon industry, but during this SiC via etch process, a non-conducting sapphire substrate is being handled that will adhere to the clamp at the end of the etch.

Given this, the company transferred a technology to the system that was developed as part of its past GaN-on-sapphire LED research.

“We had developed an electrostatic clamp that could efficiently clamp bare sapphire as part of our patterned sapphire substrate process,” explains Dineen. “Thanks to the control method we developed, here we have excellent cooling in our system and the wafers are handled very smoothly.”

While the company

capitalises on lessons learned from LED process development, does it also

expect the up and coming GaN-on-SiC RF device market to provide the same

potential for growth? Dineen points to the likes of Wolfspeed, Panasonic and

Fujitsu, all developing GaN-on-SiC RF devices, and also highlights how

China-based manufacturers are now penetrating the market.

Yet, an LED-type boom isn’t expected. As Dineen puts it: “We do see a lot of growth in this market, but I don’t think we will see anything quite as big as the LED market.”

“This is an interesting market, it’s growing and SiC also has potential in power applications,” he adds. “This all ties in with our expertise around III-V materials in these niche production markets.”

And what about rival GaN-on-silicon devices? For example, this time last year, MACOM celebrated shipping more than one million GaN-on-silicon

RF devices while claiming a 100 W transistor with comparable performance at a cheaper cost. And more recently, imec has launched a GaN-on-silicon research programme to produce 8 inch wafers.

“Processing costs will be a barrier for GaN-on-SiC devices but its performance is driving demand,” he says. “If you measure GaN-on-SiC device quality versus cost, it is a strong choice compared to GaN-on-silicon. GaN-on-silicon will have a place for sure, although there are limitations on performance.”

Still, Oxford Instrument’s PlasmaPro100 Polaris etch system can handle wafer sizes up to 8 inches. And as Dineen concludes: “I’m not sure whether or not SiC wafers will reach that diameter, but GaN-on-silicon wafers are getting there, so we can etch a GaN recess into these wafers if needed.”

Richard Stevenson talks to IHS Markit analyst Richard Eden about the big events in the SiC industry, such as Infineon’s plans to purchase Wolfspeed, X-Fab’s establishing of a 150 mm SiC foundry, and the acquisition of Fairchild by ON Semiconductor.

Q: Within the SiC industry, this year will be remembered for the buying of Wolfspeed, essentially Cree’s SiC division, by European electronics giant Infineon. As the first to bring the SiC diode to market, Infineon is already a leader in this technology. So what is the rationale behind its aim to buy Wolfspeed in a cash deal worth $850 million?

A: There are two main reasons. Firstly, although Infineon is a big player in the SiC diode market, it’s way behind Cree and others when it comes to the potentially larger SiC MOSFET market. After several years of pushing its SiC JFETs, it only finally launched the SiC MOSFET earlier this year. So it’s four or five years behind the curve for SiC MOSFETs. By acquiring Wolfspeed, it will immediately get a product range that is established, which has gone through several design optimisations, and is already in mass production. So it can get market share.

The other key element in the Wolfspeed acquisition is that Infineon obtains the world-leading substrate wafer production capacity, and its know-how. It gives Infineon in-house control of the essential resource to make its own wafers, and it saves costs from having to buy wafers from a commercial source.

Q: Will this acquisition make Europe the leader of SiC power devices, given that STMicroelectronics also produces SiC diodes and MOSFETs based on this material?

A: To some extent, yes. Control of Wolfspeed’s product development will shift across the Atlantic to Europe. But I don’t think that they’ll move the actual production or design engineering for a long time yet.

Q: How does the sale of Wolfspeed impact the US? Is General Electric now the local leader of this technology?

A: I think General Electric is probably one of the most well-known American companies, but there are plenty of other American companies that are active in the SiC market, maybe some smaller ones. GeneSiC, Global Power Technology Group, Microsemi, Northrop Grumman, Raytheon and United Silicon Carbide are all deeply involved, and you have new companies like Monolith Semiconductor.

Q: In the Asia-Pacific region, is Rohm still the leading manufacturer of SiC power devices?

A: Yes, I think so. But Rohm is unusual [in this region], in that it sells all of its SiC products commercially. It has no captive, internal market making end-equipment, whereas some of the other Japanese and Asian companies that produce SiC products do so for internal use in their finished end equipment. Selling [the SiC products] is a side line. For those companies, examples would be Denso, Fuji Electric, Hitachi, Mitsubishi Electric, Toshiba, Toyota and so on.

Q: ON Semiconductor has just bought Fairchild for $2.4 billion. Back in 2011, Fairchild equipped itself with SiC BJT technology by buying TranSiC. Do you think ON Semiconductor will continue to promote this technology?

A: No, I don’t, because Fairchild stopped developing the SiC-based BJTs in around 2014. However, ON Semiconductor will continue to invest in wide bandgap materials, maintaining both companies’ strategies. Fairchild had already announced SiC diodes, developed by the former TranSiC team in Sweden, with its SiC MOSFETs coming soon: this work will continue unchanged. ON Semi was working with GaN, in partnership with Transphorm, as well as an in-house GaN project: these will also continue.

Q: Does the acquisition of SiC start-ups such as SemiSouth and TranSiC, and the multi-million dollar acquisitions on Wolfspeed and Fairchild, suggest that there is no longer a place for the little guy in the SiC power industry?

A: No, there are still several little guys left in the SiC industry. For example, AnvilSemiconductors in the UK, Ascatron in Sweden, and then a host of companies in America – small guys: BASiC 3C, GeneSiC, Global Power Technology Group, Monolith Semiconductor, and United Silicon Carbide.

They may have strategies to be bought eventually, but they all want to be big companies. They are all ambitious.

Q: Have all the world’s leading silicon power device makers now got SiC technology, either through acquisition or in-house development?

A: I’d say no, but I would say that the ones who are not involved in SiC are probably working on GaN. The likes of Alpha & Omega Semiconductor, NXP, Panasonic and Texas Instruments are only involved in GaN.

Even Vishay – which has has historically bought up companies involved in older, established technologies – is developing a 650 V discrete, normally-off GaN power transistor in-house. This has not been formerly or officially announced, but this news was quietly displayed on the Vishay booth at Electronica. Expect plans to be announced in Q1 ‘17.

Q: Do these electronics giants see SiC power devices as complementary to their silicon products, or as eventual successors?

A: In general, it’s a mix of both. Overall, they are hedging their bets, so they have an income stream in future, whichever way the market moves. In the short term it will be complementary, but in the long term it may be a successor – so they have got to be in that market, or their sales will just dry up.

Q: X-fab is developing a 6-inch SiC line that will enable companies to outsource their chip production. Do you expect this move to have a big impact on the industry?

A: I think it may have an impact, but I don’t know how big it will be. It certainly enables the prospect of fabless SiC companies to spring up. When I spoke to X-fab last, they said that they had already got about five signed-up clients for the SiC foundry service. It’s probably increased a bit since then.

Q: How would you describe the level of maturity of the SiC diode and transistor today? And what flavour of transistor is most popular?

A: I’d say that for SiC diodes, and to some extent SiC transistors, you don’t hear about the solving of performance or reliability problems anything like as much as you did four or five years ago. So it’s definitely maturing, but there is still some room to improve further.

In terms of the flavour of transistor, SiC MOSFETs are definitely the transistor of choice of end customers, even though there are benefits to both SiC JFETs and SiC BJTs.

The market choice is driven by perception, not by the laws of physics. Engineers have been designing with normally off silicon MOSFETs for about 30 years, so they want a SiC alternative that is driven in a similar way; a technology that they are comfortable with.

Q: Is there any appetite for the commercialisation of other SiC power devices, such as a thyristor?

A: Not that I’ve seen.

Q: How will Infineon’s purchase of Wolfspeed impact the SiC substrate market?

A: As Infineon will get full control of its SiC substrate manufacturing process, it can optimise the characteristic it wants for its products. It can allocate production to suit its needs as well.

I believe that Cree was the biggest supplier of wafers in the SiC power market, so Infineon may be able to control which of its competitors it supplies – if any. So I think the likes of Dow Corning, II-VI Incorporated and SiCrystal will be rubbing their hands, because the market-leading competitor may be about to exit the market.

Q: Dow Corning has strived to take a bigger share of the SiC substrate market. Has it made much ground so far, or does Wolfspeed currently dominate the substrate market?

A: I think Wolfspeed, or Cree, has still been the dominant supplier in the market up until now. I know Dow Corning has tried hard, and has caught Cree heavily, but I don’t think they have overtaken them.

Q: Is the manufacture of SiC chips shifting to larger substrates.

A: Yes, but slowly. The market is still using 100 mm diameter wafers at the moment, but it is actively transitioning to 150 mm wafers. In my most recent report, published in February this year, I estimated the use of 150 mm wafers would overtake 100 mm by 2018.

Q: Are there still issues over substrate quality, such as micropipes and Basal plane dislocations, or are these now a thing of the past?

A: I think they are gradually being solved, but they are still a problem for the lower price wafer suppliers. So, without wanting to point the finger, there are several Chinese suppliers that have come on to the market with very cheap quotes. These [imperfections] are real problems for them, compared to the high-quality, more Western suppliers. You get what you pay for.

Q: What is the SiC market worth today? And what proportion of it is for diodes and for transistors?

A: In my most recent report I estimated that the total SiC power market was worth about $200 million in 2015. Of that, SiC diodes comprised about 60 percent, SiC transistors just under 20 percent – and that was dominated by SiC MOSFETs – and SiC power modules comprised just over 20 percent. That’s mainly in hybrid SiC modules, so modules which combine silicon transistors with SiC diodes.

Q: What is the typical operating voltage of these products?

A: It depends on the device type. At the moment, most SiC diodes are 650 V rated, most SiC MOSFETs are 1200 V, and power modules are split roughly 50-50 between 1200 V and 1700 V.

Q: Many have argued that GaN HEMTs are suited to providing operation below 1 kV, and probably below 600 V. But recent research has shown that GaN HEMTs can operate well above 1 kV. So is the SiC power device market under a significant threat from GaN?

A: Maybe, but it will take a very long time. It will take several more years for GaN transistors to become very common and successful commercially, and it will take a lot longer to get over 1000 V GaN to be perfected – ten to twenty years, at least.

Q: Where are the majority of SiC power devices deployed today, and how might this change over the remainder of the decade?

A: In 2015, the biggest application was AC-DC power supply units, mainly used in computing or telecommunications. By 2019, I think the largest application will be hybrid and electric vehicles. We are already seeing SiC diodes used inside the DC-DC converters on hybrid vehicles. They have been in production for about one to one-and-a-half years. Hybrid vehicles will become much more common, and the use of SiC in the vehicles will increase too. So you have two growth factors.

Q: Does the SiC power industry have a bright future?

A: Yes, because as long as the use of electric power remains ubiquitous, there will be a demand to use it more efficiently, to flatten off the increased rate of power generation capacity.

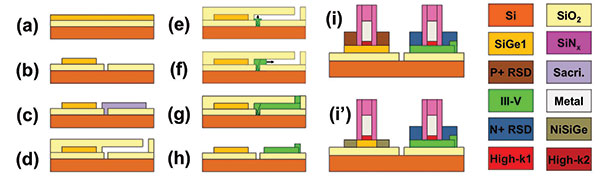

InGaAs MOSFETs, and in general III-V on 300 mm silicon, remain channel materials of interest for future technology application

BY MAO-LIN HUNAG, SHANG-WEN CHANG, CHUN-HSIUNG LIN, HOWARD C.-H. WANG, AND CARLOS H. DIAZ FROM TAIWAN SEMICONDUCTOR MANUFACTURING COMPANY

For the last five decades, the semiconductor industry has successfully benefited from the miniaturization of the MOSFET. The dimensions of transistors have been continuously scaled to meet the requirements for high performance and low power consumption as demanded by application.

Today, the semiconductor industry faces many serious challenges for extending Moore’s law beyond the 10 nm technology node. One of these challenges is to increase the transistor density, while keeping total power density under control through a scaling of the operating voltage. Unfortunately, reducing the operating voltage has unwanted consequences, impacting device performance and impairing switching speed.

One modification that can be made to the MOSFET is to replace the silicon channel with a high-mobility material, such as III-V compounds. This adjustment has the potential to enhance the on-state current, especially at low supply voltages of 0.5 V or less, due to better carrier transport properties at low electric fields. This allows the III-V channel to show great potential in low-power, high-performance applications. However, monolithic integration of III-Vs on large-scale silicon wafers is a significant challenge.

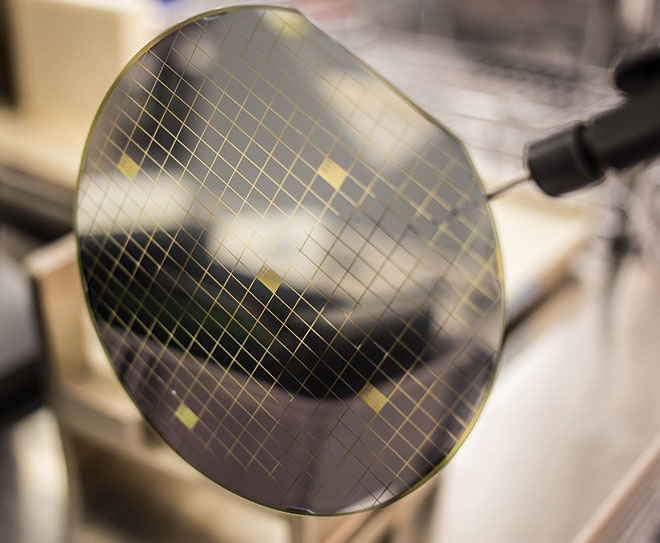

Recently, several approaches have been used to successfully integrate InGaAs with silicon substrates. Examples include: direct epitaxy of III-V on 300 mm silicon, using a strain-relaxed buffer layer or aspect ratio trapping; direct wafer bonding; and template-assisted selective epitaxy. All these approaches are aiding the development of high quality III-V channel transistors on silicon.

At the Taiwan Semiconductor Manufacturing Company, we are playing our part in this pursuit of III-V MOSFETs by fabricating InGaAs transistors on 300 mm silicon substrates for low-voltage logic applications. To do this we have studied the epitaxial growth of the InGaAs channel, the deposition of a high-k gate dielectric, and source/drain contact resistance; and we have evaluated transistor architectures and characteristics.

Figure 1. Transmission electron

microscopy images of III-V epitaxial layers grown on a 300 mm silicon

substrate. (a) III-V/silicon heterostructures including a silicon substrate,

strain-relaxed buffer layers, back barrier, and channel. (b) Top InGaAs channel.

(M.L. Huang et. al. VLSI Symp. Tech. Dig. 2015)

Growth of a high-quality InGaAs epi-layer can be realized on 300 mm, on-axis silicon (100) wafers with a strain-relaxed buffer layer technology. The 8 percent lattice-mismatch between silicon and In0.53Ga0.47As can be accommodated by two metamorphic buffer layers, which minimize crystalline defects at the top InGaAs channel.

Formation of the strain-relaxed structure begins with the growth of a GaAs layer directly on a silicon substrate, followed by an InP buffer layer to gradually relax the misfit strain. Growth of an In0.52Al0.48As back barrier follows, and then an In0.53Ga0.47As channel, which is lattice-matched to InP.

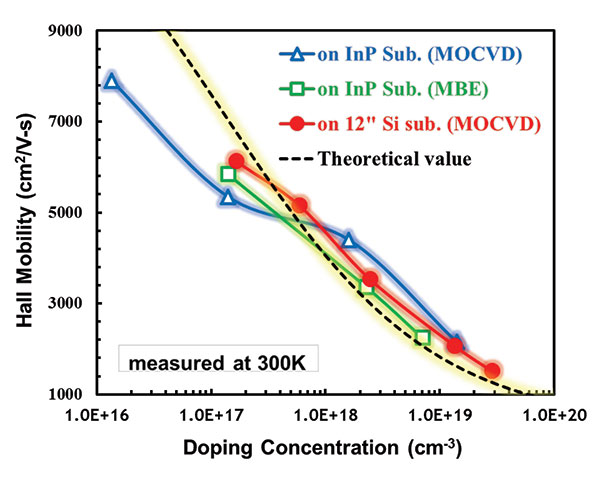

Figure 2. The Hall-mobility of In0.53Ga0.47As

as a function of silicon doping concentration. (M.L. Huang et. al. VLSI Symp.

Tech. Dig. 2015)

All these III-V layers are grown by MOCVD, a technology that delivers high throughput production and has the capability for selective area growth.

The completed epi-structure, grown on 300 mm silicon, is shown in a transmission electron microscopy image, which also reveals the high quality InGaAs channel epitaxial layer (see Figure 1). The mobility of the materials at different silicon doping concentrations is determined by Hall measurements (see Figure 2). They show that the electron mobility in our MOCVD-grown n-type InGaAs-on-silicon is comparable to that of InGaAs layers grown on a lattice-matched InP substrate by MBE or MOCVD.

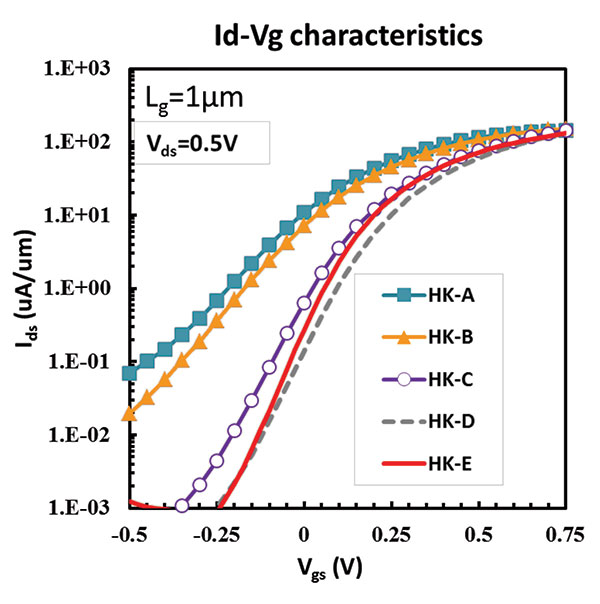

Figure 3. (a) The sub-threshold

characteristics for the planar InGaAs MOSFETs at 0.5 V drain voltage (Vds)

with different high-k

(HK) conditions. HK-E shows the lowest sub-threshold swing value

(88 mV/dec). (M.L. Huang et. al.

VLSI Symp. Tech. Dig. 2015)

The interface between oxides and III-Vs can have a far higher interfacial density of states than that between silicon and its native oxide. This is an issue, because it prevents the gate from providing adequate control over the channel. Significant improvements have been made to the high-k gate dielectric/III-V interfaces during the last decade, thanks to the introduction of atomic layer deposition (ALD) technology. Specifically, ALD precursors have been found to produce a ‘self-clean’ effect, with undesired native oxide located at the III-V surface replaced with high-k metal oxides through ligand exchange and substitution reactions. These take place at the initial stage of the ALD process.

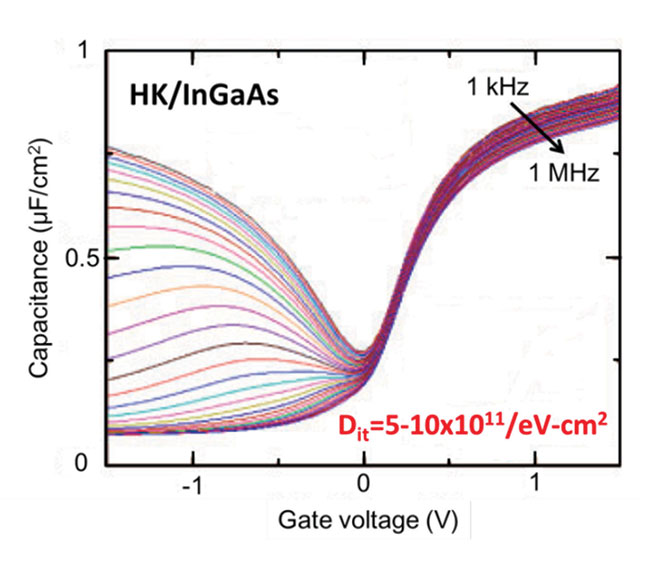

Figure 4. Multi-frequency

capacitance-voltage characteristics for a high-k/InGaAs capacitor.

Realizing a high performance InGaAs MOSFETs requires further optimization of the properties of the interface between the high-k dielectric and the III-V. The sub-threshold characteristics of MOSFETs offer an insight into the gate control capability and interface states. A transistor with a steeper sub-threshold slope or smaller sub-threshold swing – the reciprocal of the sub-threshold slope – is able to exhibit a faster transition between its on and off states.

Different pre-treatment and high-k deposition conditions impact the transfer characteristics of planar ultra-thin body (UTB) InGaAs MOSFETs (see Figure 3). Optimizing the gate stack through the introduction of a high-quality interface between high-k dielectric and InGaAs enables a sub-threshold swing (SS) of 88 mV/decade at a 0.5 V drain voltage. Off-current leakage is less than 1 nA/mm, thanks to the combination of a high-quality, high-k gate stack and low defect density epitaxial layers.

Characterization of the interface traps at the high-k/InGaAs interface is undertaken with multi-frequency capacitance-voltage (C-V) measurements spanning from 1 kHz to 1 MHz (see Figure 4). The resulting plots clearly identify the transitions from accumulation through depletion to inversion. This indicates that the channel carrier is well controlled by gate voltage. Note that the density of interface states for the InGaAs MOS capacitor is 5-10 x 1011 eV-1 cm-2 near the mid-gap.

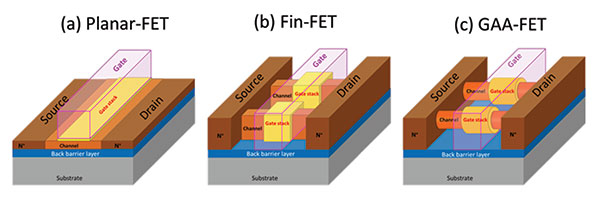

Figure 5. Evolution of field-effect

transistors from planar to Fin- and gate-all-around (GAA) 3D structures.

The resistance at metal-to-source/drain contact also governs transistor performance. High-performance ohmic contacts hinge on a low Schottky barrier height and heavily doped semiconductors at the source and drain regions. Although the contact between a metal and InGaAs has advantages over that between a metal and silicon – the electron effective mass is smaller and the Schottky barrier height is about 0.25 eV lower – the maximum effective doping levels in InGaAs is significantly lower than that in silicon. In InGaAs, it is at most 1 x 10 20 cm-3, compared with 5-10 x 10 20 cm-3 for silicon, and this leads to an inferior contact resistivity in InGaAs; it is typically 7-10 x 10-9 Ω-cm2, while for state-of-the art silicon technology it is 5 x 10-9 Ω-cm2. To achieve the low contact resistivities that are required for sub-10 nm technology, common strategies are to either increase the doping concentration, or to modulate the Schottky barrier height through material selections.

Figure 6 Transfer characteristics and

sub-threshold swing of planar, Fin, and gate-all-around (GAA) InGaAs FETs.

Recently, silicon transistor have evolved from a planar to a three-dimensional (3D) architecture (see Figure 5 for a sketch of a planar-FET, Fin-FET, and gate-all-around FET). The greatest advantage of the Fin- and gate-all-around 3D FETs over the planar FET is the superior short-channel performance owing to the multi-dimensional gate control on the channel. The improved gate control capability allows the further scaling in gate length, leading to improved device performance, such as an increase in on-state current or a reduction in operating voltage. In addition, the 3D architecture enables a higher chip density by pushing the channel to the vertical dimension.

We have compared the transfer characteristics of our in-house InGaAs planar ultra-thin body transistor (channel thickness 10 nm) with our FinFET, and our gate-all-around FET (see Figure 6). Operating at a source drain bias of 0.05 V, the sub-threshold swing for the ultra-thin body FET, FinFET, and gate-all-around FET are 82 mV/decade, 75 mV/decade, and 72 mV/decade, respectively (see Figure 6). The FinFET and gate-all-around FET have a smaller sub-threshold swing than the planar ultra-thin-body FET, thanks to the superior gate control ability over the channel.

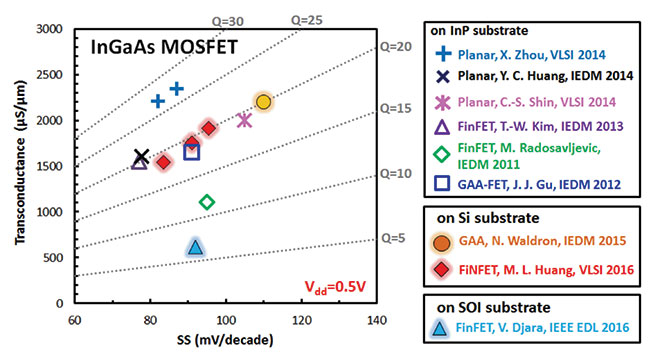

Values for maximum transconductance and sub-threshold swing at a 0.5 V supply voltage have been used to benchmark various planar and 3D InGaAs MOSFETs (see Figure 7). To quantify carrier transport performance and electrostatic integrity, this plot includes a figure of merit Q, which is defined as the transconductance, divided by the sub-threshold swing.

Our InGaAs FinFET produced on 300 mm silicon substrates have a maximum transconductance between 1600 and 1800 mS/mm, a sub-threshold swing of 80-90 mV/decade, and a Q of approximately 20. These values are comparable to the best data obtained from device fabricated on lattice-matched InP substrates.

Figure 7. Benchmarking different

planar and 3D InGaAs MOSFETs by comparing maximum transconductance (gm)

and sub-threshold swing (SS) at a Vdd of 0.5 V. The figure of merit,

Q, is defined as gm/SS.

High quality InGaAs planar MOSFETs and FinFETs have been monolithically integrated on 300 mm silicon wafers. Investigation of MOCVD epitaxial growth, materials properties, high-k gate dielectrics, source/drain contact, device architectures, and device performances suggests that the III-Vs remain a channel material of interest for future high-performance and low-power applications.

Further reading

J. A. del Alamo et. al. IEDM Tech. Dig., p. 24 (2013)

H. Riel et. al. MRS Bulletin 39 668 (2014)

M. L. Huang et. al. VLSI Tech. Dig. , p. T204 (2015)

X. Zhou et. al. IEDM Tech. Dig. p. 773 (2012)

M. L. Huang et. al. Appl. Phys. Lett. 87 252104 (2005)

Y. C. Lin et. al. Appl. Phys. Express 7 041202 (2014)

A. Baraskar et. al. J. Appl. Phys. 114 154516 (2013)

G. Doornbos et. al. IEEE Elec. Dev. Lett. 31 1110 (2010)

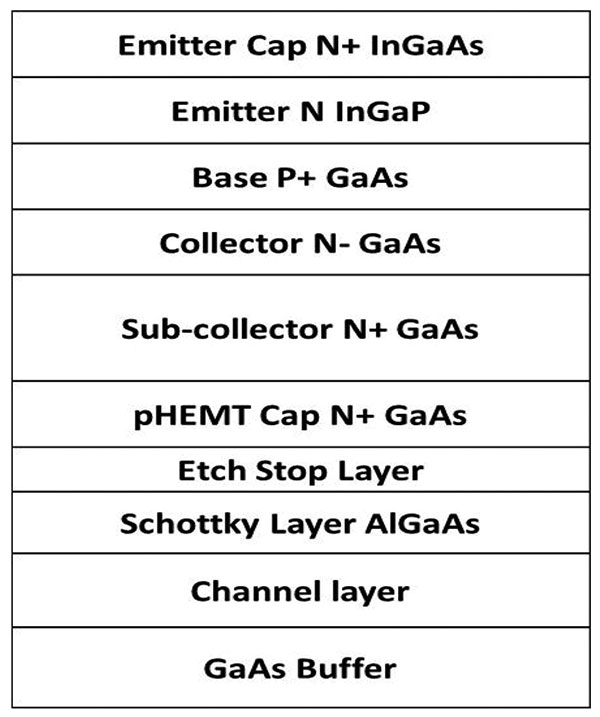

BY JIANG LI, TOM BROWN, MEHRAN JANANI, JIRO YOTA, AND CRISTIAN CISMARU FROM SKYWORKS SOLUTIONS

Smartphones are delivering staggering levels of performance. These marvelous devices can stream videos with great resolution, provide music on the move, take great pictures, and run a vast number of applications.

To accomplish all of this and more, numerous components are crammed together on a very small footprint. So there is great pressure to reduce the real estate of every part, including the power amplifier that enables communication between the handset and the base station.

The dominant transistor technology for the power amplifier is the InGaP/GaAs HBT. It delivers excellent RF performance in a reproducible manner, and it is manufactured in high volumes with a high yield. However, when this chip is deployed in advanced frond-end modules, it fails to meet RF designer’s zero-size requirements. Given this state of affairs, there is a compelling need to integrate the HBT with a FET or a pHEMT on the same chip, because this aids design flexibility and circuit functionality while reducing the module’s size and its overall cost.

One option for forming a single GaAs chip that integrates either the FET or the pHEMT with the HBT is to insert the FET into the emitter section of the HBT. Compared to a HBT-only process, the strengths of the resulting BiFET are a low epitaxial cost, shared process steps, and minimal impact on production cycle time. But there are also weaknesses – as the FET and HBT have shared layers, optimization of the device is hampered; and the BiFET has poor RF isolation.

The alternative approach is to vertically stack the pHEMT underneath the HBT sub-collector. This creates a BiHEMT, a device that features an absence of shared layers between the pHEMT and the HBT. Thanks to this independence, it is possible to individually optimize the thickness and doping within each device. Additional merits are good device RF performance and isolation, resulting from the integration of the pHEMT underneath the HBT sub-collector, so that it is positioned on top of the semi-insulated substrate.

However, all these advantages must be weighed against the big structure topology, which makes the fabrication of the BiHEMT more challenging. It is particularly demanding to develop a sub-micron pHEMT gate process that ensures good RF device performance.

At Skyworks Solutions we have pursued the second of the two options for device integration, successfully developing an advanced BiHEMT technology that stacks the pHEMT underneath the InGaP/GaAs HBT sub-collector. To enable commercial success, we have identified and addressed many fabrication challenges. This has led to high volume, high-yield manufacture of GaAs BiHEMTs on our 6-inch production line.

Forming BiHEMT epiwafers is straightforward, involving the growth of the HBT epitaxial structure on top of the pHEMT. Using MOCVD, HEMT epitaxial layers are deposited on 150 mm semi-isolating GaAs substrates, before the highly doped HBT sub-collector is added, followed by the collector, base, and emitter layers.

We have introduced slight modifications to our HBT layer stack to accommodate the implementation of the pHEMT underneath the HBT. This includes the optimization of the HBT sub-collector thickness, in order to reduce the overall BiHEMT topology. The electric performance of the HBT is not compromised by this adjustment.

Additional changes are to insert etch stop layers for process robustness (see Table 1 for the InGaP/GaAs BiHEMT epitaxial structure), and to take special care during HBT layer growth. These refinements minimize the possibility of degrading pHEMT performance.

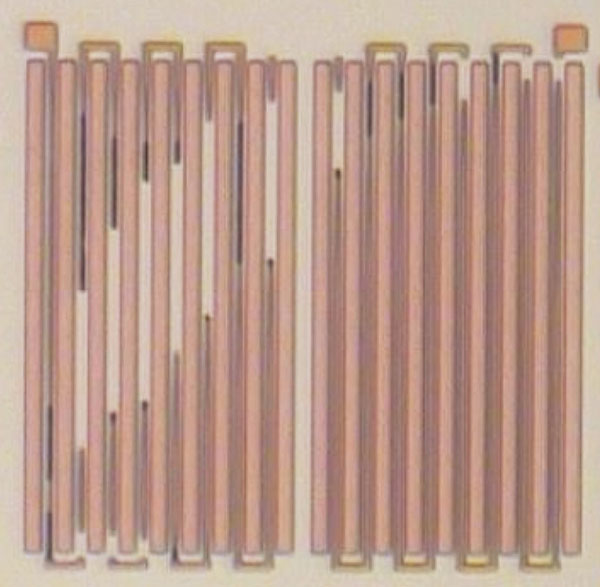

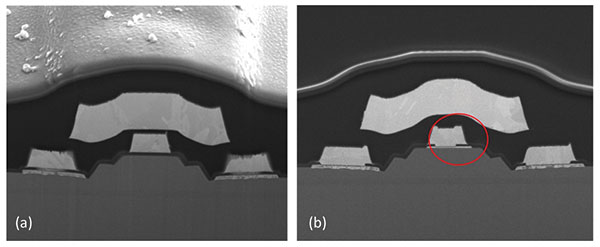

To fabricate the BiHEMT, we use many conventional processes (details are provided in the box “Making a BiHEMT”). Compared to the standard HBT-only process, the additional process challenges for making the BiHEMT are primarily associated with the severe topology created by the combination of active devices, passive components, metal interconnections, and dielectric layers. There is a step height of about 2 mm between the top of the HBT emitter contact and the pHEMT gate layer at the bottom (see Figure 1).

Due to this substantial height difference, it is critical to optimize the photo and etch processes for gate formation, so that the pHEMT gate Schottky layer is opened and etched with good uniformity and process control. These processes need to be reliable and provide a good process margin, to prevent wafer scrap that leads to increased loss and inferior

yield.

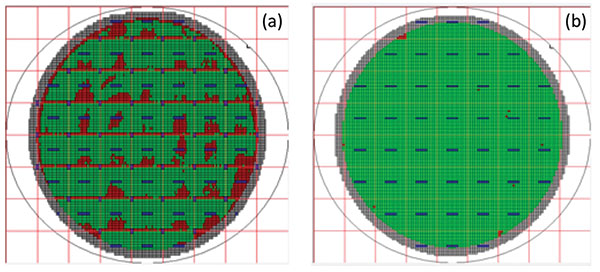

We found that with our BiHEMT production process, the gate metal can be missing after gate lift-off (see Figure 2). Investigations revealed that the missing gate is more common at the reticle corner, due to a combination of a non-optimized gate photo process and non-optimized photo process tool conditions.

To find a solution to the missing gate issue, we introduced a novel method to pre-screen the gate yield. Implementation occurred at the post gate metal formation step, before completion of the process and the process control monitoring test.

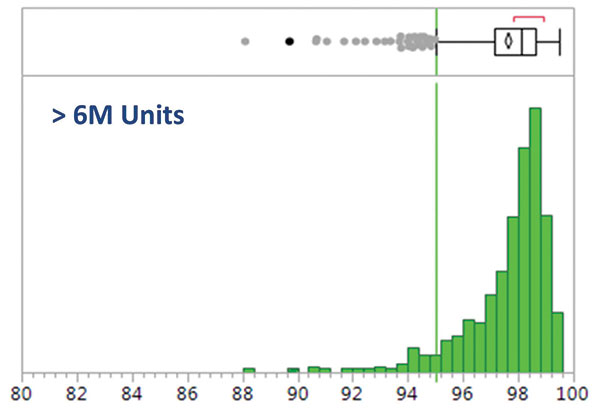

This approach revealed that prior to optimization of gate photolithography, yield loss could be as high as almost 20 percent (See Figure 3 (a)). But gate integrity yields of 99 percent are now possible, by optimizing specific gate photo exposure conditions, equipment tuning and mask modification. These steps eliminate missing gate issue in the reticle corner (see Figure 3 (b)).

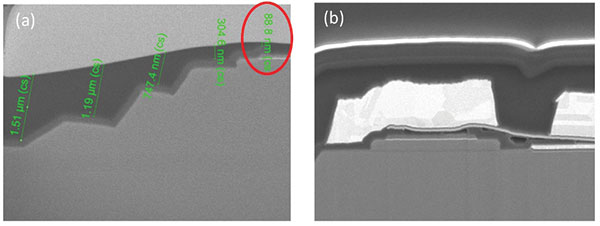

Another stumbling block to establishing a high-volume, high-yield BiHEMT process is the erosion of photoresist in the thin film TaN resistor process. Again, this is a topology-related process.

Formation of the TaN resistors, which are located at the pHEMT level, begins with a photolithography process to pattern the resistors. Dry etching of SiN follows, and then TaN deposition to achieve a clean lift-off (dielectric etch assisted lift-off).

One weakness with this approach is that the photo resist is not perfectly conformal – it is far thinner on the top of the emitter of the HBT than it is at the TaN level (see Figure 4 (a)). Note that on top of the HBT emitter, the resist can be less than 100 nm-thick. As a result, during SiN dry etching for the TaN resistor, the photoresist on top of the HBT emitter can be fully eroded, resulting in TaN metal deposition on top of the HBT emitter. Ultimately, this can prevent a connection between the HBT Metal-1 metal and the emitter metal; and it can result in an emitter short and yield loss (see Figure 4(b)). This yield loss is 3 percent at the final probe test.

We had two options for eliminating the unwanted TaN metal on top of the HBT emitter. One way was to simply increase resist thickness. However, this approach is not that successful, because as the coated resist is not very conformal, increasing its thickness fails to significantly improve resist coverage on top of the emitter. There is even a downside: a thicker resist on the TaN resistor makes it harder to control the critical dimension of this component, and drags down the probe test yield.

A better way is to combine a moderate increase in resist thickness with the selection of a more conformal photo resist, to improve resist coverage. By taking this approach, we have tackled yield loss without impacting electrical performance.

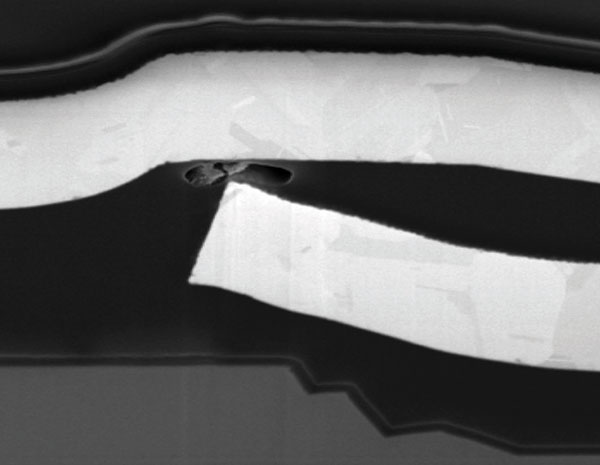

Additional issues that have to be addressed when working with the severe BiHEMT topology occur in backend-of-line process modules. There is the possibility of inter-level metal interconnection shorts and/or poor isolation (an example of this is shown in Figure 5, which reveals shorts between Metal-2 and Metal-3). This type of problem is caused by the severe underlying topology, and is associated with poor material coverage of the photo resist and inter-level dielectric. When the inter-level dielectric is dry etched, the resist – and even the dielectric material – are removed, resulting in shorts between the interconnection metals. Yield loss is exacerbated by the presence of metal stringers. This form of metal short is fatal, and can result in wafer scrap.

We have adopted multiple process steps to solve the inter-level metal short issue. Increasing the photo resist thickness to increase the process margin appears to have merit, but there is a photo resist conformability issue, due to the resist thickness on top of the topology not increasing sufficiently. So we have also optimized the etch ratio of the dielectric-to-photoresist, leading to elimination of the erosion of the protected dielectric area; and we have eradicated metal stringers, by optimizing inter-level photo conditions and metal stacks. Probe yield increases by 3.8 percent, thanks to the removal of inter-level metal shorts (see Figure 6 for a comparison of inter-level dielectric thickness before and after process optimization).

To determine the performance provided by our BiHEMTs, we have undertaken DC and RF testing. The results are encouraging: HBT performance is comparable to that of our HBT-only technology, while the required RF performance for various circuit applications is provided by the pHEMT.

Realizing a high-yield in BiHEMT technology is not simply a matter of optimizing multiple process modules – it also relies critically on testability and test coverage in die-sort. To this end, we have over 60 parameters that are recorded in a DC test for process control monitoring, and over 50 parameters are probed in final test step.

Armed with these results, while implementing our processes that address all the topology-related process issues, we can realize a probe die-sort yield in BiHEMT technology that consistently exceeds 95 percent in our high-volume production line (see Figure 7).

That’s good news for engineers making smartphones, as they can now get what they crave – power amplifiers that combine great performance with a tiny footprint.

The authors wish to thank the contributions provided by Ravi Ramanathan, Mike Sun and Manjeet Singh of Skyworks Solutions.

Production of the BiHEMT begins with the formation of the emitter contact. Photolithography defines the HBT emitter pattern, and emitter contact metal evaporation and lift-off follow. There is no need to employ an emitter alloy, because emitter metal contacts are deposited on a highly doped emitter top layer.

A combination of photolithography and an inductively coupled plasma dry etch, which stops on top of the InGaP HBT emitter layer, defines the emitter mesa. This pair of processes is also used to form the base pedestal. Deposition of a SiN film by PECVD provides protection to the HBT active area, while access to the pHEMT layers comes from wet-etching of the sub-collector layer.

Formation of the HBT base contact involves etching of the SiN film and the InGaP layer, metal deposition and liftoff; the HBT collector contact is defined by deposition of AuGeNi/Au and subsequent rapid thermal processing. The pHEMT source and drain ohmic contacts are formed simultaneously with the HBT collector. Devices, diodes, and other passive components are electrically isolated by helium ion implantation, and the pHEMT gate defined by photolithography, gate recess wet etch, Ti/Pt/Au gate metal deposition and lift-off.

Following formation of the intrinsic HBT and the pHEMT, devices are passivated by PECVD of SiN films. The next steps involve the fabrication of TaN thin film resistors, metal-to-metal SiN capacitors, inductors and metal interconnects. The front side process for the BiHEMT is completed with final passivation, resulting from SiN deposition.

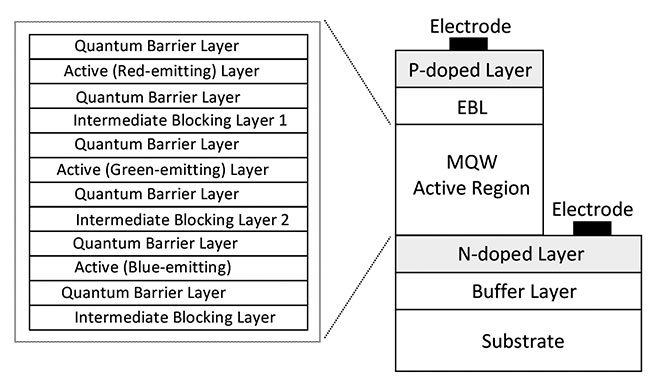

BY JYH-CHIA CHEN, MILTON YEH AND HUSSEIN S. EL-GHOROURY FROM OSTENDO TECHNOLOGY INC.

There are fundamental flaws with both of the leading approaches for producing LED-based white light sources and full-colour displays. If white light is formed from the colour mixing of separate red, green and blue LEDs that are packaged together as one device, the resulting unit must combine red LEDs made from AlGaInP with GaN-based green and blue emitters – and pairing these different types of LED requires special efforts, due to substantial differences in electrical characteristics and material properties. With the main alternative, there are also major downsides. In this case, a blue LED is coated with a yellow phosphor, and white light results from colour mixing. Efficiency is then compromised, due to cascade losses that occur during the blue-to-yellow colour conversion of the photons.

In addition to these drawbacks, both of these approaches are held back by basic issues related to the source, including a high packaging cost, low efficiency, a large device size, low yield and poor reliability. What’s needed, but not commercially available, is a single device that emits all the three primary colours of light.

Progress in this direction has been made by several teams, including Korean electronics giant Samsung. It has produced GaN-based, pyramid-shaped LEDs that emit multiple wavelengths simultaneously to create a white-light source. However, these devices cannot emit all three primary colours independently, so while they are suitable for lighting applications, they can’t be used for displays.

An alternative approach that is pursued by Zetian Mi’s group at McGill University is to produce monolithic red-green-blue LEDs from nanowire structures. Using a three-step selective-area growth technique, these researchers form three sets of nanowire structures on three different regions. Several wafer preparations are used before and after each selective growth. With this approach, each display pixel is capable of producing the three primary colours, which are emitted from three areas, or sub-pixels. This architecture compromises the pixel dimension of the display, and ultimately its resolution.

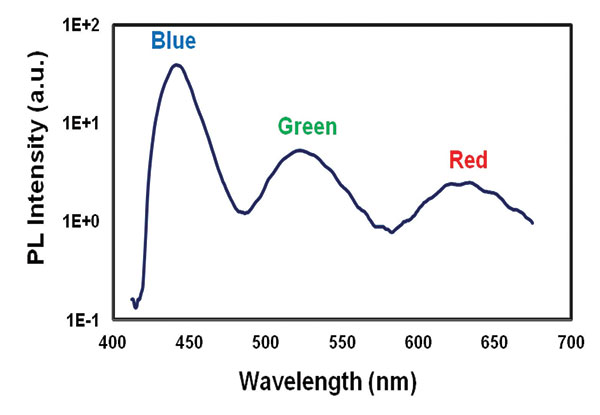

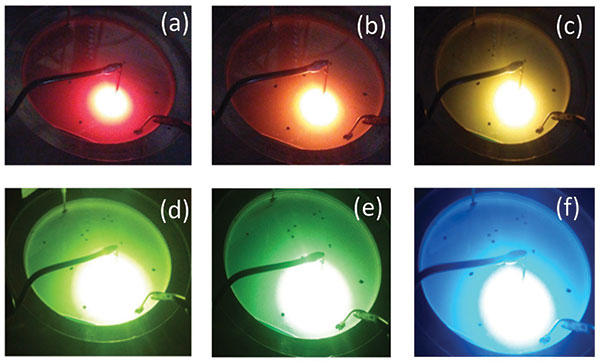

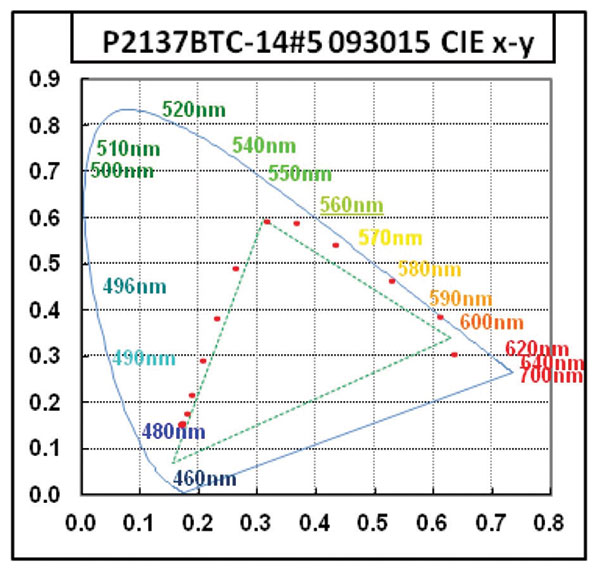

Addressing this limitation is our team from Ostendo Technology Inc. of Carlsbad, CA, which has created the world’s first LED that delivers controllable, tuneable full-colour emission through adjustments in current flow. Note that in addition to the three primary colours, our device produces other colours through colour-mixing techniques.

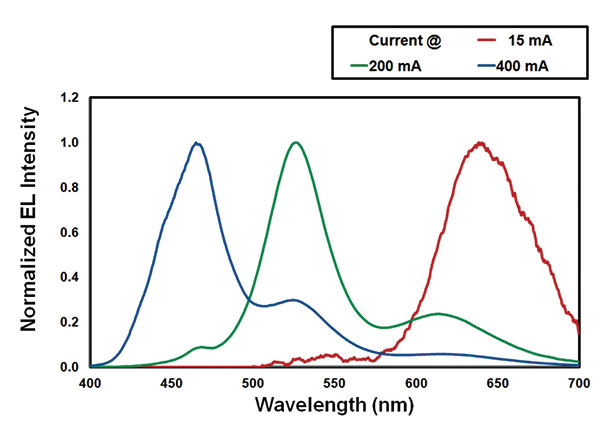

An incredibly important aspect of our technology is that it involves a growth process that is identical to that used for commercial, single-color LEDs – there is no additional pre- or post-growth process. Thanks to this, our technology is practical, and can be scaled to high-volumes and low costs.